(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11) 特許番号

特許第5557795号 (P5557795)

(45) 発行日 平成26年7月23日(2014.7.23)

(24) 登録日 平成26年6月13日(2014.6.13)

(51) Int. Cl. F 1

HO 1 L

27/146

(2006.01)

HO 1 L

27/14

E

HO 4 N

5/374

(2011.01)

HO 4 N

5/335

7 4 O

HO 1 L

31/10

(2006.01)

HO 1 L

31/10

G

請求項の数 12 (全 19 頁)

(21) 出願番号 特願2011-105332 (P2011-105332)

(22) 出願日 平成23年5月10日 (2011.5.10) (65) 公開番号 特開2012-216739 (P2012-216739A)

(43) 公開日

平成24年11月8日 (2012.11.8)

審査請求日

平成25年11月29日 (2013.11.29)

(31) 優先権主張番号 特願2011-70944 (P2011-70944) (32) 優先日 平成23年3月28日 (2011.3.28)

(33) 優先権主張国 日本国(JP)

||(73)特許権者 306037311

富士フイルム株式会社

東京都港区西麻布2丁目26番30号

(74)代理人 100115107

弁理士 高松 猛

||(74)代理人 100151194

弁理士 尾澤 俊之

|(74)代理人 100164758

弁理士 長谷川 博道

(72) 発明者 後藤 崇

神奈川県足柄上郡開成町牛島577番地

富士フイルム株式会社内

審査官 中内 大介

最終頁に続く

## (54) 【発明の名称】 固体撮像素子及び撮像装置

## (57)【特許請求の範囲】

#### 【請求項1】

半導体基板上方に形成された光電変換部と、前記光電変換部で発生した電荷に応じた信号を読みだす前記半導体基板に形成されたMOS型の信号読出し回路とを含む画素がアレイ状に配置された固体撮像素子であって、

前記光電変換部は、前記半導体基板上方に形成され前記画素毎に分割される画素電極と、前記画素電極上方に形成される対向電極と、前記画素電極と前記対向電極との間に形成される光電変換層とを含み、

前記光電変換層で発生した電荷のうちの正孔が前記画素電極に移動するよう、前記信号 読出し回路の電源電圧よりも高いバイアス電圧が前記対向電極には印加され、

前記信号読出し回路は、前記半導体基板内に形成され前記画素電極に移動した正孔が蓄積される電荷蓄積部と、前記電荷蓄積部の電位に応じた信号を出力する出力トランジスタと、前記電荷蓄積部の電位を所定のリセット電位にリセットするためのリセットトランジスタとを含み、

前記電荷蓄積部は、前記画素電極と電気的に接続されるn型不純物領域からなる第一の電荷蓄積領域と、前記第一の電荷蓄積領域の隣に離間して形成されるn型不純物領域からなる第二の電荷蓄積領域と、前記第一の電荷蓄積領域と前記第二の電荷蓄積領域とを、断面ポテンシャルにおいて所定の電位よりも高い電位においては電気的に分離し、前記所定の電位以下の電位においては電気的に接続する分離/接続領域とにより構成され、前記画素電極に移動する正孔の量が所定量までは前記第一の電荷蓄積領域、前記第二の電荷蓄積

領域、及び前記分離 / 接続領域の各々に前記画素電極から移動する正孔を蓄積し、前記画素電極に移動する正孔の量が前記所定量を越えてからは前記第一の電荷蓄積領域のみに前記画素電極から移動する正孔を蓄積するものであり、

前記出力トランジスタは、前記第二の電荷蓄積領域の電位に応じた信号を出力するものである固体撮像素子。

#### 【請求項2】

請求項1記載の固体撮像素子であって、

前記所定の電位は前記リセット電位よりも高い固体撮像素子。

#### 【請求項3】

半導体基板上方に形成された光電変換部と、前記光電変換部で発生した電荷に応じた信号を読みだす前記半導体基板に形成されたMOS型の信号読出し回路とを含む画素がアレイ状に配置された固体撮像素子であって、

前記光電変換部は、前記半導体基板上方に形成され前記画素毎に分割される画素電極と、前記画素電極上方に形成される対向電極と、前記画素電極と前記対向電極との間に形成される光電変換層とを含み、

前記光電変換層で発生した電荷のうちの電子が前記画素電極に移動するよう、前記信号 読出し回路の基準電圧よりも低いバイアス電圧が前記対向電極には印加され、

前記信号読出し回路は、前記半導体基板内に形成され前記画素電極に移動した電子が蓄積される電荷蓄積部と、前記電荷蓄積部の電位に応じた信号を出力する出力トランジスタと、前記電荷蓄積部の電位を所定のリセット電位にリセットするためのリセットトランジスタとを含み、

前記電荷蓄積部は、前記画素電極と電気的に接続されるp型不純物領域からなる第一の電荷蓄積領域と、前記第一の電荷蓄積領域の隣に離間して形成されるp型不純物領域からなる第二の電荷蓄積領域と、前記第一の電荷蓄積領域と前記第二の電荷蓄積領域とを、断面ポテンシャルにおいて所定の電位よりも低い電位においては電気的に分離し、前記所定の電位以上の電位においては電気的に接続する分離 / 接続領域とにより構成され、前記画素電極に移動する電子の量が所定量までは前記第一の電荷蓄積領域、前記第二の電荷蓄積領域、及び前記分離 / 接続領域の各々に前記画素電極から移動する電子を蓄積し、前記画素電極に移動する電子の量が前記所定量を越えてからは前記第一の電荷蓄積領域のみに前記画素電極から移動する電子を蓄積するものであり、

前記出力トランジスタは、前記第二の電荷蓄積領域の電位に応じた信号を出力するものである固体撮像素子。

#### 【請求項4】

請求項3記載の固体撮像素子であって、

前記所定の電位は前記リセット電位よりも低い固体撮像素子。

#### 【請求項5】

請求項1又は2記載の固体撮像素子であって、

前記分離 / 接続領域は、前記第一の電荷蓄積領域と前記第二の電荷蓄積領域の間の前記 半導体基板上方に形成された、固定電圧が印加されるゲート電極によって形成される固体 撮像素子。

# 【請求項6】

請求項3又は4記載の固体撮像素子であって、

前記分離 / 接続領域は、前記第一の電荷蓄積領域と前記第二の電荷蓄積領域の間の前記 半導体基板上方に形成された、固定電圧が印加されるゲート電極によって形成される固体 撮像素子。

# 【請求項7】

請求項5記載の固体撮像素子であって、

前記固定電圧は、前記電源電圧である固体撮像素子。

#### 【請求項8】

請求項6記載の固体撮像素子であって、

10

20

30

前記固定電圧は、前記基準電圧である固体撮像素子。

#### 【請求項9】

請求項1~8のいずれか1項記載の固体撮像素子であって、

前記分離 / 接続領域は、前記半導体基板内の前記第一の電荷蓄積領域と前記第二の電荷蓄積領域との間に形成された不純物領域により構成される固体撮像素子。

#### 【請求項10】

請求項9記載の固体撮像素子であって、

前記不純物領域は、前記第一の電荷蓄積領域及び前記第二の電荷蓄積領域の各々と同一 導電型であり、

前記不純物領域の不純物濃度は、前記第一の電荷蓄積領域及び前記第二の電荷蓄積領域の各々よりも低い固体撮像素子。

10

#### 【請求項11】

請求項10記載の固体撮像素子であって、

前記不純物領域の表面に、前記不純物領域と逆導電型の別の不純物領域を備える固体撮像素子。

#### 【請求項12】

請求項1~11のいずれか1項記載の固体撮像素子を備える撮像装置。

【発明の詳細な説明】

#### 【技術分野】

#### [00001]

20

30

本発明は、固体撮像素子及び撮像装置に関する。

#### 【背景技術】

## [0002]

近年の固体撮像素子の高感度化、多画素化に対応するために、シリコン基板上方に一対の電極とこれらで挟まれた光電変換層を含む光電変換部を有する光電変換層積層型の固体撮像素子が注目されてきている。この固体撮像素子は、光電変換層で発生した電荷を当該一対の電極の一方からシリコン基板に移動させて蓄積し、この蓄積電荷に応じた信号を、シリコン基板に形成した信号読出し回路で読み出す(特許文献 1 参照)。

#### [0003]

特許文献1は、光電変換層積層型の固体撮像素子において、シリコン基板上方の光電変換層で発生した電荷のうちの正孔をシリコン基板内の電荷蓄積部に蓄積し、この電荷蓄積部に蓄積された正孔に応じた信号を信号読出し回路によって読みだす構成を開示している。このような構成により、光電変換層に有機材料を用いた場合でも、感度低下及び分光感度のブロード化を防ぐことが可能となっている。

【先行技術文献】

#### 【特許文献】

## [0004]

【特許文献 1 】特開 2 0 0 7 - 8 1 1 3 7 号公報

#### 【発明の概要】

【発明が解決しようとする課題】

40

#### [0005]

特許文献1に記載の固体撮像素子は、光電変換層で発生した正孔をシリコン基板内のp型不純物層からなる電荷蓄積部に蓄積し、pチャネルMOSトランジスタによって当該正孔に応じた信号を読みだすものである。正孔に応じた信号の読出し方式としては様々なものが考えられる。例えば、光電変換層で発生した正孔をシリコン基板内のn型不純物層からなる電荷蓄積部に蓄積し、nチャネルMOSトランジスタによって当該正孔に応じた信号を読みだす構成が考えられる。以下、この構成について図14を参照して説明する。

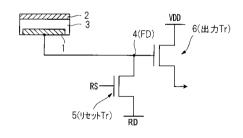

#### [0006]

図14は、光電変換層積層型の固体撮像素子の1画素の読み出し回路の構成例を示す図である。

#### [00007]

画素電極1と、対向電極2と、画素電極1及び対向電極2の間の光電変換層3とにより半導体基板上方の光電変換部が構成される。半導体基板には、画素電極1と電気的に接続されるn型不純物層からなるフローティングディフュージョン4と、フローティングディフュージョン4の電位をリセットするためのnチャネル型のリセットトランジスタ5と、フローティングディフュージョン4の電位に応じた電圧信号を出力するnチャネル型の出力トランジスタ6とが形成される。出力トランジスタ6のゲート電極はフローティングディフュージョン4に接続される。

#### [0008]

図14に示される対向電極2には、読み出し回路に供給される電源電圧VDD(例えば3V)よりも高いバイアス電圧(例えば10V)が印加される。このバイアス電圧によって画素電極1及び対向電極2間に電界が発生する。この電界により、光電変換層3で発生した電荷のうちの正孔が画素電極1に移動し、画素電極1に移動した正孔がフローティングディフュージョン4に蓄積される。フローティングディフュージョン4に正孔が蓄積されると、フローティングディフュージョン4の電位は上昇する。

#### [0009]

光電変換層に過大光が入射した場合、フローティングディフュージョン4の電位は、最大で、対向電極2に印加されるバイアス電圧と同程度まで上昇する。このような過電圧がフローティングディフュージョン4に印加されると、フローティングディフュージョン4が破壊されてしまい、焼き付き等の故障が発生する。

#### [0010]

なお、このような故障は、光電変換層で発生した電子をシリコン基板内の p 型不純物層からなる電荷蓄積部に蓄積し、 p チャネル M O S トランジスタによって当該電子に応じた信号を読みだす構成においても、同様に発生する。

#### [0011]

本発明は、上記事情に鑑みてなされたものであり、過大光が入射された場合でも故障することのない光電変換層積層型の固体撮像素子及びそれを備える撮像装置を提供することを目的とする。

#### 【課題を解決するための手段】

# [0012]

本発明の固体撮像素子は、半導体基板上方に形成された光電変換部と、前記光電変換部 で発生した電荷に応じた信号を読みだす前記半導体基板に形成されたMOS型の信号読出 し回路とを含む画素がアレイ状に配置された固体撮像素子であって、前記光電変換部は、 前記半導体基板上方に形成され前記画素毎に分割される画素電極と、前記画素電極上方に 形成される対向電極と、前記画素電極と前記対向電極との間に形成される光電変換層とを 含み、前記光電変換層で発生した電荷のうちの正孔が前記画素電極に移動するよう、前記 信号読出し回路の電源電圧よりも高いバイアス電圧が前記対向電極には印加され、前記信 号読出し回路は、前記半導体基板内に形成され前記画素電極に移動した正孔が蓄積される 電荷蓄積部と、前記電荷蓄積部の電位に応じた信号を出力する出力トランジスタと、前記 電荷蓄積部の電位を所定のリセット電位にリセットするためのリセットトランジスタとを 含み、前記電荷蓄積部は、前記画素電極と電気的に接続されるn型不純物領域からなる第 一の電荷蓄積領域と、前記第一の電荷蓄積領域の隣に離間して形成されるn型不純物領域 からなる第二の電荷蓄積領域と、前記第一の電荷蓄積領域と前記第二の電荷蓄積領域とを 、断面ポテンシャルにおいて所定の電位よりも高い電位においては電気的に分離し、前記 所定の電位以下の電位においては電気的に接続する分離 / 接続領域とにより構成され、前 記画素電極に移動する正孔の量が所定量までは前記第一の電荷蓄積領域、前記第二の電荷 蓄積領域、及び前記分離/接続領域の各々に前記画素電極から移動する正孔を蓄積し、前 記画素電極に移動する正孔の量が前記所定量を越えてからは前記第一の電荷蓄積領域のみ に前記画素電極から移動する正孔を蓄積するものであり、前記出力トランジスタは、前記 第二の電荷蓄積領域の電位に応じた信号を出力するものである。

10

20

30

40

#### [0013]

本発明の固体撮像素子は、半導体基板上方に形成された光電変換部と、前記光電変換部 で発生した電荷に応じた信号を読みだす前記半導体基板に形成されたMOS型の信号読出 し回路とを含む画素がアレイ状に配置された固体撮像素子であって、前記光電変換部は、 前記半導体基板上方に形成され前記画素毎に分割される画素電極と、前記画素電極上方に 形成される対向電極と、前記画素電極と前記対向電極との間に形成される光電変換層とを 含み、前記光電変換層で発生した電荷のうちの電子が前記画素電極に移動するよう、前記 信号読出し回路の基準電圧よりも低いバイアス電圧が前記対向電極には印加され、前記信 号読出し回路は、前記半導体基板内に形成され前記画素電極に移動した電子が蓄積される 電荷蓄積部と、前記電荷蓄積部の電位に応じた信号を出力する出力トランジスタと、前記 電荷蓄積部の電位を所定のリセット電位にリセットするためのリセットトランジスタとを 含み、前記電荷蓄積部は、前記画素電極と電気的に接続されるp型不純物領域からなる第 一の電荷蓄積領域と、前記第一の電荷蓄積領域の隣に離間して形成されるp型不純物領域 からなる第二の電荷蓄積領域と、前記第一の電荷蓄積領域と前記第二の電荷蓄積領域とを 断面ポテンシャルにおいて所定の電位よりも低い電位においては電気的に分離し、前記 所定の電位以上の電位においては電気的に接続する分離/接続領域とにより構成され、前 記画素電極に移動する電子の量が所定量までは前記第一の電荷蓄積領域、前記第二の電荷 蓄積領域、及び前記分離/接続領域の各々に前記画素電極から移動する電子を蓄積し、前 記画素電極に移動する電子の量が前記所定量を越えてからは前記第一の電荷蓄積領域のみ に前記画素電極から移動する電子を蓄積するものであり、前記出力トランジスタは、前記 第二の電荷蓄積領域の電位に応じた信号を出力するものである。

[0014]

本発明の撮像装置は、前記固体撮像素子を備えるものである。

【発明の効果】

[0015]

本発明によれば、過大光が入射された場合でも故障することのない光電変換層積層型の固体撮像素子及びそれを備える撮像装置を提供することができる。

【図面の簡単な説明】

[0016]

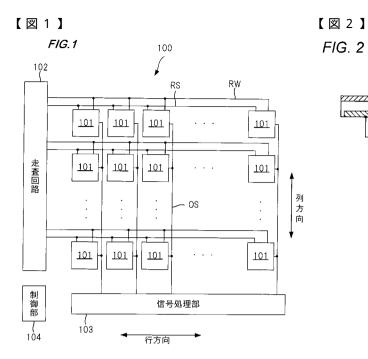

【図1】本発明の一実施形態を説明するための光電変換層積層型の固体撮像素子100の 平面模式図

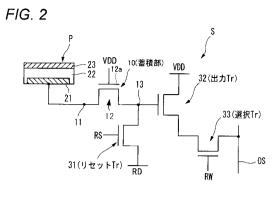

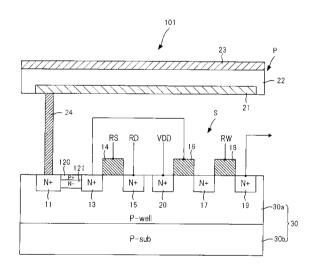

【図2】図1に示される固体撮像素子100における画素101の概略構成を模式的に示 ま図

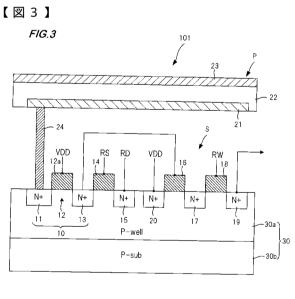

【図3】図1に示される固体撮像素子100における画素101の概略構成を示す断面模式図

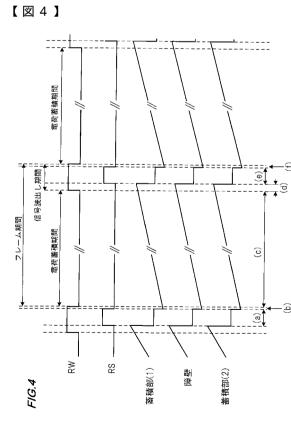

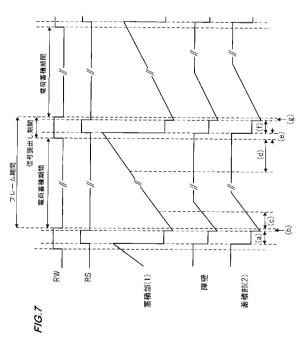

【図4】図1に示される固体撮像素子100の1画素行分の撮像動作(入射光量が少ない場合)を説明するためのタイミングチャート

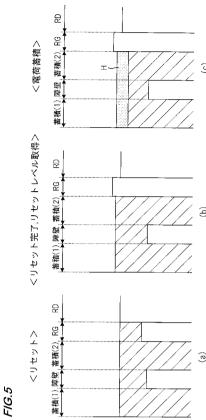

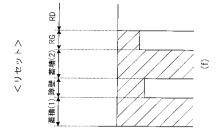

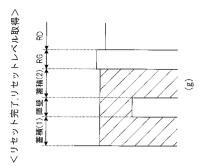

【図5】図1に示される固体撮像素子100の1画素行分の撮像動作(入射光量が少ない場合)時の半導体基板30内のポテンシャル遷移を示す図

【図6】図1に示される固体撮像素子100の1画素行分の撮像動作(入射光量が少ない場合)時の半導体基板30内のポテンシャル遷移を示す図

【図7】図1に示される固体撮像素子100の1画素行分の撮像動作(入射光量が多い場合)を説明するためのタイミングチャート

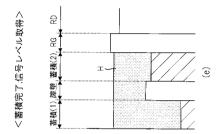

【図8】図1に示される固体撮像素子100の1画素行分の撮像動作(入射光量が多い場合)時の半導体基板30内のポテンシャル遷移を示す図

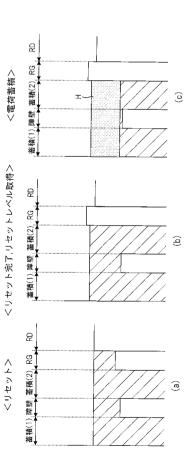

【図9】図1に示される固体撮像素子100の1画素行分の撮像動作(入射光量が多い場合)時の半導体基板30内のポテンシャル遷移を示す図

【図10】図1に示される固体撮像素子100の1画素行分の撮像動作(入射光量が多い場合)時の半導体基板30内のポテンシャル遷移を示す図

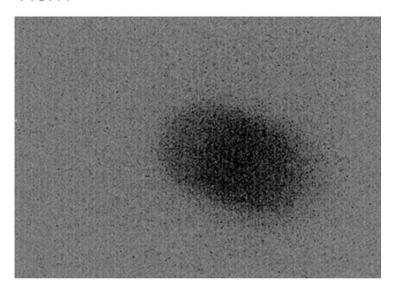

【図11】図14に示される構成の画素をアレイ状に配置した固体撮像素子を用いて太陽

10

20

30

40

を撮像した後に、この固体撮像素子を遮光して暗時撮像を行って得られた画像を示す図 【図12】図2に示される構成の画素をアレイ状に配置した固体撮像素子を用いて太陽を 撮像した後に、この固体撮像素子を遮光して暗時撮像を行って得られた画像を示す図

【図13】図1に示される固体撮像素子100の変形例を示す図

【図14】光電変換層積層型の固体撮像素子の1画素の読み出し回路の構成例を示す図 【発明を実施するための形態】

#### [0017]

以下、本発明の実施形態について図面を参照して説明する。

#### [0018]

図1は、本発明の一実施形態を説明するための光電変換層積層型の固体撮像素子100 の平面模式図である。この固体撮像素子100は、デジタルカメラ及びデジタルビデオカメラ等の撮像装置、電子内視鏡及びカメラ付携帯電話機等に搭載される撮像モジュール、 等に搭載して用いられる。

## [0019]

図1に示す固体撮像素子100は、行方向とこれに直交する列方向に二次元アレイ状(図1の例では正方格子状)に配列された複数の画素101と、画素101からの信号の読み出しを制御するための走査回路102と、各画素101から出力される信号を処理する信号処理部103と、固体撮像素子100を統括制御する制御部104とを備える。

#### [0020]

走査回路102は、リセット線RS及び行選択線RWの各々を介して、各画素101に含まれる後述する信号読出し回路に接続される。信号処理部103は、出力信号線OSを介して各画素101と接続される。

# [0021]

図2は、図1に示される固体撮像素子100における画素101の概略構成を模式的に示す図である。図3は、図1に示される固体撮像素子100における画素101の概略構成を示す断面模式図である。

#### [0022]

図2、3に示されるように、画素101は、p型シリコン基板30bとp型シリコン基板30b上に形成されたp型ウェル層30aとからなる半導体基板30上方に形成される光電変換部Pと、半導体基板30に形成されたMOS型の信号読出し回路Sとを備える。

#### [0023]

光電変換部 P は、半導体基板 3 0 上方に形成された画素電極 2 1 と、画素電極 2 1 上方に形成された対向電極 2 3 と、画素電極 2 1 と対向電極 2 3 の間に設けられた光電変換層 2 2 とを含む。

#### [0024]

対向電極23は、その上方から光が入射される。対向電極23は、光電変換層22に光を入射させる必要があるため、入射光に対して透明なITO等の導電性材料で構成される。対向電極23は、全ての画素101で共通の一枚構成であるが、画素101毎に分割してあっても良い。

#### [0025]

画素電極21は、画素101毎に分割された薄膜電極である。画素電極21は、透明又は不透明の導電性材料(ITOやアルミニウムや窒化チタン等)によって構成される。

#### [0026]

光電変換層 2 2 は、入射光のうちの特定の波長域を吸収して、吸収した光量に応じた電荷を発生する有機又は無機の光電変換材料を含んで構成された層である。光電変換層 2 2 と対向電極 2 3 の間、又は、光電変換層 2 2 と画素電極 2 1 の間には、電極から光電変換層 2 2 に電荷が注入されるのを抑制する電荷ブロッキング層が設けられていてもよい。

#### [0027]

光電変換層 2 2 で発生した電荷のうちの正孔が画素電極 2 1 に移動し、電子が対向電極 2 3 に移動するように、対向電極 2 3 にはバイアス電圧が印加される。光電変換層 2 2 が

10

20

30

40

10

20

30

40

50

十分に高い感度を発現するように、バイアス電圧には、信号読み出し回路Sに供給される電圧の最大値である電源電圧VDD(例えば3V)よりも高い電圧(5~20V程度、例えば10V)が用いられる。

#### [0028]

図2に示されるように、信号読出し回路Sは、電荷蓄積部10と、電荷蓄積部10の電位を所定のリセット電位(例えば0.5V)にリセットするためのリセットトランジスタ31と、出力トランジスタ32と、行選択トランジスタ33とを備える。電荷蓄積部10は、第一の電荷蓄積領域11と、第二の電荷蓄積領域13と、第一の電荷蓄積領域11及び第二の電荷蓄積領域13を電位の深い部分では電気的に分離し、電位の浅い部分では電気的に接続する分離/接続領域12とにより構成される。以下、図3を参照して、信号読出し回路Sの詳細を説明する。

[0029]

図3に示されるように、第一の電荷蓄積領域11は、半導体基板30内のp型ウェル層30a表面部に形成されたn型不純物領域により構成される。第一の電荷蓄積領域11は、半導体基板30上に形成された導電性材料からなるコンタクト部24によって画素電極21と電気的に接続される。

[0030]

p型ウェル層30a内において第一の電荷蓄積領域11の隣には、少し離間してn型不 純物領域からなる第二の電荷蓄積領域13が形成されている。

[0031]

第一の電荷蓄積領域11と第二の電荷蓄積領域13との間の半導体基板30上には、図示しない絶縁膜を介して電極12aが形成されている。この電極12aには、固定電圧(図3では、信号読出し回路Sに供給される電源電圧VDD(例えば3V))が印加されるようになっている。この電極12aと重なるp型ウェル層30aの領域が分離/接続領域12である。この分離/接続領域12が、第一の電荷蓄積領域11と第二の電荷蓄積領域13とを、半導体基板30の断面ポテンシャルにおいて所定の電位よりも高い電位においては電気的に分離し、当該所定の電位以下の電位においては電気的に接続する。

[0032]

p型ウェル層30a内において、第二の電荷蓄積領域13の隣には少し離間してn型不純物領域からなる不純物領域15が形成されている。第二の電荷蓄積領域13と不純物領域15との間の半導体基板30上には、図示しない絶縁膜を介してゲート電極14が形成されている。このゲート電極14には、図1に示されるリセット線RSが接続される。不純物領域15には、リセット電圧(例えば0.5V)を供給するための電源が接続される。第二の電荷蓄積領域13と、不純物領域15と、ゲート電極14と、ゲート電極14下方のチャネル領域とにより、図2に示されるリセットトランジスタ31が構成される。

[0033]

ゲート電極14に印加する電圧を制御して、リセットトランジスタ31のチャネル領域の電位を不純物領域15の電位(リセット電位)よりも深くすることで、不純物領域15から電荷蓄積部10に電子を注入して、電荷蓄積部10の電位をリセット電位にリセットすることができる。

[0034]

p型ウェル層30a内において、半導体領域15の隣には少し離間してn型不純物領域からなる不純物領域20が形成されている。p型ウェル層30a内において、不純物領域20の隣には少し離間してn型不純物領域からなる不純物領域17が形成されている。不純物領域20と不純物領域17との間の半導体基板30上には、図示しない絶縁膜を介してゲート電極16が形成されている。不純物領域20と不純物領域17とゲート電極16とゲート電極16下方のチャネル領域とにより、図2に示される出力トランジスタ32が構成される。

[0035]

出力トランジスタ32のゲート電極16は、配線によって第二の電荷蓄積領域13に接

続されている。出力トランジスタ32の不純物領域20には電源電圧VDDを供給する電源が接続される。出力トランジスタ32は、第二の電荷蓄積領域13に蓄積される正孔の量によって決まる第二の電荷蓄積領域13の電位に応じた信号を行選択トランジスタ33に出力する。

## [0036]

p型ウェル層30a内において、不純物領域17の隣には少し離間してn型不純物領域からなる不純物領域19が形成されている。不純物領域17と不純物領域19との間の半導体基板30上には、図示しない絶縁膜を介してゲート電極18が形成されている。不純物領域17と不純物領域19とゲート電極18とゲート電極18下方のチャネル領域とにより、図2に示される行選択トランジスタ33が構成される。

[0037]

行選択トランジスタ33のゲート電極18には図1に示される行選択線RWが接続されている。行選択トランジスタ33の不純物領域19には図1に示される出力信号線OSが接続されている。行選択トランジスタ33がオンすると、出力トランジスタ32から出力された信号が出力信号線OSに出力される。

[0038]

以上のように構成された固体撮像素子100の動作について説明する。固体撮像素子1 00は、電荷蓄積部10に含まれる分離/接続領域12の機能により、入射光の量によって動作が異なる。このため、以下では、入射光の量が少ないときと多いときとに分けて、 固体撮像素子100の動作を説明する。

[0039]

図4は、図1に示される固体撮像素子100の1画素行分の撮像動作(入射光量が少ない場合)を説明するためのタイミングチャートである。図4において、"RW"は、行選択線RWに供給される電圧波形を示している。また、"RS"は、リセット線RSに供給される電圧波形を示している。また、"蓄積部(1)"は、第一の電荷蓄積領域11の電位を示している。また、"障壁"は、分離/接続領域12の電位を示している。また、"蓄積部(2)"は、第二の電荷蓄積領域13の電位を示している。

[0040]

図5及び図6は、図1に示される固体撮像素子100の1画素行分の撮像動作(入射光量が少ない場合)時の半導体基板30内のポテンシャル遷移を示す図である。図5の(a)~(c)と図6の(d)~(f)は、図4に示される(a)~(f)の各期間における半導体基板30内のポテンシャル図である。図5及び図6において、"蓄積(1)"は第一の電荷蓄積領域11のポテンシャルを示している。また、"障壁"は分離/接続領域12のポテンシャルを示している。また、"蓄積(2)"は第二の電荷蓄積領域13のポテンシャルを示している。また、"RG"はリセットトランジスタ31のチャネル領域のポテンシャルを示している。また、"RD"はリセットトランジスタ31の不純物領域15のポテンシャルを示している。また、図5及び図6において、電位は下側に向かうほど高くなっている。

[0041]

固体撮像素子100では、その動作中、図4に示されるように、電荷蓄積部10に電荷を蓄積する電荷蓄積期間と、電荷蓄積期間中に電荷蓄積部10の第二の電荷蓄積領域13に蓄積された電荷に応じた信号を読みだす信号読出し期間とからなるフレーム期間(フレーム)が繰り返される。

[0042]

フレーム期間の開始前になると、走査回路102が、リセットトランジスタ31のゲート電極14に印加する電圧をローレベルからハイレベルに切り替える。リセット中のポテンシャル状態を示しているのが図5(a)である。図5(a)に示されるように、ゲート電極14に印加される電圧がハイレベルになると、リセットトランジスタ31のチャネル領域の電位が、リセットトランジスタ31の不純物領域15の電位(リセット電位)よりも高くなる。この結果、リセットトランジスタ31の不純物領域15から電荷蓄積部10

10

20

30

40

に電子が注入されて、第一の電荷蓄積領域11、分離 / 接続領域12、及び第二の電荷蓄積領域13の全ての電位がリセット電位にリセットされる。

#### [0043]

次に、走査回路102は、リセットトランジスタ31のゲート電極14に印加する電圧をハイレベルからローレベルに切り替えてリセットを完了させる。リセット完了後のポテンシャル状態を示しているのが図5(b)である。図5(b)に示されるように、ゲート電極14に印加される電圧がローレベルになると、リセットトランジスタ31のチャネル領域の電位が、リセットトランジスタ31の不純物領域15の電位よりも浅くなる。このとき、容量結合により、電荷蓄積部10の電位は、図5(a)のときよりも若干浅くなる

[0044]

リセット完了後、行選択トランジスタ33からは、図5(b)の状態における第二の電荷蓄積領域13の電位に応じた信号(リセット信号)が出力信号線OSに出力される。そして、この信号が前のフレームの撮像信号に含まれるリセット信号として信号処理部103に保持される。続いて、信号処理部103にて、前のフレームの撮像信号から当該リセット信号を減算する処理が行われる。リセット信号が出力されると、走査回路102は、行選択トランジスタ33をオフにする。

#### [0045]

分離/接続領域12の電位は電極12aに印加されている電源電圧VDDによって決まっており、図5(a),(b)に示されるように、分離/接続領域12の電位はリセット電位よりも深い位置にある。このため、リセットトランジスタ31の不純物領域15から注入される電子は、分離/接続領域12にも蓄積される。したがって、リセット中及びリセット完了時には、第一の電荷蓄積領域11、分離/接続領域12、及び第二の電荷蓄積領域13の全ての電位が同一電位になる。

[0046]

光電変換部 P には撮像動作中は常時光が当たっているため、図 5 ( b )のリセット完了後に電荷蓄積期間が開始する。この電荷蓄積期間中、光電変換層 2 2 で発生した電荷のうちの正孔は画素電極 2 1 に移動し、画素電極 2 1 から第一の電荷蓄積領域 1 1 に移動する。第一の電荷蓄積領域 1 1、分離 / 接続領域 1 2、及び第二の電荷蓄積領域 1 3 は、電極 1 2 a に印加される電源電圧 V D D によって決まる分離 / 接続領域 1 2 の電位よりも低い電位では導通している。このため、第一の電荷蓄積領域 1 1 に移動した正孔は、分離 / 接続領域 1 2 及び第二の電荷蓄積領域 1 3 にも蓄積される。したがって、第一の電荷蓄積領域 1 1、分離 / 接続領域 1 2、及び第二の電荷蓄積領域 1 3 の全ての電位が均一に上昇する。

[0047]

図5(c)は、電荷蓄積期間中のポテンシャル状態を示す図である。図5(c)に示されるように、第一の電荷蓄積領域11、分離/接続領域12、及び第二の電荷蓄積領域13を併せた領域(電荷蓄積部10)には、入射光に応じた正孔Hが蓄積される。

[0048]

電荷蓄積期間の終了タイミングになると、走査回路102は、行選択トランジスタ33をオンにする(図4(d),図6(d))。行選択トランジスタ33がオンすると、第二の電荷蓄積領域13の電位に応じた信号(撮像信号)が、出力トランジスタ32から行選択トランジスタ33を経由して出力信号線OSに出力される。そして、この撮像信号が信号処理部103にて保持される。

[0049]

次に、走査回路102は、リセットトランジスタ31のゲート電極14に印加する電圧をローレベルからハイレベルに切り替えて、電荷蓄積部10の電位をリセットする。リセット中のポテンシャル状態を示しているのが図6(e)である。走査回路102がリセットトランジスタ31のゲート電極14に印加する電圧をローレベルに戻すと、リセットが完完了される。このときのポテンシャルは図6(f)に示されるようになる。リセットが完

10

20

30

40

了すると、行選択トランジスタ33からは、図6(f)の状態における第二の電荷蓄積領域13の電位に応じた信号(リセット信号)が出力信号線OSに出力される。そして、この信号が信号処理部103に保持される。リセット信号の出力後、走査回路102は、行選択トランジスタ33をオフにする。

#### [0050]

信号処理部103は、図4(d)において保持した撮像信号から、図4(f)において保持したリセット信号を減算することで、ノイズを除去した撮像信号を得る。

#### [0051]

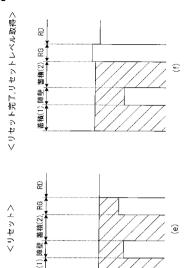

図7は、図1に示される固体撮像素子100の1画素行分の撮像動作(入射光量が多い場合)を説明するためのタイミングチャートである。図7における各表記(RW、RS、蓄積部(1)、障壁、蓄積部(2))は、図4と同じである。

#### [0052]

図8~10は、図1に示される固体撮像素子100の1画素行分の撮像動作(入射光量が多い場合)時の半導体基板30内のポテンシャル遷移を示す図である。図8の(a)~(c)と図9の(d)~(f)と図10の(g)は、図7に示される(a)~(g)の各期間における半導体基板30内のポテンシャル図である。図8~10における各表記(蓄積(1)、障壁、蓄積(2)、RG、RD)は、図5,6と同じである。また、図8~10において、電位は下側に向かうほど高くなっている。

#### [0053]

フレーム期間の開始前になると、走査回路102が、リセットトランジスタ31のゲート電極14に印加する電圧をローレベルからハイレベルに切り替える。リセット中のポテンシャル状態を示しているのが図8(a)である。

# [0054]

次に、走査回路102は、リセットトランジスタ31のゲート電極14に印加する電圧をハイレベルからローレベルに切り替えてリセットを完了させる。リセット完了後のポテンシャル状態を示しているのが図8(b)である。図8(b)に示されるように、リセット完了後は、容量結合により、電荷蓄積部10の電位は、図8(a)のときよりも若干浅くなる。

#### [0055]

リセット完了後、行選択トランジスタ33からは、図8(b)の状態における第二の電荷蓄積領域13の電位に応じた信号(リセット信号)が出力信号線OSに出力される。この信号は前のフレームの撮像信号に含まれるリセット信号として信号処理部103に保持される。そして、信号処理部103にて、前のフレームの撮像信号から当該リセット信号を減算する処理が行われる。リセット信号が出力されると、走査回路102は、行選択トランジスタ33をオフにする。

#### [0056]

光電変換部 P には撮像動作中は常時光が当たっているため、図 8 ( b ) のリセット完了後に電荷蓄積期間が開始する。この電荷蓄積期間中、光電変換層 2 2 で発生した電荷のうちの正孔は画素電極 2 1 に移動し、画素電極 2 1 から第一の電荷蓄積領域 1 1 に移動する。第一の電荷蓄積領域 1 1、分離 / 接続領域 1 2、及び第二の電荷蓄積領域 1 3 は、電極 1 2 a に印加される電源電圧 V D D によって決まる分離 / 接続領域 1 2 の電位以下の電位では導通している。このため、第一の電荷蓄積領域 1 1 に移動した正孔は、分離 / 接続領域 1 2 及び第二の電荷蓄積領域 1 3 にも蓄積される。したがって、第一の電荷蓄積領域 1 1、分離 / 接続領域 1 2、及び第二の電荷蓄積領域 1 3 の全ての電位が均一に上昇する。

# 図8(c)は、画素電極21に移動した正孔の量が閾値以下のときの電荷蓄積期間中のポテンシャル状態を示す図である。図8(c)に示されるように、第一の電荷蓄積領域11、分離/接続領域12、及び第二の電荷蓄積領域13を併せた領域(電荷蓄積部10)

# [0058]

には、入射光に応じた正孔Hが蓄積される。

[0057]

50

20

10

30

10

20

30

40

50

図9(d)に示されるように、画素電極21に正孔が更に移動し、第一の電荷蓄積領域112の電荷蓄積領域13の各々の電位が、電極12aに印加される電源電圧VDDによって決まる分離/接続領域12の電位(以下、障壁電位という)よりも高くなると、第二の電荷蓄積領域13の電位は、障壁電位よりも僅かに高いところで一定となり、それ以上は高くならない。これは、半導体基板30から第二の電荷蓄積領域13に流入する電流と、第二の電荷蓄積領域13から障壁電位を超えて第一の電荷蓄積領域11に流出する電流とが釣り合うためである。

#### [0059]

したがって、第一の電荷蓄積領域11と第二の電荷蓄積領域13の各々の電位が障壁電位よりも高くなると、画素電極21に移動してきた正孔は、第一の電荷蓄積領域11のみに蓄積されるようになる。そして、第一の電荷蓄積領域11の電位だけが最大で対向電極23に印加されるバイアス電圧と同程度まで上昇を続ける。

#### [0060]

電荷蓄積期間の終了タイミングになると、走査回路102は、行選択トランジスタ33をオンにする(図7(e)、図9(e))。行選択トランジスタ33がオンすることにより、第二の電荷蓄積領域13の電位(障壁電位よりも僅かに高い電位)に応じた信号(撮像信号)が、出力トランジスタ32から行選択トランジスタ33を経由して出力信号線OSに出力される。この撮像信号は信号処理部103にて保持される。

#### [0061]

次に、走査回路102は、リセットトランジスタ31のゲート電極14に印加する電圧をローレベルからハイレベルに切り替えて、電荷蓄積部10の電位をリセットする。リセット中のポテンシャル状態を示しているのが図9(f)である。走査回路102がリセットトランジスタ31のゲート電極14に印加する電圧をローレベルに戻すと、リセットが完了される。このときのポテンシャルは図10(g)に示されるようになる。リセットが完了すると、行選択トランジスタ33からは、図10(g)の状態における第二の電荷蓄積領域13の電位に応じた信号(リセット信号)が出力信号線OSに出力される。そして、この信号が信号処理部103に保持される。

#### [0062]

信号処理部103は、図7(e)において保持した撮像信号から、図7(g)において保持したリセット信号を減算することで、ノイズを除去した撮像信号を得る。

#### [0063]

以上のように、固体撮像素子100によれば、電荷蓄積部10に蓄積される正孔の量が 所定量(第二の電荷蓄積領域13の電位が障壁電位と同じになったときに電荷蓄積部10 に蓄積されている正孔量)を超えた場合には、第二の電荷蓄積領域13にそれ以上の正孔 蓄積は行われず、第一の電荷蓄積領域11にのみ正孔蓄積が行われる。このため、固体撮 像素子100に過大光が入射した場合でも、第二の電荷蓄積領域13の電位が、第二の電 荷蓄積領域13が破壊される恐れのある電位(障壁電位よりも僅かに高い値)以上になる のを防ぐことができる。

# [0064]

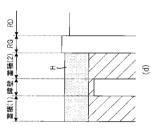

図11は、図14に示される構成の画素をアレイ状に配置した固体撮像素子を用いて太陽を撮像した後に、この固体撮像素子を遮光して暗時撮像を行って得られた画像を示す図である。図12は、図2に示される構成の画素をアレイ状に配置した固体撮像素子を用いて太陽を撮像した後に、この固体撮像素子を遮光して暗時撮像を行って得られた画像を示す図である。

#### [0065]

図11に示される画像には、太陽光が照射された部分に対応する位置に黒い円状の焼き付きが発生したのに対し、図12に示される画像には、いずれの部分にも焼き付きは全く発生しなかった。

#### [0066]

図14に示される構成の画素を持つ固体撮像素子では、非常に強い太陽光によってフロ

10

20

30

40

50

ーティングディフュージョン 4 の電位が急激に上昇し過ぎてフローティングディフュージョン 4 が破壊されてしまい、破壊されたフローティングディフュージョン 4 を含む画素において暗電流(電子)が激増した。図11、12では正孔が信号として発生した場合に画像上で白として表示している。このため、故障により電子が激増したことで、図11に示されるように、故障箇所が黒い円状の焼き付きとして表れたと考えられる。一方、固体撮像素子100によれば、分離 / 接続領域12によって、第二の電荷蓄積領域13の大幅な電位上昇が抑制され、故障が発生するのを防止することができる。このため、図12では、図11に示されるような焼き付きが発生せず、均一な出力が得られたと考えられる。

[0067]

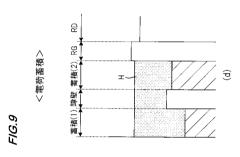

なお、分離 / 接続領域 1 2 は、第一の電荷蓄積領域 1 1 と第二の電荷蓄積領域 1 3 とを、所定の電位(例えば、電源電圧 V D D)よりも深い位置では電気的に分離し、当該所定の電位以下の位置では電気的に接続する機能を持つものであればよい。例えば、図 1 3 に示されるように、半導体基板 3 0 内に形成した不純物領域によっても形成することができる。

[0068]

図13は、図1に示される固体撮像素子100の変形例を示す図である。図13は、図3に対応する図である。

[0069]

図13に示される画素101は、分離/接続領域12及び電極12aを削除し、p型不純物領域120と、n型不純物領域121とを追加した点を除いては、図3に示される画素101と同じ構成である。

[0070]

n型不純物領域121は、第一の電荷蓄積領域11と第二の電荷蓄積領域13の間におけるp型ウェル層30a内に形成されている。n型不純物領域121の不純物濃度は、第一の電荷蓄積領域11及び第二の電荷蓄積領域13の各々の不純物濃度よりも低い。

[0071]

n型不純物領域121の表面にはp型不純物領域120が形成されている。このような構成により、n型不純物領域121が、第一の電荷蓄積領域11と第二の電荷蓄積領域13とを、半導体基板30の断面ポテンシャルにおいて所定の電位よりも高い電位においては電気的に分離し、当該所定の電位以下の電位においては電気的に接続する。つまり、n型不純物領域121が分離/接続領域として機能する。また、p型不純物領域120が設けられていることにより、暗電流低減等の効果も得ることができる。

[0072]

このように、分離 / 接続領域を n 型不純物領域 1 2 1 によって形成する場合には、固定電圧を印加する電極 1 2 a が不要となる。このため、図 3 の画素構成と比較して、配線数を削減することができ、画素を微細化することができる。

[0073]

なお、本明細書では光電変換部Pから取り出してフローティングディフュージョン4に蓄積する電荷を正孔とし、信号読み出し回路SをnチャネルMOSトランジスタで形成する構成とした。しかし、光電変換部Pから取り出す電荷を電子とし、信号読み出し回路SをpチャネルMOSトランジスタで形成する構成としてもよい。この場合、これまで説明してきた固体撮像素子におけるn型とp型が全て逆になる。また、対向電極には信号読み出し回路に供給される全ての電位の基準となる基準電圧GND(例えば0V)よりも低い値(例えば・10V)を印加する。この構成であっても、基板内断面ポテンシャルは図5,6,8・10のようになる。ただし、各図において上に向かうほど電位は高くなる。したがって、上述してきたのと同様の効果が得られる。

[0074]

以上説明してきたように、本明細書には以下の事項が開示されている。

[0075]

開示された固体撮像素子は、半導体基板上方に形成された光電変換部と、前記光電変換

部で発生した電荷に応じた信号を読みだす前記半導体基板に形成されたMOS型の信号読 出し回路とを含む画素がアレイ状に配置された固体撮像素子であって、前記光電変換部は 、前記半導体基板上方に形成され前記画素毎に分割される画素電極と、前記画素電極上方 に形成される対向電極と、前記画素電極と前記対向電極との間に形成される光電変換層と を含み、前記光電変換層で発生した電荷のうちの正孔が前記画素電極に移動するよう、前 記信号読出し回路の電源電圧よりも高いバイアス電圧が前記対向電極には印加され、前記 信号読出し回路は、前記半導体基板内に形成され前記画素電極に移動した正孔が蓄積され る電荷蓄積部と、前記電荷蓄積部の電位に応じた信号を出力する出力トランジスタと、前 記電荷蓄積部の電位を所定のリセット電位にリセットするためのリセットトランジスタと を含み、前記電荷蓄積部は、前記画素電極と電気的に接続されるn型不純物領域からなる 第一の電荷蓄積領域と、前記第一の電荷蓄積領域の隣に離間して形成されるn型不純物領 域からなる第二の電荷蓄積領域と、前記第一の電荷蓄積領域と前記第二の電荷蓄積領域と を、断面ポテンシャルにおいて所定の電位よりも高い電位においては電気的に分離し、前 記所定の電位以下の電位においては電気的に接続する分離/接続領域とにより構成され、 前記画素電極に移動する正孔の量が所定量までは前記第一の電荷蓄積領域、前記第二の電 荷蓄積領域、及び前記分離/接続領域の各々に前記画素電極から移動する正孔を蓄積し、 前記画素電極に移動する正孔の量が前記所定量を越えてからは前記第一の電荷蓄積領域の みに前記画素電極から移動する正孔を蓄積するものであり、前記出力トランジスタは、前 記第二の電荷蓄積領域の電位に応じた信号を出力するものである。

#### [0076]

開示された固体撮像素子は、前記所定の電位は前記リセット電位よりも高いものである

[0077]

開示された固体撮像素子は、半導体基板上方に形成された光電変換部と、前記光電変換 部で発生した電荷に応じた信号を読みだす前記半導体基板に形成されたMOS型の信号読 出し回路とを含む画素がアレイ状に配置された固体撮像素子であって、前記光電変換部は 、前記半導体基板上方に形成され前記画素毎に分割される画素電極と、前記画素電極上方 に形成される対向電極と、前記画素電極と前記対向電極との間に形成される光電変換層と を含み、前記光電変換層で発生した電荷のうちの電子が前記画素電極に移動するよう、前 記信号読出し回路の基準電圧よりも低いバイアス電圧が前記対向電極には印加され、前記 信号読出し回路は、前記半導体基板内に形成され前記画素電極に移動した電子が蓄積され る電荷蓄積部と、前記電荷蓄積部の電位に応じた信号を出力する出力トランジスタと、前 記電荷蓄積部の電位を所定のリセット電位にリセットするためのリセットトランジスタと を含み、前記電荷蓄積部は、前記画素電極と電気的に接続されるp型不純物領域からなる 第一の電荷蓄積領域と、前記第一の電荷蓄積領域の隣に離間して形成されるp型不純物領 域からなる第二の電荷蓄積領域と、前記第一の電荷蓄積領域と前記第二の電荷蓄積領域と を、断面ポテンシャルにおいて所定の電位よりも低い電位においては電気的に分離し、前 記所定の電位以上の電位においては電気的に接続する分離/接続領域とにより構成され、 前記画素電極に移動する電子の量が所定量までは前記第一の電荷蓄積領域、前記第二の電 荷蓄積領域、及び前記分離/接続領域の各々に前記画素電極から移動する電子を蓄積し、 前記画素電極に移動する電子の量が前記所定量を越えてからは前記第一の電荷蓄積領域の みに前記画素電極から移動する電子を蓄積するものであり、前記出力トランジスタは、前 記第二の電荷蓄積領域の電位に応じた信号を出力するものである。

# [0078]

開示された固体撮像素子は、前記所定の電位は前記リセット電位よりも低いものである

[0079]

開示された固体撮像素子は、前記分離 / 接続領域は、前記第一の電荷蓄積領域と前記第二の電荷蓄積領域の間の前記半導体基板上方に形成された、固定電圧が印加されるゲート電極によって形成されるものである。

20

10

30

40

#### [0800]

開示された固体撮像素子は、前記固定電圧が前記電源電圧であるものを含む。

#### [0081]

開示された固体撮像素子は、前記固定電圧が前記基準電圧であるものを含む。

## [0082]

開示された固体撮像素子は、前記分離 / 接続領域は、前記半導体基板内の前記第一の電荷蓄積領域と前記第二の電荷蓄積領域との間に形成された不純物領域により構成されるものである。

#### [0083]

開示された固体撮像素子は、前記不純物領域が、前記第一の電荷蓄積領域及び前記第二の電荷蓄積領域の各々と同一導電型であり、前記不純物領域の不純物濃度は、前記第一の電荷蓄積領域及び前記第二の電荷蓄積領域の各々よりも低いものである。

#### [0084]

開示された固体撮像素子は、前記不純物領域の表面に、前記不純物領域と逆導電型の別の不純物領域を備えるものである。

#### [0085]

開示された撮像装置は、前記固体撮像素子を備えるものである。

## 【符号の説明】

#### [0086]

100 固体撮像素子

101 画素

10 電荷蓄積部

- 11 第一の電荷蓄積領域

- 12 分離/接続領域

- 13 第二の電荷蓄積領域

- 2 1 画素電極

- 22 光電変換層

- 23 対向電極

- 30 半導体基板

- 31 リセットトランジスタ

32 出力トランジスタ

10

20

# 【図6】

# 【図7】

【図8】

F1G.8

FIG.6

【図9】

【図13】

# FIG.13

# 【図10】

【図14】

# FIG. 14

# 【図11】

FIG.11

【図12】

FIG.12

# フロントページの続き

# (56)参考文献 特開2005-268477(JP,A)

特開2009-147067(JP,A)

特開2010-233096(JP,A)

特開2010-016593(JP,A)

特開2007-081137(JP,A)

# (58)調査した分野(Int.CI., DB名)

H01L 27/14

H01L 31/10

H04N 5/374