# (19) **日本国特許庁(JP)**

(51) Int. C1.

# (12)特 許 公 報(B2)

$\mathbf{F}$  L

(11)特許番号

特許第3963663号 (P3963663)

(45) 発行日 平成19年8月22日(2007.8.22)

(24) 登録日 平成19年6月1日 (2007.6.1)

| (51) 1111.01. | 1 1                          |           |                          |

|---------------|------------------------------|-----------|--------------------------|

| HO1L 21/336   | <b>(2006.01)</b> HO1L        | 29/78     | 616A                     |

| HO1L 29/786   | <b>(2006.01)</b> GO2F        | 1/1368    |                          |

| GO2F 1/1368   | <i>3 (2006.01)</i> GO9F      | 9/30      | 338                      |

| GO9F 9/30     | <b>(2006.01)</b> GO9F        | 9/30      | 348A                     |

| HO1L 21/8238  | <b>8 (2006.01)</b> HO1L      | 27/08     | 3 2 1 E                  |

|               |                              |           | 請求項の数 18 (全 20 頁) 最終頁に続く |

| (21) 出願番号     | 特願2001-159754 (P2001-159754) | (73) 特許権: | 者 000153878              |

| (22) 出願日      | 平成13年5月28日 (2001.5.28)       |           | 株式会社半導体エネルギー研究所          |

| (62) 分割の表示    | 特願平6-137986の分割               |           | 神奈川県厚木市長谷398番地           |

| 原出願日          | 平成6年5月26日 (1994.5.26)        | (74) 代理人  | 100110858                |

| (65) 公開番号     | 特開2002-50637 (P2002-50637A)  |           | 弁理士 柳瀬 睦肇                |

| (43) 公開日      | 平成14年2月15日 (2002.2.15)       | (74) 代理人  | 100100413                |

| 審査請求日         | 平成13年6月27日 (2001.6.27)       |           | 弁理士 渡部 温                 |

| (31) 優先権主張番号  | 特願平6-114448                  | (72) 発明者  | 張 宏勇                     |

| (32) 優先日      | 平成6年4月29日 (1994.4.29)        |           | 神奈川県厚木市長谷398番地 株式会社      |

| (33) 優先権主張国   | 日本国(JP)                      |           | 半導体エネルギー研究所内             |

|               |                              | (72) 発明者  | 武内 晃                     |

|               |                              |           | 神奈川県厚木市長谷398番地 株式会社      |

|               |                              |           | 半導体エネルギー研究所内             |

|               |                              |           |                          |

|               |                              |           |                          |

|               |                              |           | 最終頁に続く                   |

#### (54) 【発明の名称】半導体装置

# (57)【特許請求の範囲】

#### 【請求項1】

を有し、

N チャネル型の薄膜トランジスタおよび前記 N チャネル型の薄膜トランジスタに接続する P チャネル型の薄膜トランジスタを有する半導体装置において、

それぞれの薄膜トランジスタは、

絶縁表面を有する基板上にソース領域、ドレイン領域およびチャネル形成領域を有する 半導体膜と、

前記チャネル形成領域に接するゲイト絶縁膜と、

前記ゲイト絶縁膜を介して前記チャネル形成領域に近接<u>し且つ前記チャネル形成領域の</u> 上方に位置するゲイト電極と、

前記ゲイト電極の側面に形成されたサイドウォールと、

前記Nチャネル型の薄膜トランジスタは、前記チャネル形成領域と前記ソース領域との間および前記チャネル形成領域と前記ドレイン領域との間それぞれに低濃度不純物領域を有し、

前記Pチャネル型の薄膜トランジスタは前記半導体膜に低濃度不純物領域を有してなく

前記Pチャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域は、前記Nチャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域と同じ濃度のN型不純物を有するとともに前記N型不純物より高濃度のP型不純物を有

し、

前記N型不純物は、第1のN型不純物と第2のN型不純物とからなり、

前記Nチャネル型の薄膜トランジスタにおける前記ソース領域、前記ドレイン領域および前記低濃度不純物領域並びに前記Pチャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域に、前記ゲイト電極をマスクとして、前記第1のN型不純物が導入され、前記Nチャネル型の薄膜トランジスタにおける半導体膜をマスク膜でマスクし且つ前記ゲイト電極をマスクとして、前記Pチャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域に前記P型不純物が導入され、前記Nチャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域並びに前記Pチャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域で、前記ゲイト電極と前記サイドウォールをマスクとして、前記第2のN型不純物が導入されることにより形成されたものであることを特徴とする半導体装置。

#### 【請求項2】

N チャネル型の薄膜トランジスタおよび前記 N チャネル型の薄膜トランジスタに接続する P チャネル型の薄膜トランジスタを有する半導体装置において、

それぞれの薄膜トランジスタは、

絶縁表面を有する基板上にソース領域、ドレイン領域およびチャネル形成領域を有する 半導体膜と、

前記チャネル形成領域に接するゲイト絶縁膜と、

前記ゲイト絶縁膜を介して前記チャネル形成領域に近接<u>し且つ前記チャネル形成領域の</u> 上方に位置するゲイト電極と、

前記ゲイト電極の側面に形成されたサイドウォールと、

# を有し、

前記Nチャネル型の薄膜トランジスタは、前記チャネル形成領域と前記ソース領域との間および前記チャネル形成領域と前記ドレイン領域との間それぞれに低濃度不純物領域を有し、

前記Pチャネル型の薄膜トランジスタは前記半導体膜に低濃度不純物領域を有してなく

前記 P チャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域は、前記 N チャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域と同<u>じ濃</u>度の N 型不純物を有するとともに前記 N 型不純物より高濃度の P 型不純物を有し、

前記N型不純物は、第1のN型不純物と第2のN型不純物とからなり、

前記 N チャネル型の薄膜トランジスタにおける半導体膜をマスク膜でマスクし<u>且つ前記ゲイト電極をマスクとして</u>、前記 P チャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域に前記 P 型不純物が導入され、前記 N チャネル型の薄膜トランジスタにおける前記ソース領域、前記ドレイン領域および前記低濃度不純物領域並びに前記 P チャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域に、前記ゲイト電極をマスクとして、前記第 1 の N 型不純物が導入され、前記 N チャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域並びに前記 P チャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域に、前記ゲイト電極と前記サイドウォールをマスクとして、前記第 2 の N 型不純物が導入されることにより形成されたものであることを特徴とする半導体装置。

# 【請求項3】

Nチャネル型の薄膜トランジスタおよび P チャネル型の薄膜トランジスタを有する半導体装置において、

それぞれの薄膜トランジスタは、

絶縁表面を有する基板上に形成され、ソース領域、ドレイン領域およびチャネル形成領域を有する半導体膜と、

前記半導体膜上に形成されたゲイト絶縁膜と、

10

20

30

前記ゲイト絶縁膜を介して前記チャネル形成領域の上方に形成されたゲイト電極と、 <u>前記ゲイト電極の側面に形成されたサイドウォールと、</u>

前記ゲイト絶縁膜および前記ゲイト電極の上方に形成された窒化珪素膜と を有し、

前記Nチャネル型の薄膜トランジスタは、前記チャネル形成領域と前記ソース領域との間および前記チャネル形成領域と前記ドレイン領域との間それぞれに低濃度不純物領域を有し、

前記Pチャネル型の薄膜トランジスタは前記半導体膜に低濃度不純物領域を有してなく

前記 P チャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域は、前記 N チャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域と同<u>じ濃</u>度の N 型不純物を有するとともに前記 N 型不純物より高濃度の P 型不純物を有し、

前記N型不純物は、第1のN型不純物と第2のN型不純物とからなり、

前記Nチャネル型の薄膜トランジスタにおける前記ソース領域、前記ドレイン領域および前記低濃度不純物領域並びに前記Pチャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域に、前記ゲイト電極をマスクとして、前記第1のN型不純物が導入され、前記Nチャネル型の薄膜トランジスタにおける半導体膜をマスク膜でマスクし且つ前記ゲイト電極をマスクとして、前記Pチャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域に前記P型不純物が導入され、前記Nチャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域並びに前記Pチャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域に、前記ゲイト電極と前記サイドウォールをマスクとして、前記第2のN型不純物が導入されることにより形成されたものであることを特徴とする半導体装置。

#### 【請求項4】

Nチャネル型の薄膜トランジスタおよび P チャネル型の薄膜トランジスタを有する半導体装置において、

それぞれの薄膜トランジスタは、

絶縁表面を有する基板上に形成され、ソース領域、ドレイン領域およびチャネル形成領域を有する半導体膜と、

前記半導体膜上に形成されたゲイト絶縁膜と、

前記ゲイト絶縁膜を介して前記チャネル形成領域の上方に形成されたゲイト電極と、

前記ゲイト電極の側面に形成されたサイドウォールと、

前記ゲイト絶縁膜および前記ゲイト電極の上方に形成された窒化珪素膜と を有し、

前記Nチャネル型の薄膜トランジスタは、前記チャネル形成領域と前記ソース領域との間および前記チャネル形成領域と前記ドレイン領域との間それぞれに低濃度不純物領域を有し、

前記Pチャネル型の薄膜トランジスタは前記半導体膜に低濃度不純物領域を有してなく

前記 P チャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域は、前記 N チャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域と同<u>じ濃</u>度の N 型不純物を有するとともに前記 N 型不純物より高濃度の P 型不純物を有し、

前記N型不純物は、第1のN型不純物と第2のN型不純物とからなり、

前記 N チャネル型の薄膜トランジスタにおける半導体膜をマスク膜でマスクし<u>且つ前記ゲイト電極をマスクとして</u>、前記 P チャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域に前記 P 型不純物が導入され、前記 N チャネル型の薄膜トランジスタにおける前記ソース領域、前記ドレイン領域および前記低濃度不純物領域並びに前記 P チャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域に<u>、</u>

10

20

30

前記ゲイト電極をマスクとして、前記第1のN型不純物が導入され、前記Nチャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域並びに前記Pチャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域に、前記ゲイト電極と前記サイドウォールをマスクとして、前記第2のN型不純物が導入されることにより形成されたものであることを特徴とする半導体装置。

#### 【請求項5】

請求項1乃至4のいずれか一において、前記半導体装置は入力ポートであることを特徴とする半導体装置。

#### 【請求項6】

請求項1乃至4のいずれか一において、前記半導体装置はCPUであることを特徴とする半導体装置。

#### 【請求項7】

請求項1乃至4のいずれか一において、前記半導体装置はメモリーであることを特徴と する半導体装置。

# 【請求項8】

請求項1乃至4のいずれか一において、前記半導体装置はデコーダーであることを特徴とする半導体装置。

### 【請求項9】

絶縁表面を有する基板上に形成された薄膜トランジスタを有する画素と、前記画素を駆動する駆動回路とを有する半導体装置において、

前記駆動回路は、Nチャネル型の薄膜トランジスタおよび前記Nチャネル型の薄膜トランジスタに接続するPチャネル型の薄膜トランジスタを有し、前記駆動回路におけるそれぞれの薄膜トランジスタは、

前記基板上にソース領域、ドレイン領域およびチャネル形成領域を有する半導体膜と、 前記チャネル形成領域に接するゲイト絶縁膜と、

前記ゲイト絶縁膜を介して前記チャネル形成領域に近接<u>し且つ前記チャネル形成領域の</u> 上方に位置するゲイト電極と、

前記ゲイト電極の側面に形成されたサイドウォールと、

# を有し、

前記Nチャネル型の薄膜トランジスタは、前記チャネル形成領域と前記ソース領域との間および前記チャネル形成領域と前記ドレイン領域との間それぞれに低濃度不純物領域を有し、

前記Pチャネル型の薄膜トランジスタは前記半導体膜に低濃度不純物領域を有してなく

前記 P チャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域は、前記 N チャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域と同<u>じ濃度の N 型不純物を有するとともに前記 N 型不純物より高濃度の P 型不純物を有し、</u>

前記N型不純物は、第1のN型不純物と第2のN型不純物とからなり、

前記 N チャネル型の薄膜トランジスタにおける前記ソース領域、前記ドレイン領域および前記低濃度不純物領域並びに前記 P チャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域に、前記ゲイト電極をマスクとして、前記第1のN型不純物が導入され、前記 N チャネル型の薄膜トランジスタにおける半導体膜をマスク膜でマスクし且つ前記ゲイト電極をマスクとして、前記 P チャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域に前記 P 型不純物が導入され、前記 N チャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域並びに前記 P チャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域で、前記ゲイト電極と前記サイドウォールをマスクとして、前記第2のN型不純物が導入されることにより形成されたものであることを特徴とする半導体装置。

# 【請求項10】

20

30

絶縁表面を有する基板上に形成された薄膜トランジスタを有する画素と、前記画素を駆 動する駆動回路とを有する半導体装置において、

前記駆動回路は、Nチャネル型の薄膜トランジスタおよび前記Nチャネル型の薄膜トラ ンジスタに接続するPチャネル型の薄膜トランジスタを有し、前記駆動回路におけるそれ ぞれの薄膜トランジスタは、

前記基板上にソース領域、ドレイン領域およびチャネル形成領域を有する半導体膜と、 前記チャネル形成領域に接するゲイト絶縁膜と、

前記ゲイト絶縁膜を介して前記チャネル形成領域に近接し且つ前記チャネル形成領域の 上方に位置するゲイト電極と、

前記ゲイト電極の側面に形成されたサイドウォールと、 を有し、

前記Nチャネル型の薄膜トランジスタは、前記チャネル形成領域と前記ソース領域との 間および前記チャネル形成領域と前記ドレイン領域との間それぞれに低濃度不純物領域を 有し、

前記Pチャネル型の薄膜トランジスタは前記半導体膜に低濃度不純物領域を有してなく

前記Pチャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域 は、前記Nチャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領 域と同じ濃度のN型不純物を有するとともに前記N型不純物より高濃度のP型不純物を有 し、

前記N型不純物は、第1のN型不純物と第2のN型不純物とからなり、

前記Nチャネル型の薄膜トランジスタにおける半導体膜をマスク膜でマスクし且つ前記 <u>ゲイト電極をマスクとして</u>、前記 P チャネル型の薄膜トランジスタにおける前記ソース領 域および前記ドレイン領域に前記P型不純物が導入され、前記Nチャネル型の薄膜トラン ジスタにおける前記ソース領域、前記ドレイン領域および前記低濃度不純物領域並びに前 記Pチャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域に、 前記ゲイト電極をマスクとして、前記第1のN型不純物が導入され、前記Nチャネル型の 薄膜トランジスタにおける前記ソース領域および前記ドレイン領域並びに前記Pチャネル 型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域に、前記ゲイト電 極と前記サイドウォールをマスクとして、前記第2のN型不純物が導入されることにより 形成されたものであることを特徴とする半導体装置。

# 【請求項11】

絶縁表面を有する基板上に形成された薄膜トランジスタを有する画素と、前記画素を駆 動する駆動回路とを有する半導体装置において、

前記駆動回路は、Nチャネル型の薄膜トランジスタおよびPチャネル型の薄膜トランジ スタを有し、前記駆動回路におけるそれぞれの薄膜トランジスタは、

前記基板上に形成され、ソース領域、ドレイン領域およびチャネル形成領域を有する半 導体膜と、

前記半導体膜上に形成されたゲイト絶縁膜と、

前記ゲイト絶縁膜を介して前記チャネル形成領域の上方に形成されたゲイト電極と、

前記ゲイト電極の側面に形成されたサイドウォールと、

前記ゲイト絶縁膜および前記ゲイト電極の上方に形成された窒化珪素膜と を有し、

前記Nチャネル型の薄膜トランジスタは、前記チャネル形成領域と前記ソース領域との 間および前記チャネル形成領域と前記ドレイン領域との間それぞれに低濃度不純物領域を 有し、

前記Pチャネル型の薄膜トランジスタは前記半導体膜に低濃度不純物領域を有してなく

前記Pチャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域 は、前記Nチャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領 10

20

30

40

域と同<u>じ濃</u>度のN型不純物を有するとともに前記N型不純物より高濃度のP型不純物を有し、

前記N型不純物は、第1のN型不純物と第2のN型不純物とからなり、

前記Nチャネル型の薄膜トランジスタにおける前記ソース領域、前記ドレイン領域および前記低濃度不純物領域並びに前記Pチャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域に、前記ゲイト電極をマスクとして、前記第1のN型不純物が導入され、前記Nチャネル型の薄膜トランジスタにおける半導体膜をマスク膜でマスクし且つ前記ゲイト電極をマスクとして、前記Pチャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域に前記P型不純物が導入され、前記Nチャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域並びに前記Pチャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域に、前記ゲイト電極と前記サイドウォールをマスクとして、前記第2のN型不純物が導入されることにより形成されたものであることを特徴とする半導体装置。

# 【請求項12】

絶縁表面を有する基板上に形成された薄膜トランジスタを有する画素と、前記画素を駆動する駆動回路とを有する半導体装置において、

前記駆動回路は、Nチャネル型の薄膜トランジスタおよびPチャネル型の薄膜トランジスタを有し、前記駆動回路におけるそれぞれの薄膜トランジスタは、

前記基板上に形成され、ソース領域、ドレイン領域およびチャネル形成領域を有する半 導体膜と、

前記半導体膜上に形成されたゲイト絶縁膜と、

前記ゲイト絶縁膜を介して前記チャネル形成領域の上方に形成されたゲイト電極と、

前記ゲイト電極の側面に形成されたサイドウォールと、

前記ゲイト絶縁膜および前記ゲイト電極の上方に形成された窒化珪素膜と を有し、

前記Nチャネル型の薄膜トランジスタは、前記チャネル形成領域と前記ソース領域との間および前記チャネル形成領域と前記ドレイン領域との間それぞれに低濃度不純物領域を有し、

前記Pチャネル型の薄膜トランジスタは前記半導体膜に低濃度不純物領域を有してなく

前記 P チャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域は、前記 N チャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域と同<u>じ濃</u>度の N 型不純物を有するとともに前記 N 型不純物より高濃度の P 型不純物を有し、

前記N型不純物は、第1のN型不純物と第2のN型不純物とからなり、

前記 N チャネル型の薄膜トランジスタにおける半導体膜をマスク膜でマスクし<u>且つ前記ゲイト電極をマスクとして</u>、前記 P チャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域に前記 P 型不純物が導入され、前記 N チャネル型の薄膜トランジスタにおける前記ソース領域、前記ドレイン領域および前記低濃度不純物領域並びに前記 P チャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域に、前記ゲイト電極をマスクとして、前記第1のN型不純物が導入され、前記 N チャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域並びに前記 P チャネル型の薄膜トランジスタにおける前記ソース領域および前記ドレイン領域に、前記ゲイト電極と前記サイドウォールをマスクとして、前記第2のN型不純物が導入されることにより形成されたものであることを特徴とする半導体装置。

# 【請求項13】

請求項1乃至<u>12</u>のいずれかーにおいて、前記Pチャネル型の薄膜トランジスタのソース領域およびドレイン領域は、燐とホウ素の両方を含んでいることを特徴とする半導体装置。

【請求項14】

20

30

請求項1乃至13のいずれか一において、前記低濃度不純物領域は不純物の濃度が前記ソース領域および前記ドレイン領域よりも低い領域であることを特徴とする半導体装置。

# 【請求項15】

請求項1乃至<u>14</u>のいずれかーにおいて、前記Nチャネル型の薄膜トランジスタにおける前記N型不純物は燐であり、前記Pチャネル型の薄膜トランジスタにおける前記P型不 純物はホウ素であることを特徴とする半導体装置。

#### 【請求項16】

請求項1乃至<u>15</u>のいずれかーにおいて、前記Nチャネル型の薄膜トランジスタの低濃度不純物領域におけるドーズ量は $5 \times 10^{14}$ 原子/ $cm^2$ 以下であることを特徴とする半導体装置。

### 【請求項17】

請求項 1 乃至 15 のいずれかーにおいて、前記 N チャネル型の薄膜トランジスタの低濃度不純物領域におけるドーズ量は  $1 \times 10^{13} \sim 5 \times 10^{14}$  原子  $/ cm^2$  であることを特徴とする半導体装置。

#### 【請求項18】

請求項1乃至<u>17</u>のいずれかーにおいて、前記Nチャネル型の薄膜トランジスタおよび前記Pチャネル型の薄膜トランジスタからなる相補型回路を有することを特徴とする半導体装置。

### 【発明の詳細な説明】

### [0001]

#### 【発明の属する技術分野】

本発明は、絶縁基板(本明細書では絶縁性の表面を有する物体全体を指し、特に断らないかぎり、ガラス等の絶縁材料のみならず、半導体や金属等の材料上に絶縁物層を形成したものも意味する)上に薄膜状の絶縁ゲイト型半導体装置(薄膜トランジスタ、TFTともいう)が形成された集積回路およびそれを形成する方法に関する。本発明による半導体集積回路は、液晶ディスプレー等のアクティブマトリクス回路およびその周辺駆動回路やイメージセンサー等の駆動回路、あるいはSOI集積回路や従来の半導体集積回路(マイクロプロセッサーやマイクロコントローラ、マイクロコンピュータ、あるいは半導体メモリー等)に使用されるものである。

# [0002]

# 【従来の技術】

従来より、アクティブマトリックス型の液晶表示装置やイメージセンサー等の回路をガラス基板上に形成する場合において、薄膜トランジスタ(TFT)を集積化して利用する構成が広く知られている。この場合には、通常、最初にゲイト電極を含む 1 層目の配線を形成し、その後、層間絶縁物を形成した後、 2 層目の配線を形成する方法が一般的であり、必要に応じては、さらに 3 層目、 4 層目の配線を形成することもあった。

# [0003]

# 【発明が解決しようとする課題】

このような薄膜トランジスタの集積回路における最大の問題点はゲイト電極の延長上の配線(ゲイト配線)と、2層目の配線の交差する部分(乗り越え部)における2層目の配線の断線(段切れ、ともいう)であった。これは、ゲイト電極・配線上の層間絶縁物をステップカバレージよく形成し、さらに、平坦化することが困難なためであった。

# [0004]

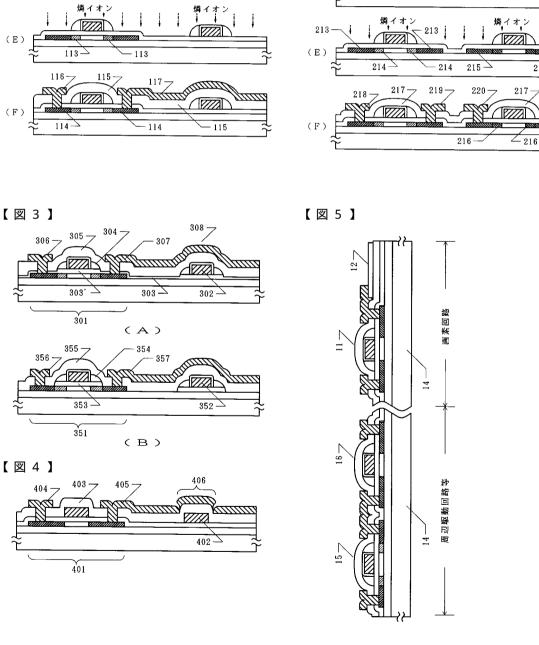

図4には従来のTFT集積回路でよく見られた断線不良の様子を示したものである。基板上にTFT領域401とゲイト配線402が設けられており、これらを覆って、層間絶縁物403が形成されている。しかしながら、ゲイト配線402のエッジが急峻であると、層間絶縁物403がゲイト配線を十分に被覆することができない。そして、このような状態において、2層目の配線404、405を形成した場合には、ゲイト配線の乗り越え部406において、2層目配線が図に示すように断線(段切れ)してしまう。

# [0005]

50

40

20

10

このような段切れを防止するには、2層目の配線の厚みを増すことが必要であった。例えば、ゲイト配線の2倍程度の厚さにすることが望まれた。しかし、このことは、集積回路の凹凸がさらに増加することを意味し、その上にさらに配線を重ねることが必要な場合には、2層目配線の厚みによる断線も考慮しなければならなかった。また、液晶ディスプレーのように集積回路の凹凸が好まれない回路を形成する場合には、2層目配線の厚みを増すことによる対処は実質的に不可能であった。

集積回路においては、段切れが1か所でも存在すると、全体が不良となってしまうため、 段切れをいかに減らすかが重要な課題であった。本発明は、このような段切れ不良を減ら す方法を提供し、よって集積回路の歩留りを上げることを課題とする。

#### [0006]

【課題を解決するための手段】

本発明においては、ゲイト電極・配線の少なくとも上面にゲイト電極を陽極酸化法によって酸化することによって、酸化物被膜を形成し、さらに、ゲイト電極・配線の側面に異方性エッチングによって概略三角形状の絶縁物(サイドウォール)を形成したのち、層間絶縁物を堆積し、さらに、2層目の配線を形成することを特徴とする。陽極酸化法によって形成される酸化物被膜は、後に形成されるサイドウォールを構成する材料に比較して、エッチングされにくいことが必要であり、サイドウォールを酸化珪素によって形成する場合には、酸化アルミニウム、酸化タンタル、酸化チタン、酸化モリブテン、酸化タングステング等が好ましい。これらの材料は、酸化珪素をドライエッチング法によってエッチングする条件、すなわち、弗素系のエッチングガス(例えば、NF3、SF6)によるエッチングでは極めてエッチングレートが低い。

[0007]

本発明を実施する第1の方法は以下のようなものである。まず、島状の半導体層を形成する。さらに、その上にゲイト絶縁膜となる被膜を形成する。さらに、ゲイト電極・配線を形成する。この際、ゲイト電極・配線は陽極酸化される材料で形成され、かつ、陽極酸化の結果、得られる被膜は上記のようにサイドウォールに比較してエッチングされにくいことが必要である。

その後、ゲイト電極・配線にほぼ中性の電解溶液中において正の電圧を印加して、ゲイト電極・配線の少なくとも上面に陽極酸化物被膜を形成する。この工程は、気相陽極酸化法によってもよい。 ここまでが第1の段階である。

[0008]

その後、ゲイト電極・配線およびその周囲の陽極酸化物被膜を覆って、絶縁物被膜を形成する。この被膜形成においては被覆性が重要であり、また、ゲイト電極・配線の高さの1/3~2倍の厚さが好適である。この目的には、プラズマCVD法や減圧CVD法、大気圧CVD法等の化学的気相成長(CVD)法が好ましい。そして、このように形成された絶縁物を異方性エッチングによって基板に対して概略垂直な方向に優先的にエッチングする。エッチングの終了は、平坦部における該絶縁物被膜がエッチングされる程度であり、さらに、その下のゲイト絶縁膜がエッチングされる程度までエッチングをすすめてもよい。その結果、ゲイト電極・配線の側面のごとき、段差部では、もともと該絶縁物被膜が厚いので、概略三角形城の絶縁物(サイドウォール)が取り残される。ここまでが第2の段階である。

[0009]

その後、層間絶縁物を形成したのち、TFTのソース / ドレインの一方もしくが双方にコンタクトホールを形成し、2層目の配線を形成する。ここまでが第3の段階である。以上の段階において、TFTのソース / ドレインを形成するためにドーピングをおこなうのはさまざまな場合が考えられる。例えば、基板上にNチャネル型TFTのみを形成する場合には、第1段階と第2段階の間に、比較的、高濃度のN型不純物をゲイト電極およびその周囲の陽極酸化物被膜をマスクとして半導体層に自己整合的に導入すればよい。この場合には、陽極酸化物被膜がゲイト電極の側面に存在した場合には、陽極酸化物の厚さ分だけソース / ドレインとゲイト電極が離れた、いわゆるオフセットゲイト型となる。しか

10

20

30

40

し、以下の説明では、このようなケースも含めて、通常のTFTと称することとする。

# [0010]

同じく、Nチャネル型TFTを形成する場合においても、低濃度ドレイン(LDD)を有するTFT(LDD型TFT)を形成する場合には、第1段階と第2段階の間に、比較的低濃度の不純物を半導体層に導入したのち、第2段階と第3段階の間に、より高濃度のN型不純物をゲイト電極およびサイドウォールをマスクとして自己整合的に半導体層に導入すればよい。この場合には、LDDの幅はサイドウォールの幅と概略同一である。基板上にPチャネル型TFTのみを形成する場合も上記と同様にすればよい。

#### [0011]

基板上にNチャネル型TFTとPチャネル型TFTを混在させた、いわゆる相補型回路(CMOS回路)を形成することも上記の方法を使用して同様におこなえる。Nチャネル型TFTおよびPチャネル型TFTともに通常のTFTで構成する場合、もしくは、共にLDD型TFTで構成するには不純物の導入は、上記に示したNチャネル型もしくはPチャネル型のTFTの一方のみを基板上に形成する方法における不純物の導入を、N型不純物とP型不純物についてそれぞれおこなえばよい。

#### [0012]

例えば、ホットキャリヤ対策の必要なNチャネル型TFTはLDD型とし、その必要がないPチャネル型TFTは通常のTFTとする場合には、不純物導入の工程はやや特殊なものとなる。その場合には、第1段階と第2段階の間に、比較的低濃度のN型不純物を半導体層に導入する。これを第1の不純物導入とする。この際には、Pチャネル型TFTの半導体層にもN型不純物を導入してもよい。

さらに、Nチャネル型TFTの半導体層をマスクして、Pチャネル型TFTの半導体層にのみ高濃度のP型不純物を導入する。これを第2の不純物導入とする。この不純物導入によって、仮に先のN型不純物の導入によって、Pチャネル型TFTの半導体層にN型不純物が存在したとしても、より高濃度のPチャネル型不純物が導入された結果、半導体の導電型はP型である。当然、第1の不純物導入において導入される不純物濃度に比較すると、第2の不純物導入のそれはより大きく、好ましくは、1~3桁大きい。

### [0013]

最後に、Nチャネル型TFTのソース/ドレインを形成するために比較的、高濃度のN型不純物を、第2段階と第3段階の間に導入する。これを第3の不純物導入とする。この場合には、Pチャネル型TFTにN型不純物が導入されないように、マスクして不純物導入をおこなってもよいし、特にマスクをおこなわなくてもよい。しかし、後者の場合には導入するN型不純物の濃度は、第2の不純物導入で導入されたP型不純物の濃度よりも小さいことが必要であり、好ましくは、第2の不純物導入のP型不純物の濃度の1/10~2/3である。この結果、Pチャネル型TFTの領域にもN型不純物が導入されるが、不純物濃度はその前に導入されたP型不純物の濃度よりも小さいために、P型は維持される。

#### [0014]

# 〔作用〕

本発明においてはサイドウォールの存在によってゲイト配線の乗り越え部分における層間 絶縁物の段差被覆性が向上し、第 2 配線の段切れを減らすことができる。また、上記に示 したように、サイドウォールを利用することにより、LDD構造を得ることも可能である

本発明においては、陽極酸化物被膜の存在は重要である。上記の第2段階において、サイドウォールを形成するために異方性エッチングをおこなう。しかしながら、絶縁表面上においてはプラズマを制御することが難しく、基板内でのエッチングのばらつきは避けられないものであった。もし、ゲイト電極の上面に陽極酸化物が形成されていない場合には、同じ基板内であっても、場所によってはゲイト電極が激しくエッチングされてしまうこともある。陽極酸化物被膜が存在すれば、エッチングはストップし、ゲイト電極は保護される。以下に実施例を示し、より詳細に本発明を説明する。

# [0015]

40

20

20

30

40

50

### 【実施例】

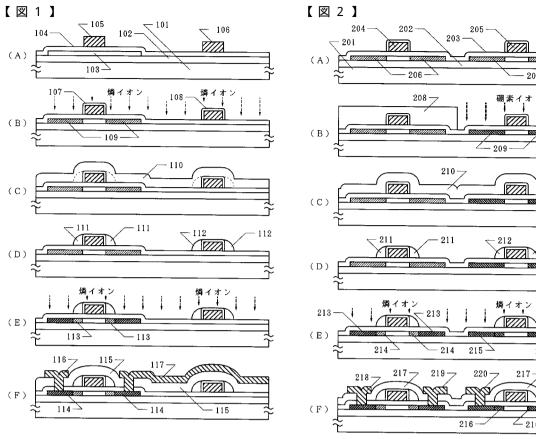

[実施例1] 図1に本実施例を示す。まず、基板(コーニング7059、300mm×400mmもしくは100mm×100mm)101上に下地酸化膜102として厚さ1000~5000 、例えば、2000 の酸化珪素膜を形成した。この酸化膜の形成方法としては、酸素雰囲気中でのスパッタ法を使用した。しかし、より量産性を高めるには、TEOSをプラズマCVD法で分解・堆積して形成してもよい。また、このように形成した酸化珪素膜を400~650 でアニールしてもよい。

### [0016]

その後、プラズマCVD法やLPCVD法によってアモルファス状のシリコン膜を300~5000、好ましくは400~1000、例えば、500 堆積し、これを、550~600 の還元雰囲気に8~24時間放置して、結晶化せしめた。その際には、ニッケル等の結晶化を助長する金属元素を微量添加して結晶化を促進せしめてもよい。また、この工程は、レーザー照射によっておこなってもよい。そして、このようにして結晶化させたシリコン膜をエッチングして島状領域103を形成した。さらに、この上にプラズマCVD法によって厚さ700~1500、例えば、1200 の酸化珪素膜104を形成した。

# [0017]

その後、厚さ1000 ~3 μm、例えば、5 0 0 0 のアルミニウム(1 w t % の S i 、もしくは 0 . 1 ~ 0 . 3 w t % の S c (スカンジウム)を含む)膜をスパッタ法によって形成して、これをエッチングし、ゲイト電極 1 0 5 およびゲイト配線 1 0 6 を形成した。(図 1 ( A ))

そして、ゲイト電極105およびゲイト電極106に電解液中で電流を通じて陽極酸化し、厚さ500~2500 、例えば、2000 の陽極酸化物107、108を形成した。用いた電解溶液は、L-酒石酸をエチレングリコールに5%の濃度で希釈し、アンモニアを用いてpHを7.0±0.2に調整したものである。その溶液中に基板101を浸し、定電流源の+側を基板上のゲイト配線に接続し、-側には白金の電極を接続して20mAの定電流状態で電圧を印加し、150Vに到達するまで酸化を継続した。さらに、150Vで定電圧状態で加え0.1mA以下になるまで酸化を継続した。この結果、厚さ2000 の酸化アルミニウム被膜が得られた。

#### [0018]

その後、イオンドーピング法によって、島状シリコン膜 1 0 3 に、ゲイト電極部(すなわちゲイト電極とその周囲の陽極酸化膜)をマスクとして自己整合的に不純物(ここでは燐)を注入し、図 1 (B)に示すように低濃度不純物領域(LDD) 1 0 9 を形成した。ドーズ量は 1 × 1 0  $^{13}$  ~ 5 × 1 0  $^{14}$  原子 / c m  $^2$  、加速電圧は 1 0 ~ 9 0 k V、例えば、、ドーズ量を 5 × 1 0  $^{13}$  原子 / c m  $^2$  、加速電圧は 8 0 k V とした。(図 1 (B))

# [0019]

そして、プラズマCVD法によって、酸化珪素膜110を堆積した。ここでは、原料ガスにTEOSと酸素、もしくはモノシランと亜酸化窒素を用いた。酸化珪素膜110の厚さはゲイト電極・配線の高さによって最適な値が異なる。例えば、本実施例のごとく、ゲイト電極・配線の高さが陽極酸化物被膜も含めて約6000 の場合には、その1/3~2倍の2000 ~1.2 $\mu$ mが好ましく、ここでは、6000 とした。この成膜工程においては、平坦部での膜厚の均一性をともに、ステップカバレージが良好であることも要求される。その結果、ゲイト電極・配線の側面部の酸化珪素膜の厚さは、図1(C)に点線で示す分だけ厚くなっている。(図1(C))

#### [0020]

次に、公知のRIE法による異方性ドライエッチングをおこなうことによって、この酸化 珪素膜108のエッチングをおこなった。このエッチングはゲイト絶縁膜105までエッ チングが達した時点で終了した。このようなエッチングの終点に関しては、例えば、ゲイ ト絶縁膜105のエッチングレートを、酸化珪素膜110のものに比較して小さくするこ とによって、制御することが可能である。以上の工程によって、ゲイト電極・配線の側面

30

40

50

には概略三角形状の絶縁物(サイドウォール) 1 1 1 、 1 1 2 が残った。(図 1 ( D ) ) 【 0 0 2 1 】

その後、再び、イオンドーピング法によって、燐を導入した。この場合のドーズ量は、図 1 (B)の工程のドーズ量より 1 ~ 3 桁多いことが好ましい。本実施例では、最初の燐のドーピングのドーズ量の 4 0 倍の  $2 \times 10^{15}$  原子 / c  $m^2$  とした。加速電圧は 8 0 k V とした。この結果、高濃度の燐が導入された領域(ソース / ドレイン) 1 1 4 が形成され、また、サイドウォールの下部には低濃度領域(LDD) 1 1 3 が残された。(図 1 (E))

### [0022]

さらに、KrFエキシマーレーザー(波長248nm、パルス幅20nsec)を照射して、ドーピングされた不純物の活性化をおこなった。レーザーのエネルギー密度は200~400mJ/cm²、好ましくは250~300mJ/cm²が適当であった。なお、本実施例ではゲイト電極・配線にアルミニウムを用いたため、耐熱性の点で問題があり、実施することが困難であるが、レーザー照射による代わりに、熱アニールによっておこなってもよい。

#### [0023]

最後に、全面に層間絶縁物115として、CVD法によって酸化珪素膜を厚さ5000 形成した。そして、TFTのソース/ドレインにコンタクトホールを形成し、2層目のアルミニウム配線・電極116、117を形成した。アルミニウム配線の厚さはゲイト電極・配線とほぼ同じ、4000~6000 とした。以上の工程によって、Nチャネル型のLDDを有するTFTが完成された。不純物領域の活性化のために、さらに200~400 で水素アニールをおこなってもよい。2層目配線117はゲイト配線106を乗り越える部分での段差が、サイドウォール112の存在によって緩やかになっているため、2層目の配線の厚さがゲイト電極・配線とほぼ同じであるにも関わらず、段切れはほとんど観察されなかった。(図1(F))

# [0024]

なお、2層目配線の厚さに関しては、本発明人の検討の結果、ゲイト電極・配線の厚さをx [ ]、2層目配線の厚さをy [ ]とした場合に、

y x - 1 0 0 0 ( )

であれば、顕著な断線はなかった。 y の値は小さければ小さいほど好ましく、特に液晶ディスプレーのアクティブマトリクス回路のように基板表面の凹凸の少ないことが要求される回路の場合には、

x - 1 0 0 0 [ ] y x + 1 0 0 0 [ ] が適当であることがわかった。

# [0025]

[実施例2] 図2に本実施例を示す。本実施例は同一基板上にアクティブマトクス回路とその駆動回路が同時に作製される、いわゆる、モノリシック型アクティブマトリクス回路に関するものである。本実施例では、アクティブアトリクス回路のスイッチング素子にはPチャネル型TFTを、駆動回路にはNチャネル型TFTとPチャネル型TFTによって構成される相補型回路用いた。図2の左側には、駆動回路で用いられるNチャネル型TFTの作製工程断面図を、また、同図の右側には、駆動回路ならびにアクティブマトリクス回路に用いられるPチャネル型TFTの作製工程断面図を示す。アクティブマトリクス回路のスイッチング素子にPチャネル型TFTを用いたのは、リーク電流(オフ電流ともいう)が小さいためである。

#### [0026]

まず、基板(コーニング7059)201上に実施例1と同様に下地酸化膜202、島状シリコン半導体領域、ゲイト酸化膜として機能する酸化珪素膜203を形成し、アルミニウム膜(厚さ5000 )によるゲイト電極204、205を形成した。その後、実施例1と同様に陽極酸化によって、ゲイト電極の周囲(側面と上面)に厚さ2000 の陽極酸化物を形成した。そして、ゲイト電極部をマスクとしてイオンドーピング法によって燐

30

40

50

の注入をおこない、低濃度の N 型不純物領域 2 0 6 、 2 0 7 を形成した。ドーズ量は 1  $\times$  1 0  $^{13}$ 原子 / c m  $^2$  とした。

### [0027]

さらに、KrFエキシマーレーザー(波長 2 4 8 n m、パルス幅 2 0 n s e c )を照射して、ドーピングされた不純物の活性化をおこなった。レーザーのエネルギー密度は 2 0 0 ~ 4 0 0 m J / c m  $^2$  、好ましくは 2 5 0 ~ 3 0 0 m J / c m  $^2$  が適当であった。(図 2 ( A ) )

その後、Nチャネル型TFTの領域をフォトレジスト208でマスクし、この状態で、イオンドーピング法によって高濃度のホウ素のドーピングをおこなった。ドーズ量は $5\times1$ 0 $^{15}$ 原子/cm $^2$ 、加速電圧は6.5k V とした。この結果、先の燐のドーピングによって、弱いN型となった不純物領域207は強いP型に反転し、P型不純物領域209となった。その後、再び、レーザー照射によって、不純物の活性化をおこなった。(図2(B))

なお、本実施例では、低濃度の燐の全面ドーピングの後に、高濃度のホウ素の部分選択ドーピングをおこなったが、この工程は逆にしてもよい。

#### [0028]

フォトレジストのマスク 2 0 8 を除去した後、プラズマ C V D 法によって厚さ 4 0 0 0 ~ 8 0 0 0 の酸化珪素膜 2 1 0 を堆積した。(図 2 ( C ) )

そして、実施例1と同様に異方性エッチングによって、ゲイト電極の側面に酸化珪素のサイドウォール211、212を形成した。(図2(D))

その後、再び、イオンドーピング法によって、燐を導入した。この場合のドーズ量は、図2(A)の工程のドーズ量より1~3桁多く、かつ、図2(B)の工程のドーズ量の1/10~2/3が好ましい。本実施例では、最初の燐のドーピングのドーズ量の200倍の $2\times10^{15}$ 原子/cm² とした。しかし、これは図2(B)の工程のホウ素のドーズ量の40%である。加速電圧は80kVとした。この結果、高濃度の燐が導入された領域(ソース/ドレイン)213が形成され、また、サイドウォールの下部には低濃度不純物領域(LDD)214が残された。

#### [0029]

さらに、KrFエキシマーレーザー(波長248nm、パルス幅20nsec)を照射して、ドーピングされた不純物の活性化をおこなった。レーザーのエネルギー密度は200~400mJ/cm²、好ましくは250~300mJ/cm²が適当であった。 一方、Pチャネル型TFTの領域(図の右側)にも燐がドーピングされたのであるが、先

にドーピングされたホウ素の濃度が燐の2.5倍であるのでP型のままであった。Pチャネル型TFTのP型領域は見掛け上、サイドウォールの下の領域216とその外側(チャネル形成領域の反対側)の領域215の2種類存在するように思えるが、電気的特性の面からは両者には大した差が見られなかった。(図2(E))

#### [0030]

最後に、図2(F)に示すように、全面に層間絶縁物217として、CVD法によって酸化珪素膜を厚さ3000 形成し、TFTのソース / ドレインにコンタクトホールを形成し、アルミニウム配線・電極218、219、220、221を形成した。以上の工程によって、Nチャネル型TFTがLDD型である半導体集積回路が完成された。

図では示されていないが、ゲイト配線を 2 層目の配線が乗り越える部分では、層間絶縁物がさして厚くないにも関わらず、実施例 1 と同様に断線はほとんど見られなかった。

# [0031]

本実施例のようにNチャネル型TFTをLDD構造とするのはホットキャリヤによる劣化を防止するためである。しかし、LDD領域はソース/ドレインに対して直列に挿入された寄生抵抗であるので、動作速度が落ちてしまうという問題があった。したがって、モビリティーが小さく、ホットキャリヤによる劣化の少ないPチャネル型TFTでは、本実施例のようにLDDが存在しないほうが望ましい。

なお、本実施例では、ドーピング工程ごとにレーザー照射によるドーピング不純物の活性

20

30

40

50

化をおこなったが、全てのドーピング工程が終了し、層間絶縁物を形成する直前に、一括 しておこなってもよい。

#### [0032]

〔実施例3〕 本実施例を図3を用いて説明する。本実施例は、実施例1において、サイドウォールを形成するためのエッチングの程度をさまざまに変えた例を示す。ず、図3(A)で示されるものに関して説明する。図にはTFT領域301とゲイト配線302が示されている。このような構造を得るための作製プロセスは実施例1において、図1を用いて説明したものと同様である。

ただし、本実施例では、サイドウォール304を形成するための異方性エッチングの工程において、ややオーバーエッチ気味にエッチングをおこなったため、サイドウォール304がゲイト電極・配線の上面よりもやや下に位置している。また、ゲイト絶縁膜303までエッチングされることとなった。

#### [0033]

本実施例では、サイドウォール304を構成する材料のエッチングレートはゲイト絶縁膜303の約2倍であった。そのため、同じエッチング条件であったも、ゲイト絶縁膜のエッチングされる深さは、サイドウォールの約半分であった。本実施例では、ゲイト絶縁膜は初期の厚さの約半分にまでエッチングされた。一方、サイドウォール304とゲイト電極・配線の下方に存在するゲイト絶縁膜303°の厚さは初期の厚さと同じである。また、ゲイト電極・配線は陽極酸化物によって被覆されていたので、サイドウォール形成のための異方性エッチングの工程においてもほとんどダメージを受けなかった。

# [0034]

このような状態において、層間絶縁物305を全面に形成した。サイドウォール304は 実施例1よりもやや低い位置に存在していたが、従来の場合と違って、ゲイト配線302 付近の段差が緩やかであるので、層間絶縁物は十分にゲイト配線の乗り越え部308を被 覆していた。

その後、2層目の配線306、307を形成したが、ゲイト乗り越え部308での層間絶縁物305の起伏が緩やかであるので、当該部分での断線はなかった。

### [0035]

図3 (B)は、サイドウォール354を構成する材料のエッチングレートはゲイト絶縁膜353とほぼ同じ場合である。そのため、同じエッチング条件で、ゲイト絶縁膜もサイドウォールもほぼ同様にエッチングされた。本実施例では、ゲイト絶縁膜は完全にエッチングされ、TFTの活性層が露出する状態となった。この場合においても、ゲイト乗り越え部での層間絶縁物355の起伏が緩やかであるので、2層目の配線356、357の当該部分での断線はなかった。

なお、一般に図3(A)のようにゲイト絶縁膜を半分だけ残すということは難しく、図1 もしくは図3(B)のように完全に残すか、全く残さないかのいずれかの方が容易である

### [0036]

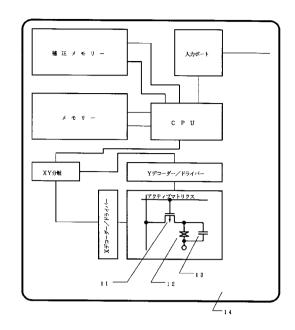

【実施例4】 本発明を用いて、アクティブマトリクス回路とその周辺駆動回路、さらには、CPU等の回路をも同一ガラス基板上に構成した例を示す。回路全体のブロック図を図6に示す。これらの回路を構成するTFTは全て同一基板14上に形成されている。図6において、11がアクティブマトリクス回路の一つの画素に設けられたTFTであり、12が画素電極、13が補助のキャパシタである。図6に示す構成においては、アクティブマトリクス回路の各画素に形成されるTFT11に加えてさらに入力ポート、補正メモリー、メモリー、CPU、XY分岐、Xデコーダー/ドライバー、Yデコーダー/ドライバー、の回路を構成するTFTを全て同一基板上に形成することを特徴とする。(図6)

図6において、入力ポートとは、外部から入力された信号を読み取り、画像用信号に変換し、補正メモリーは、アクティブマトリクスパネルの特性に合わせて入力信号等を補正するためのパネルに固有のメモリーのことである。特に、この補正メモリーは、各画素固有

20

30

50

の情報を不揮発性メモリーとして有し、個別に補正するためのものである。すなわち、電気光学装置の画素に点欠陥のある場合には、その点の周囲の画素にそれに合わせて補正した信号を送り、点欠陥をカバーし、欠陥を目立たなくする。または、画素が周囲の画素に比べて暗い場合には、その画素により大きな信号を送って、周囲の画素と同じ明るさとなるようにするものである。

#### [0038]

CPUとメモリーは通常のコンピュータのものとその機能は同様で、特にメモリーは各画素に対応した画像メモリーをRAMとして持っている。また、画像情報に応じて、基板を裏面から照射するバックライトを変化させることもできる。このような回路の断面の概略を図5に示す。

回路は、大きく分けてアクティブマトリクス回路(画素回路)の領域とアクティブマトリクス回路以外の周辺駆動回路、CPU、メモリー等の領域に分けられる。本実施例では、アクティブマトリクス回路以外の領域では、Nチャネル型TFT15とPチャネル型TFT16から構成される相補型回路を用いた。その作製方法は実施例2および図2に示されるものと同様である。また、アクティブマトリクス回路においてはTFTとしてはPチャネル型のTFT11を用いたが、その作製は上記の相補型回路におけるPチャネル型TFT作製と同時におこなわれた。(図5)

#### [0039]

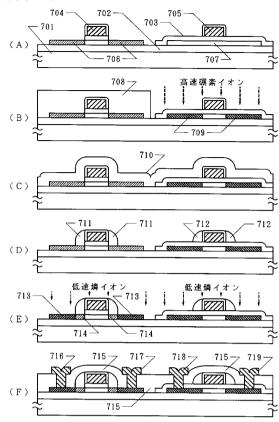

【実施例 5 】 図 7 に本実施例を示す。本実施例は実施例 2 と同様に同一基板上にLDD型のNチャネル型TFTと通常のPチャネル型TFTを形成する例である。図 7 の左側にはNチャネル型TFTの作製工程断面図を、また、同図の右側にはPチャネル型TFTの作製工程断面図を示す。まず、基板(コーニング 7 0 5 9 ) 7 0 1 上に下地酸化膜 7 0 2 、島状シリコン半導体領域、ゲイト酸化膜として機能する酸化珪素膜 7 0 3 を形成し、陽極酸化物によって表面の被覆されたアルミニウム膜(厚さ 5 0 0 0 )のゲイト電極 7 0 4、7 0 5 を形成した。

#### [0040]

さらに、Nチャネル型TFTの部分のゲイト酸化膜をゲイト電極704をマスクとして選択的に除去し、半導体層を露出せしめた。そして、ゲイト電極部をマスクとしてイオンドーピング法によって燐の注入をおこない、低濃度のN型不純物領域706を形成した。ドーズ量は1×10 $^{13}$ 原子/с $^{2}$  、加速電圧は20keVとした。このドーピング工程においては、加速電圧が低いため、ゲイト酸化膜703で被覆されているPチャネル型TFTの島状領域707には燐はドーピングされなかった。(図7(A))

#### [0041]

その後、N チャネル型 T F T の領域をフォトレジスト 7 0 8 でマスクし、この状態で、イオンドーピング法によって高濃度のホウ素のドーピングをおこなった。ドーズ量は  $5 \times 10^{14}$  原子 /  $10^{14}$  原子 / 1

なお、本実施例では、低濃度の燐の全面ドーピングの後に、高濃度のホウ素の部分選択ドーピングをおこなったが、この工程は逆にしてもよい。

フォトレジストのマスク 7 0 8 を除去した後、プラズマ C V D 法によって厚さ 4 0 0 0 ~ 40 8 0 0 0 の酸化珪素膜 7 1 0 を堆積した。(図 7 ( C ))

#### [0042]

そして、実施例 2 と同様に異方性エッチングによって、ゲイト電極の側面に酸化珪素のサイドウォール 7 1 1 、 7 1 2 を形成した。(図 7 ( D ) )

その後、再び、イオンドーピング法によって、燐を導入した。この場合のドーズ量は、図7(A)の工程のドーズ量より1~3桁多くなることが好ましい。本実施例では、最初の燐のドーピングのドーズ量の200倍の $2\times10^{15}$ 原子/cm²とした。加速電圧は20kVとした。この結果、高濃度の燐が導入された領域(ソース/ドレイン)713が形成され、また、サイドウォールの下部には低濃度不純物領域(LDD)714が残された。一方、Pチャネル型領域においては、ゲイト酸化膜が存在するため、燐イオンは注入され

なかった。実施例2では、Pチャネル型TFTでは燐もホウ素も高濃度に注入されるため、そのドーズ量の大小には制約があったが、本実施例では、ドーズ量に関する制約はない。ただし、加速電圧に関しては、上記のように、燐を低く、ホウ素を高くすることが必要である。(図7(E))

# [0043]

ドーピング工程の後、 K r F エキシマーレーザー (波長 2 4 8 n m、パルス幅 2 0 n s e c ) を照射して、ドーピングされた不純物の活性化をおこなった。レーザーのエネルギー密度は 2 0 0 ~ 4 0 0 m J / c m  $^2$  、好ましくは 2 5 0 ~ 3 0 0 m J / c m  $^2$  が適当であった。

最後に、図7(F)に示すように、全面に層間絶縁物715として、CVD法によって酸化珪素膜を厚さ5000 形成し、TFTのソース/ドレインにコンタクトホールを形成し、アルミニウム配線・電極716、717、718、719を形成した。以上の工程によって、Nチャネル型TFTがLDD型である半導体集積回路が完成された。

# [0044]

本実施例では、実施例 2 と比較すると、Nチャネル型TFTの部分のゲイト酸化膜を除去するために、フォトリソグラフィー工程およびエッチング工程が 1 つ余分に必要である。しかしながら、実質的にPチャネル型TFTにはN型不純物が導入されないので、N型、P型各不純物のドーズ量を比較的、任意に変更できるというメリットもある。

また、Pチャネル型TFTのゲイト酸化膜703の表面近傍に注入された燐は、後のレーザー照射工程によって、燐ガラスを形成し、ナトリウム等の可動イオンの侵入を防止するうえで効果がある。

# [0045]

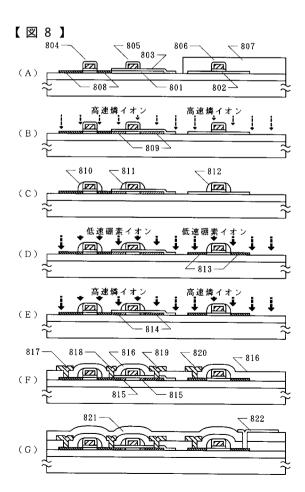

〔実施例 6 〕 図 8 に本実施例を示す。本実施例はアクティブマトリクス型液晶ディスプレーの作製方法に関し、図 8 を用いて説明する。図 8 の左側のTFT 2 つは、それぞれ、LDD型のNチャネル型TFT、通常型のPチャネル型TFTであり、周辺回路等に用いられる論理回路を示す。また、右側のTFTはアクティブマトリクスアレーに用いられるスイッチングトランジスタであり、オフセット型のPチャネル型TFTを示す。

まず、基板(コーニング 7 0 5 9)上に下地酸化膜、島状シリコン半導体領域(周辺回路用の島状領域 8 0 1、アクティブマトリクス回路用の島状領域 8 0 2)、ゲイト酸化膜として機能する酸化珪素膜 8 0 3 を形成し、さらに、陽極酸化物によって表面の被覆されたアルミニウム膜(厚さ 5 0 0 0 )のゲイト電極 8 0 4 、 8 0 5 (周辺回路用)、 8 0 6 (アクティブマトリクス回路用)を形成した。

#### [0046]

さらに、周辺回路用およびアクティブマトリクス回路用のPチャネル型TFTの部分のゲイト酸化膜をゲイト電極804、806をマスクとして選択的に除去し、半導体層を露出せしめた。さらに、アクティブマトリクス回路領域をフォトレジスト807でマスクした。そして、ゲイト電極部をマスクとしてイオンドーピング法によってホウ素の注入をおこない、高濃度のP型不純物領域808を形成した。ドーズ量は1×10 $^{15}$ 原子/cm²、加速電圧は20keVとした。このドーピング工程においては、加速電圧が低いため、ゲイト酸化膜803で被覆されているNチャネル型TFTの領域にはホウ素はドーピングされなかった。(図8(A))

# [0047]

その後、イオンドーピング法によって低濃度の燐のドーピングをおこなった。ドーズ量は $1 \times 1 \ 0^{13}$ 原子 /  $c \ m^2$  、加速電圧は $8 \ 0 \ k \ V$ とした。この結果、N チャネル型  $T \ F \ T \ O$  領域には低濃度のN 型不純物領域 $8 \ 0 \ 9$  が形成された。(図  $8 \ (B)$ )

なお、図面では、フォトレジストのマスク806を除去してドーピングしてあるが、フォトレジストをつけたままドーピングをおこなってもよい。燐の加速電圧は高いので、フォトレジストを残したままドーピングをおこなうと、燐がアクティブマトリクス回路領域に注入されないので、理想的なオフセット型のPチャネル型TFTが得られるが、ドーピングの結果、フォトレジストが炭化し、その除去に手間取ることがある。

ı

20

30

#### [0048]

フォトレジストを除去した場合にも、燐の加速電圧が高いため、燐の濃度は島状半導体領域の下においてピークを生じる。もっとも、完全に燐がドーピングされないという保証はなく、微量の燐が半導体領域に形成される。しかし、この場合に燐がドーピングされたとしても、その濃度は僅かであり、また、P<sup>+</sup> (ソース)/N<sup>-</sup> /I(チャネル)/N<sup>-</sup> /P<sup>+</sup> (ドレイン)という構造であり、リーク電流を減らすことが必要とされているアクティブマトリクス回路用のTFTとしてはうってつけである。

その後、プラズマCVD法によって厚さ4000~8000 の酸化珪素膜710を堆積し、実施例2と同様に異方性エッチングによって、ゲイト電極の側面に酸化珪素のサイドウォール810、811、812を形成した。(図8(C))

[0049]

その後、再び、イオンドーピング法によって、ホウ素を導入した。この場合のドーズ量は、図8(A)の工程のドーズ量と同程度となることが望ましい。本実施例では、ドーズ量は1 × 10 $^{15}$ 原子 / c m $^2$  、加速電圧は20 k e V とした。加速電圧が低いため、ゲイト酸化膜803の存在するNチャネル型TFTの領域にはホウ素はドーピングされず、主として、周辺回路およびアクティブマトリクス回路のPチャネル型TFTのソース / ドレインにドーピングされた。この結果、アクティブマトリクス回路のTFTのソース / ドレイン813が形成された。このTFTはゲイト電極とソース / ドレインが離れたオフセット構造となっている。(図8(D))

[0050]

次に、燐のドーピングをおこなった。この場合には、最初の燐のドーピング工程である、図8(B)のドーズ量より1~3桁多くなることが好ましい。本実施例では、最初の燐のドーピングのドーズ量の50倍の5×10<sup>14</sup>原子/cm²とした。加速電圧は80kVとした。この結果、高濃度の燐が導入された領域(ソース/ドレイン)814が形成され、また、サイドウォールの下部には低濃度不純物領域(LDD)815が残された。一方、Pチャネル型TFT領域においては、燐イオンの多くは下地膜に注入され、その導

電型に大きな影響を与えることはなかった。(図8(E))

[0051]

ドーピング工程の後、KrFエキシマーレーザー(波長248nm、パルス幅20nsec)を照射して、ドーピングされた不純物の活性化をおこなった。レーザーのエネルギー密度は200~400mJ/cm² が適当であった。

[0052]

そして、全面に第1の層間絶縁物816として、CVD法によって窒化珪素膜を厚さ500 形成し、TFTのソース/ドレインにコンタクトホールを形成し、アルミニウム配線・電極817、818、819、820を形成した。以上の工程によって、周辺回路領域が形成された。(図8(F))

さらに、第2の層間絶縁物821として、CVD法によって酸化珪素膜を厚さ3000 形成し、これをエッチングして、コンタクトホールを形成し、アクティブマトリクス回路のTFTに透明導電膜によって、画素電極822を形成した。このようにして、アクティブマトリクス型液晶ディスプレー基板を作製した。(図8(G))

[0053]

# 【発明の効果】

本発明によって、ゲイト配線乗り越え部における2層目配線の断線を削減することができるのは上記の通りである。特に集積回路は多数の素子、配線から構成されているのであるが、その中に1か所でも不良があると、全体が使用不能になる可能性がある。本発明によってこのような不良の数を大幅に削減できることは集積回路の良品率を高める上で非常に大きな効果を有することは言うまでもない。

### [0054]

また、本発明によって、2層目配線の厚さをゲイト電極・配線と同じ程度、具体的には、

10

20

40

50

ゲイト電極・配線 ± 1 0 0 0 〔 〕とすることも可能である。このことによる効果は大きく、これは、基板表面の凹凸の少ないことの要求される液晶ディスプレーのアクティブマトリクス回路には好適である。その他、本発明を使用することによって派生的に得られるメリットは「作用」の項で述べたとおりである。このように本発明はTFT集積回路の歩留りを向上させる上で著しく有益である。

#### 【図面の簡単な説明】

- 【図1】 実施例1によるTFT回路の作製方法を示す。

- 【図2】 実施例2によるTFT回路の作製方法を示す。

- 【図3】 実施例3によるTFT回路の作製方法を示す。

- 【図4】 従来法によるTFTの作製方法を示す。

- 【図5】 実施例4におけるTFT回路の断面の様子を示す。

- 【図6】 実施例4におけるTFT回路のブロック図を示す。

- 【図7】 実施例5によるTFT回路の作製方法を示す。

- 【図8】 実施例6によるTFT回路の作製方法を示す。

#### 【符号の説明】

| 1 | 0 | 1 | ガ | ラ | ス | 基板 |

|---|---|---|---|---|---|----|

|   |   |   |   |   |   |    |

- 102 下地酸化膜(酸化珪素)

- 103 島状シリコン領域(活性層)

- 104 ゲイト絶縁膜

- 105、106 ゲイト電極(アルミニウム)

- 107、108 陽極酸化物(酸化アルミニウム)

- 109 弱いN型不純物領域

- 110 絶緣物被膜(酸化珪素)

- 1 1 1 、 1 1 2 サイドウォール

- 113 LDD(低濃度不純物領域)

- 114 ソース/ドレイン

- 115 層間絶縁膜(酸化珪素)

- 116、117 金属配線・電極(アルミニウム)

10

【図6】

【図7】

# フロントページの続き

| (51) Int.CI. |         |           | FΙ      |       |         |

|--------------|---------|-----------|---------|-------|---------|

| H 0 1 L      | 27/092  | (2006.01) | H 0 1 L | 27/08 | 3 2 1 F |

| H 0 1 L      | 21/3205 | (2006.01) | H 0 1 L | 21/88 | K       |

| H 0 1 L      | 21/768  | (2006.01) | H 0 1 L | 21/90 | W       |

| H 0 1 L      | 23/522  | (2006.01) | H 0 1 L | 27/08 | 3 3 1 E |

| H 0 1 L      | 27/08   | (2006.01) | H 0 1 L | 29/78 | 613A    |

# (72)発明者 須沢 英臣

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

審査官 棚田 一也

(56)参考文献 特開平05-235350(JP,A) 特開昭64-007559(JP,A)

# (58)調査した分野(Int.CI., DB名)

H01L 21/336 G02F 1/1368 G09F 9/30 H01L 21/3205 H01L 21/768 H01L 21/8238 H01L 23/522 H01L 27/08 H01L 27/092

H01L 29/786