# (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2020-202640 (P2020-202640A)

(43) 公開日 令和2年12月17日(2020, 12, 17)

| (51) Int.Cl. |        |           | FI    |        |      | テーマコード(参  | 考) |

|--------------|--------|-----------|-------|--------|------|-----------|----|

| H02J         | 1/00   | (2006.01) | HO2J  | 1/00   | 308C | 5G165     |    |

| нозк         | 17/687 | (2006.01) | нозк  | 17/687 | A    | 5 J O 5 5 |    |

|              |        |           | HO2 J | 1/00   | 306L |           |    |

|                       |                                                     | 審査請求         | 未請求 請求項の数 4 OL (全 24 頁)                                  |

|-----------------------|-----------------------------------------------------|--------------|----------------------------------------------------------|

| (21) 出願番号<br>(22) 出願日 | 特願2019-107219 (P2019-107219)<br>令和1年6月7日 (2019.6.7) | (71) 出願人     | 591074736<br>宮城県<br>宮城県仙台市青葉区本町3丁目8番1号                   |

|                       |                                                     | (74) 代理人     | 100117341<br>弁理士 山崎 拓哉                                   |

|                       |                                                     | (74)代理人      | 100148840                                                |

|                       |                                                     | (74)代理人      | 100191673<br>弁理士 渡邊 久典                                   |

|                       |                                                     | (72) 発明者     | 小野 仁                                                     |

|                       |                                                     |              | 宮城県仙台市泉区明通二丁目2番地 宮城県産業技術総合センター内                          |

|                       |                                                     | F ターム (参<br> | 考) 5G165 BB02 CA01 DA04 EA01 KA01<br>LA01 MA09 NA01 NA10 |

|                       |                                                     |              | 最終頁に続く                                                   |

# (54) 【発明の名称】遮断回路

# (57)【要約】

【課題】蓄電回路に接続された負荷の安定的な動作を可 能にする機構を提供すること。

【解決手段】遮断回路70は、入力端72と、出力端7 8と、電源検知端74とを有している。遮断回路70の 出力端78は、蓄電回路30から供給された電力によっ て動作する負荷62に接続されている。遮断回路70は 、電源検知端74に印加された電圧が所定電圧以下であ る場合、出力端78を入力端72から遮断する一方、電 源検知端74に印加された電圧が所定電圧よりも大きい 場合、出力端78を入力端72と導通させる。

【選択図】図5

#### 【特許請求の範囲】

# 【請求項1】

入力端と、出力端と、電源検知端とを有する遮断回路であって、

前記遮断回路の前記出力端は、蓄電回路から供給された電力によって動作する負荷に接続されており、

前記電源検知端に印加された電圧が所定電圧以下である場合、前記出力端を前記入力端から遮断する一方、前記電源検知端に印加された電圧が前記所定電圧よりも大きい場合、前記出力端を前記入力端と導通させる遮断回路。

# 【請求項2】

請求項1記載の遮断回路であって、

前記蓄電回路は、電源から供給される電力を蓄積して前記負荷に供給する回路であって

前記蓄電回路は、電源ラインと、蓄電部と、制御部とを備えており、

前記電源ラインは、前記電源と前記負荷とを互いに接続しており、

前記蓄電部は、前記電源ラインに接続されており、前記電源から供給される前記電力を蓄積してゼロよりも大きな供給電圧を前記電源ラインに印加し、

前記制御部は、前記供給電圧がゼロからスタートして開始電圧に達するまで、前記負荷を前記蓄電部から遮断し、

前記制御部は、前記供給電圧が前記開始電圧に達した後、前記供給電圧が停止電圧に降下するまで、前記負荷を前記蓄電部と導通させ、前記供給電圧が前記停止電圧まで降下すると、前記供給電圧が再び前記開始電圧に達するまで、前記負荷を前記蓄電部から遮断し

前記遮断回路の前記電源検知端は、前記電源ライン上の検知点に直接的又は間接的に接続されている

遮断回路。

# 【請求項3】

請求項2記載の遮断回路であって、

前記検知点における電圧は、前記負荷が前記蓄電部から遮断されているとき、グランド電圧であり、前記負荷が前記蓄電部と導通しているとき、グランド電圧よりも高い電圧である

遮断回路。

#### 【請求項4】

請求項2又は請求項3記載の遮断回路であって、

前記蓄電回路は、スイッチ部を備えており、

前記スイッチ部は、前記電源ラインにおいて前記蓄電部と前記負荷との間に接続されており、

前記スイッチ部は、スイッチ端を有しており、

前記スイッチ部は、前記スイッチ端に印加された電圧が所定閾値よりも低い場合、前記負荷を前記蓄電部から遮断する遮断状態を取り、前記スイッチ端に印加された電圧が前記所定閾値よりも高い場合、前記負荷を前記蓄電部と導通させる導通状態を取り、

前記制御部は、前記電源ラインにおいて前記蓄電部と前記スイッチ部との間に接続されており、

前記制御部は、前記供給電圧がゼロからスタートして前記開始電圧に達するまで、前記スイッチ端に、前記所定閾値よりも低い電圧を印加し、

前記制御部は、前記供給電圧が前記開始電圧に達した後、前記供給電圧が前記停止電圧に降下するまで、前記スイッチ端に、前記所定閾値よりも高い電圧を印加し、前記供給電圧が前記停止電圧まで降下すると、前記供給電圧が再び前記開始電圧に達するまで、前記スイッチ端に、前記所定閾値よりも低い電圧を印加する遮断回路。

10

20

30

40

#### 【発明の詳細な説明】

【技術分野】

[0001]

本発明は、遮断回路に関する。

【背景技術】

[0002]

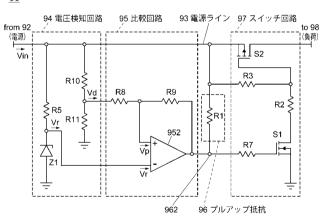

非特許文献1には、負荷に電力を供給する蓄電回路が開示されている。

[0003]

図13を参照すると、非特許文献1に開示された蓄電回路90は、電源92がエネルギーハーベスティングによって生成した微小な電力を蓄積して負荷98に供給する。蓄電回路90は、電源ライン93と、キャパシタ(図示せず)と、電圧検知回路94と、比較回路95と、抵抗R1からなるプルアップ抵抗96と、スイッチ回路97とを備えている。キャパシタは、電源ライン93に接続されている(図示せず)。電圧検知回路94、比較回路95、プルアップ抵抗96及びスイッチ回路97は、図13に示した回路構造を有している。例えば、電圧検知回路94は、ツェナー電圧VZを有するツェナーダイオードZ1を備えており、比較回路95は、オープンドレインのコンパレータ952を備えている。また、スイッチ回路97は、スイッチング素子S1とスイッチング素子S2とを備えている。

[0004]

キャパシタ(図示せず)は、電源92が生成した電力を蓄積し、これにより、電源ライン93に電圧Vinが生じる。電圧検知回路94は、電圧Vinとツェナー電圧Vzとに基づいて電圧Vrを生成すると共に、電圧Vinを分圧した電圧Vdを生成する。コンパレータ952のポジティブ入力端には、電圧Vdに応じた電圧Vpが印加され、コンパレータ952のネガティブ入力端には、電圧Vrが印加される。比較回路95は、電圧Vpと電圧Vrとの比較結果に基づいて生成した電圧を、スイッチング素子S1のゲートに印加された電圧に応じて、遮断状態(負荷98を電源92から遮断する状態)と、導通状態(負荷98を電源92に接続する状態)との間を遷移可能である。

[0005]

非特許文献1によれば、キャパシタ(図示せず)が空の状態において電源92が電力を生成すると、電力は、キャパシタに徐々に蓄積され、電圧Vin及び電圧Vpが徐々に高くなる。電圧Vpが電圧Vrに達するまで、蓄電回路90は遮断状態を維持し、電源92が生成した電力は、負荷98によって消費されることなく、キャパシタに蓄積される。キャパシタが十分に充電された後に、電圧Vpが電圧Vr以上になり、蓄電回路90は導通状態になる。このとき、十分に大きな電力が負荷98に供給される。

【先行技術文献】

【非特許文献】

[0006]

【非特許文献1】小野仁,外3名,「スイッチング回路を応用した省エネルギー・エネルギーハーベスティング技術の開発」,平成27年度 宮城県産業技術総合センター研究報告,宮城県(産業技術総合センター),平成28年9月,No.13(2015),p.1-7

【発明の概要】

【発明が解決しようとする課題】

[0007]

非特許文献 1 に開示された蓄電回路 9 0 は、理論的には上述したように動作する。しかしながら、実際に回路を構成して実験してみると、負荷 9 8 が安定的に動作しない場合がある。

[ 0 0 0 8 ]

10

20

30

40

そこで、本発明は、蓄電回路に接続された負荷の安定的な動作を可能にする機構を提供することを目的とする。

### 【課題を解決するための手段】

#### [0009]

本願発明者による研究の結果、蓄電回路の回路構造に起因して、キャパシタが十分に充電される前にスイッチ回路が導通状態になる場合があることが分かった。そこで、本願発明者は、スイッチ回路を遮断状態と導通状態との間で適切に遷移させることが可能な新たな蓄電回路を発明した。新たな蓄電回路は、特願2017-240693として国内出願済みである。

# [0010]

しかしながら、本願発明者による更なる研究の結果、上述の新たな蓄電回路を使用しても、負荷が安定的に動作しない場合があることが分かった。特に、蓄電回路以外の外部回路から電圧が印加されるような負荷(例えば、外部回路の電圧を測定するセンサ)を蓄電回路に接続した場合、負荷が安定的に動作しない場合があることが分かった。これは、蓄電回路が遮断状態にあるとき(即ち、負荷が動作していないとき)に外部回路から負荷に電圧が印加されると、負荷が予期しない動作を行うためであると考えられる。そこで、本発明は、動作していない負荷を外部回路から遮断可能な遮断回路を提供する。具体的には、本発明は、下記の遮断回路を提供する。

# [ 0 0 1 1 ]

本発明は、第1の遮断回路として、

入力端と、出力端と、電源検知端とを有する遮断回路であって、

前記遮断回路の前記出力端は、蓄電回路から供給された電力によって動作する負荷に接続されており、

前記電源検知端に印加された電圧が所定電圧以下である場合、前記出力端を前記入力端から遮断する一方、前記電源検知端に印加された電圧が前記所定電圧よりも大きい場合、前記出力端を前記入力端と導通させる

遮断回路を提供する。

#### [0012]

また、本発明は、第2の遮断回路として、第1の遮断回路であって、

前記蓄電回路は、電源から供給される電力を蓄積して前記負荷に供給する回路であって

前記蓄電回路は、電源ラインと、蓄電部と、制御部とを備えており、

前記電源ラインは、前記電源と前記負荷とを互いに接続しており、

前記蓄電部は、前記電源ラインに接続されており、前記電源から供給される前記電力を蓄積してゼロよりも大きな供給電圧を前記電源ラインに印加し、

前記制御部は、前記供給電圧がゼロからスタートして開始電圧に達するまで、前記負荷を前記蓄電部から遮断し、

前記制御部は、前記供給電圧が前記開始電圧に達した後、前記供給電圧が停止電圧に降下するまで、前記負荷を前記蓄電部と導通させ、前記供給電圧が前記停止電圧まで降下すると、前記供給電圧が再び前記開始電圧に達するまで、前記負荷を前記蓄電部から遮断し

前記遮断回路の前記電源検知端は、前記電源ライン上の検知点に直接的又は間接的に接続されている

遮断回路を提供する。

#### [ 0 0 1 3 ]

また、本発明は、第3の遮断回路として、第2の遮断回路であって、

前記検知点における電圧は、前記負荷が前記蓄電部から遮断されているとき、グランド電圧であり、前記負荷が前記蓄電部と導通しているとき、グランド電圧よりも高い電圧である

遮断回路を提供する。

10

20

30

40

#### [0014]

また、本発明は、第4の遮断回路として、第2又は第3の遮断回路であって、

前記蓄電回路は、スイッチ部を備えており、

前記スイッチ部は、前記電源ラインにおいて前記蓄電部と前記負荷との間に接続されており、

前記スイッチ部は、スイッチ端を有しており、

前記スイッチ部は、前記スイッチ端に印加された電圧が所定閾値よりも低い場合、前記負荷を前記蓄電部から遮断する遮断状態を取り、前記スイッチ端に印加された電圧が前記所定閾値よりも高い場合、前記負荷を前記蓄電部と導通させる導通状態を取り、

前記制御部は、前記電源ラインにおいて前記蓄電部と前記スイッチ部との間に接続されており、

前記制御部は、前記供給電圧がゼロからスタートして前記開始電圧に達するまで、前記スイッチ端に、前記所定閾値よりも低い電圧を印加し、

前記制御部は、前記供給電圧が前記開始電圧に達した後、前記供給電圧が前記停止電圧に降下するまで、前記スイッチ端に、前記所定閾値よりも高い電圧を印加し、前記供給電圧が前記停止電圧まで降下すると、前記供給電圧が再び前記開始電圧に達するまで、前記スイッチ端に、前記所定閾値よりも低い電圧を印加する遮断回路を提供する。

# [0015]

また、本発明は、第5の遮断回路として、第2又は第3の遮断回路であって、

前記蓄電回路は、前記蓄電部として機能するキャパシタと、スイッチ回路とを備えており、

前記蓄電回路の前記制御部は、電圧検知回路と、比較回路と、付加的回路とを含んでおり、

前記電圧検知回路は、前記電源ラインに接続された検知入力端と、参照電圧を出力する 参照出力端と、検知電圧を出力する検知出力端とを有しており、

前記参照電圧は、前記供給電圧が基準電圧よりも低い場合、前記供給電圧であり、前記供給電圧が前記基準電圧以上の場合、前記基準電圧であり、

前記検知電圧は、前記供給電圧に応じて変化し、且つ、前記供給電圧よりも低く、

前記比較回路は、前記電源ラインに接続されており、且つ、前記参照出力端に接続されたポジティブ入力端と、前記検知出力端に接続されたネガティブ入力端と、付加的制御電圧を出力する出力端とを有しており、

前記付加的制御電圧は、前記ポジティブ入力端に印加された電圧が前記ネガティブ入力端に印加された電圧よりも高い場合、前記供給電圧に応じた高電圧であり、前記ポジティブ入力端に印加された前記電圧が前記ネガティブ入力端に印加された前記電圧よりも低い場合、グランド電圧に応じた低電圧であり、

前記付加的回路は、前記電源ラインに接続された電源端と、グランドされたグランド端とを有しており、前記電源端と前記グランド端との間を遮断する非グランド状態と、前記電源端を前記グランド端と導通させるグランド状態との間を遷移可能であり、

前記スイッチ回路は、前記電源ラインにおいて前記キャパシタと前記負荷との間に接続されており、前記負荷を前記キャパシタから遮断する遮断状態と、前記負荷を前記キャパシタと導通させる導通状態との間を遷移可能であり、

前記付加的回路は、前記比較回路の前記出力端に接続された付加的入力端と、制御電圧を出力するスイッチ制御端とを有しており、

前記制御電圧は、前記付加的回路が前記非グランド状態にある場合、前記供給電圧に応じた高電圧であり、前記付加的回路が前記グランド状態にある場合、前記グランド電圧に応じた低電圧であり、

前記付加的回路は、前記供給電圧がゼロから上昇して、前記付加的制御電圧に応じて前記付加的入力端に印加された付加的印加電圧が付加的閾値に達するまでは、前記非グランド状態を取り、前記付加的印加電圧が前記付加的閾値に達した以降は、前記付加的印加電

10

20

30

40

圧が前記付加的閾値よりも高い場合、前記グランド状態を取り、前記付加的印加電圧が前記付加的閾値よりも低い場合、前記非グランド状態を取り、

前記スイッチ回路は、前記スイッチ制御端に接続されたスイッチ端を有しており、

前記スイッチ回路は、前記供給電圧がゼロから上昇して、前記制御電圧に応じて前記スイッチ端に印加された印加電圧が所定閾値に達するまでは、前記遮断状態を取り、前記印加電圧が前記所定閾値よりも高い場合、前記導通状態を取り、前記印加電圧が前記所定閾値よりも低い場合、前記遮断状態を取り、

前記供給電圧がゼロから上昇して前記付加的印加電圧が前記付加的閾値に達するまで、前記印加電圧は、前記所定閾値よりも低い

蓄電回路を提供する。

# [0016]

また、本発明は、第6の遮断回路として、第5の遮断回路であって、

前記付加的回路の前記電源端は、前記電源ラインに接続されると共に、前記電圧検知回路の前記検知出力端に接続されており、

前記制御電圧は、前記付加的回路が前記非グランド状態にある場合、前記検知電圧に応じた高電圧である

蓄電回路を提供する。

#### [ 0 0 1 7 ]

また、本発明は、第7の遮断回路として、第6の遮断回路であって、

前記付加的回路は、N型MOSFET (metal-oxide-semiconductor field-effect transistor)からなる付加的スイッチング素子を備えており、

前記付加的スイッチング素子において、ゲートは、前記付加的入力端として機能し、ソースは、前記グランド端として機能し、ドレインは、前記電源端として機能し、且つ、前記電圧検知回路の前記検知出力端と前記スイッチ回路の前記スイッチ端との間に接続されており、

前記付加的閾値は、前記付加的スイッチング素子において前記ソースと前記ドレインとの間を導通させるための前記ゲートと前記ソースとの間の電位差の閾値であり、

前記スイッチ回路は、P型MOSFETからなる主スイッチング素子と、N型MOSFETからなる副スイッチング素子とを備えており、

前記主スイッチング素子において、ソースは、前記電源ラインの前記電源側に接続されており、ドレインは、前記電源ラインの前記負荷側に接続されており、

前記副スイッチング素子において、ゲートは、前記スイッチ端として機能し、ソースは、グランドされており、ドレインは、2つの抵抗を介して前記主スイッチング素子の前記 ソースに接続されており、

前記主スイッチング素子のゲートは、前記2つの抵抗の間に接続されており、

前記所定閾値は、前記副スイッチング素子において前記ソースと前記ドレインとの間を 導通させるための前記ゲートと前記ソースとの間の電位差の閾値である 蓄電回路を提供する。

# [0018]

また、本発明は、第8の遮断回路として、第5から第7までの遮断回路のいずれかであって、

前記所定閾値は、前記付加的閾値以上である

蓄電回路を提供する。

# 【発明の効果】

### [0019]

本発明の遮断回路によれば、電源検知端に印加された電圧が所定電圧以下である場合、入力端と出力端との間が遮断される。また、本発明の遮断回路の出力端は、蓄電回路から供給された電力によって動作する負荷に接続されている。例えば、負荷は、外部回路によって負荷の測定端に印加された電圧を測定するセンサである。この場合、遮断回路の入力端を外部回路に接続し、遮断回路の出力端をセンサの測定端に接続すればよい。この構成

10

20

30

40

によれば、センサが蓄電回路から受ける電圧を遮断回路の電源検知端に印加することで、蓄電回路が遮断状態にあるとき(即ち、センサが動作していないとき)、センサは、外部回路から遮断される。即ち、本発明によれば、動作していない負荷を外部回路から遮断可能な遮断回路を提供でき、これにより、蓄電回路に接続された負荷の安定的な動作を可能にする機構を提供できる。

# 【図面の簡単な説明】

- [0020]

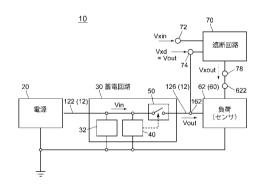

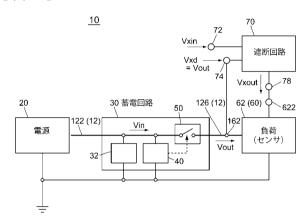

- 【図1】本発明の実施の形態による蓄電型システムを示すブロック図である。

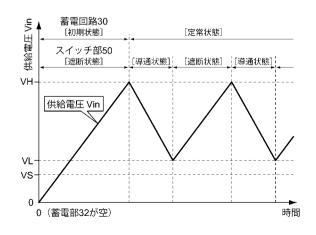

- 【図2】図1の蓄電型システムの蓄電回路の動作を模式的に示す図である。

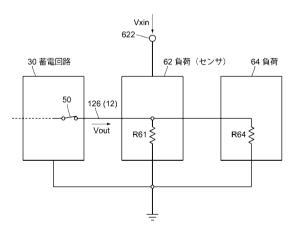

- 【図3】図1の蓄電回路のスイッチ部が導通状態にあるときの負荷(センサ)の回路構造を模式的に示す図である。

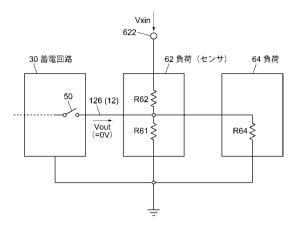

- 【図4】図1の蓄電回路のスイッチ部が遮断状態にあるときの負荷(センサ)の回路構造を模式的に示す図である。

- 【 図 5 】 図 1 の 蓄 電 型 シ ス テ ム を 遮 断 回 路 を 設 け た 状 態 で 示 す ブ ロ ッ ク 図 で あ る 。

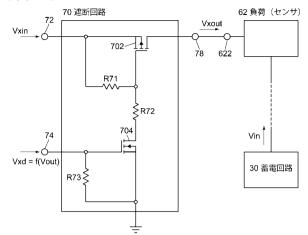

- 【図6】図5の遮断回路を示す回路図である。

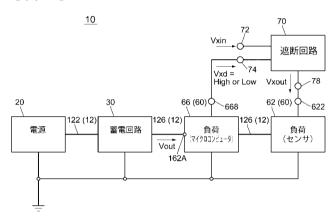

- 【図7】図5の蓄電型システムの変形例を示すブロック図である。

- 【図8】図6の遮断回路の変形例を示す回路図である。

- 【図9】図1の蓄電回路の一例を示すブロック図である。

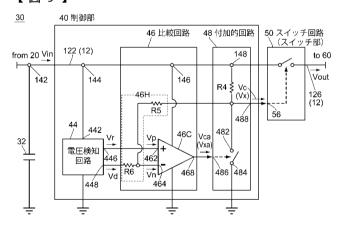

- 【図10】図9の蓄電回路の一例を示す回路図である。

- 【図11】図9及び図10の蓄電回路の動作を模式的に示す図である。

- 【図12】本発明の実施例の蓄電回路の動作を示す図である。

- 【図13】非特許文献1の蓄電回路を示す回路図である。

- 【発明を実施するための形態】

- [ 0 0 2 1 ]

図 1 を参照すると、本発明の実施の形態による蓄電型システム 1 0 は、電源 2 0 と、蓄電回路 3 0 と、負荷 6 0 とを備えている。

[0022]

本実施の形態の電源 2 0 は、周囲の環境から微小なエネルギーを収穫することで(即ち、エネルギーハーベスティングによって) 1 0 µW ~ 1 mW程度の微小な電力を生成し、且つ、微小な電圧を生成する。電源 2 0 は、例えば、光電池、熱電素子、整流後の振動発電体等の発電体である。電源 2 0 は、上述した発電体のうちの 1 つであってもよいし、上述した発電体を 2 以上含んでいてもよい。

[0023]

本実施の形態の負荷60は、例えば、昇圧型DC-DCコンバータ、降圧型DC-DCコンバータ、昇降圧型DC-DCコンバータ(以下、「DC-DCコンバータ」と総称する。)、センサ、マイクロコンピュータ、無線デバイス等の半導体素子を含む電子機器や、小型モーター等の動作開始時に一定以上の電圧を必要とする電子機器である。負荷60は、上述した電子機器のうちの1つであってもよいし、上述した電子機器を2以上含んでいてもよい。

[0024]

本実施の形態の蓄電回路30は、蓄電装置(図示せず)に組み込まれた回路である。本実施の形態の蓄電装置は、電源20及び負荷60と別体の電子機器である。但し、本発明は、これに限られない。例えば、蓄電装置は、電源20、蓄電回路30及び負荷60を備えた1つの電子機器であってもよい。また、蓄電回路30は、負荷60に組み込まれた回路であってもよい。

[ 0 0 2 5 ]

本実施の形態の負荷60は、使用時に、動作状態と待機状態との間を繰り返し遷移する。負荷60の待機状態における消費電力は、動作状態における消費電力と比較して著しく低い。一方、負荷60の動作状態における消費電力(動作電力)は、数mW~数W程度であり、電源20が直接的に供給可能な電力よりも大きい。このため、負荷60を電源20

20

10

30

30

40

に直接接続すると、電源20は電圧降下を起こし、電源20の電圧は、負荷60を適切に動作させるための電圧(動作開始電圧VS)に到達しない。

# [0026]

一方、以下に説明するように、本実施の形態の蓄電回路30は、電源20が生成する微小な電力(静電エネルギー)を蓄積し、電力が十分に蓄積された段階で、必要な高電圧によって、負荷60に電力を供給する。但し、本発明は、これに限られない。例えば、蓄電回路30は、負荷60に直接供給可能な高い電力及び電圧を生成する電源20に接続してもよい。

# [0027]

本実施の形態の蓄電回路30は、上述したように、電源20から供給される電力を蓄積して負荷60に供給する回路であり、電源ライン12と、蓄電部(キャパシタ)32と、制御部40と、スイッチ部(スイッチ回路)50とを備えている。以下、蓄電回路30の各部位の構造及び機能について説明する。

# [0028]

蓄電回路30の電源ライン12は、電源20と負荷60とを互いに接続している。詳しくは、電源ライン12は、入力側電源ライン(電源ライン)122と、出力側電源ライン(電源ライン)120とを含んでいる。電源ライン122は、電源20とスイッチ部50の一端とを互いに接続しており、電源ライン126は、スイッチ部50の他端と負荷60とを互いに接続している。換言すれば、スイッチ部50は、電源ライン122と電源ライン126との間に設けられている。即ち、電源20及び負荷60は、電源ライン12によってスイッチ部50を介して互いに接続されている。

#### [0029]

蓄電回路30のスイッチ部50は、上述したように、電源ライン12において蓄電部32と負荷60との間に接続されている。また、スイッチ部50は、スイッチ端56を有している。スイッチ部50は、スイッチ端56に印加された印加電圧Vxが所定の電圧値(所定閾値TP)よりも低い場合、負荷60を電源20から遮断する遮断状態を取り、スイッチ端56に印加された印加電圧Vxが所定閾値TPよりも高い場合、負荷60を電源20に導通させる導通状態を取る。即ち、スイッチ部50は、印加電圧Vxに応じて、遮断状態と、導通状態との間を遷移可能である。スイッチ部50は、電源20が蓄電回路30に電力を供給し始めた時点において遮断状態にある。

### [0030]

上述のように遮断状態と導通状態との間を遷移するスイッチ部 5 0 は、P型MOSFET (metal-oxide-semiconductor field-effect transistor)、N型MOSFET等の電子部品を使用して構成できる。所定閾値TPは、例えば、MOSFETにおいてソースとドレインとの間を導通又は遮断させるためのゲートとソースとの間の電位差の閾値(以下、単に「ゲート閾値」という。)である。

# [0031]

蓄電回路30の蓄電部32は、電源ライン122(電源ライン12)に接続されている。従って、スイッチ部50が遮断状態にあるとき、蓄電部32は、負荷60から遮断されている。一方、スイッチ部50が導通状態にあるとき、蓄電部32は、負荷60と導通している。

#### [0032]

蓄電部32は、電源20から供給される微小な電力を蓄積してゼロよりも大きな供給電圧 Vinを電源ライン122(電源ライン12)に印加する。スイッチ部50が遮断状態にあるとき、供給電圧 Vinは、蓄電部32に電力が蓄積されるにつれて、負荷60の動作開始電圧 VSを超えて上昇する。蓄電回路30は、スイッチ部50を所定時間だけ遮断状態にすることで、負荷60を動作させるための十分な静電エネルギーを蓄電部32に蓄積できる。加えて、蓄電回路30は、蓄電部32に十分な静電エネルギーが蓄積されたとき、スイッチ部50を導通状態にする。スイッチ部50が導通状態になると、負荷60の動作開始電圧 VSよりも高い出力電圧 Voutによって負荷60に電力が供給される。供

10

20

30

40

10

20

30

40

50

給電圧Vinは、負荷60に電力が供給されるにつれて、徐々に降下する。

# [0033]

上述のように電力を蓄積する蓄電部32は、例えば、1つのコンデンサから構成できる。但し、本発明は、これに限られない。例えば、蓄電部32は、2以上のコンデンサから構成されていてもよいし、コンデンサ以外の電子部品を含んでいてもよい。蓄電部32が2以上のコンデンサを含んでいる場合、コンデンサ間の接続方法は特に限定されない。また、蓄電部32は、電解コンデンサ、セラミックコンデンサ、電気二重層コンデンサ等の様々なコンデンサから構成可能である。

# [0034]

蓄電回路30の制御部40は、電源ライン122(電源ライン12)に接続されている。詳しくは、制御部40は、電源ライン122において蓄電部32とスイッチ部50との間に接続されており、これにより供給電圧Vinを検知可能である。加えて、制御部40は、スイッチ部50のスイッチ端56に接続されており、スイッチ端56に印加電圧Vxを印加する。

### [0035]

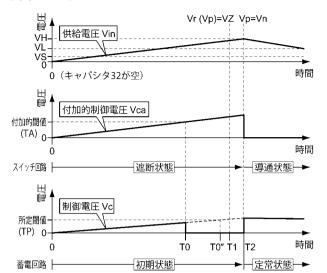

図 2 を図 1 と併せて参照すると、制御部 4 0 は、印加電圧 V x によってスイッチ部 5 0 を制御して、遮断状態と導通状態との間で遷移させる。

#### [0036]

本実施の形態において、制御部40は、供給電圧Vinがゼロからスタートして動作開始電圧VSよりも十分に大きな開始電圧VHに達するまで、スイッチ端56に、所定閾値TPよりも低い電圧を印加電圧Vxとして印加する。即ち、制御部40は、供給電圧Vinがゼロからスタートして開始電圧VHに達するまで、スイッチ部50を遮断状態に維持し、これにより負荷60を蓄電部32から遮断する。

#### [ 0 0 3 7 ]

制御部40は、供給電圧Vinが開始電圧VHに達した後、供給電圧Vinが開始電圧VHよりも小さく且つ動作開始電圧VSよりも大きな停止電圧VLに降下するまで、スイッチ端56に、所定閾値TPよりも高い電圧を印加電圧Vxとして印加する。即ち、制御部40は、供給電圧Vinが開始電圧VHに達すると、スイッチ部50を遮断状態から導通状態に遷移させる。制御部40は、供給電圧Vinが開始電圧VHに達した後、供給電圧Vinが停止電圧VLに降下するまで、スイッチ部50を導通状態に維持し、これにより負荷60を蓄電部32と導通させる。

# [0038]

制御部40は、供給電圧Vinが停止電圧VLまで降下すると、供給電圧Vinが再び開始電圧VHに達するまで、スイッチ端56に、所定閾値TPよりも低い電圧を印加電圧Vxとして印加する。即ち、制御部40は、供給電圧Vinが停止電圧VLまで降下すると、スイッチ部50を導通状態から遮断状態に遷移させる。制御部40は、供給電圧Vinが停止電圧VLまで降下すると、供給電圧Vinが再び開始電圧VHに達するまで、スイッチ部50を遮断状態に維持し、これにより負荷60を蓄電部32から遮断する。

# [0039]

上述のように動作する制御部40は、オープンドレインのコンパレータ、P型MOSFET、N型MOSFET等の電子部品を使用して構成できる。

#### [0040]

上述のように構成された蓄電回路30は、供給電圧Vinがゼロからスタートして最初に開始電圧VHに達するまで、初期状態にある。蓄電回路30が初期状態にあるとき、制御部40は、スイッチ部50を、遮断状態に維持する。蓄電回路30は、スイッチ部50が最初に導通状態に遷移したときに定常状態になり、以降、電源20から電力が供給され続けている限り、定常状態を維持する。蓄電回路30が定常状態にあるとき、制御部40は、スイッチ部50を、導通状態と遮断状態との間で繰り返し遷移させる。

# [ 0 0 4 1 ]

以上の説明から理解されるように、スイッチ部50が導通状態にあるとき、負荷60に

10

20

30

40

50

は、動作開始電圧 V S よりも高い出力電圧 V o u t によって電力が供給される。この結果、負荷 6 0 は、動作状態又は待機状態をとり、適切に動作する。一方、スイッチ部 5 0 が 遮断状態にあるとき、負荷 6 0 には、電力が供給されない。この結果、負荷 6 0 は、停止状態をとり、動作しない。負荷 6 0 は、理論的には、上述したように安定的に動作するはずである。

# [0042]

しかしながら、図13を参照すると、実際に蓄電型システムを構成して実験すると、負荷98が安定的に動作しない場合がある。この現象について研究を進めた結果、従来の蓄電回路90の回路構造に起因して、蓄電部(図13に図示しないキャパシタ)が十分に充電される前にスイッチ回路97(スイッチ部)が導通状態になる場合があることが分かった。図1、図9及び図10を参照すると、本実施の形態の蓄電回路30は、以上の考察に基づいて発明されたものであり、スイッチ部50を遮断状態と導通状態との間で適切に遷移させることができる。この蓄電回路30の回路構造に係る発明は、特願2017・240693として国内出願済みである。

# [0043]

しかしながら、実際に蓄電回路30を構成して実験すると、蓄電回路30を使用しても、負荷60が安定的に動作しない場合があることが分かった。図3を参照すると、特に、蓄電回路30以外の外部回路(図示せず)から電圧が印加されるような負荷62(例えば、外部回路の電圧を測定するセンサ62)を蓄電回路30に接続した場合、負荷62が安定的に動作しない場合があることが分かった。この原因は、スイッチ部50が遮断状態にあるとき(即ち、負荷62が動作していないとき)に外部回路から負荷62に電圧が印加されると、負荷62が予期しない動作を行うためであると考えられる。

# [0044]

以下、図3及び図4を参照しつつ、蓄電回路30に負荷62及び負荷64を接続した場合について、負荷62が安定的に動作しない原因を説明する。本実施の形態の負荷62は、外部回路(図示せず)の電圧を測定するセンサ62であり、設計に応じて形成される抵抗R61と、外部回路に接続される測定端622とを有している。測定端622は、負荷62が動作状態や待機状態にあるとき、ハイインピーダンス状態にあるか、又は、ハイインピーダンス状態に近い状態にある。換言すれば、本実施の形態の負荷62は、動作状態及び待機状態においてハイインピーダンス状態又はハイインピーダンス状態に近い状態をとる測定端622を有するセンサである。一方、本実施の形態の負荷64は、DC-DCコンバータ64であり、設計に応じて形成される抵抗R64を有している。但し、負荷64は、マイクロコンピュータ等のDC-DCコンバータ以外の電子機器であってもよい。

# [0045]

図3を参照すると、負荷62の測定端622には、外部回路の測定電圧V×inが印加される。蓄電回路30のスイッチ部50が導通状態にあるとき、負荷62及び負荷64の夫々は、動作状態又は待機状態にある。このとき、測定端622は、ハイインピーダンス状態又はハイインピーダンス状態に近い状態にあるため、電源ライン126(電源ライン12)から実質的に遮断されている。詳しくは、外部回路から測定端622に流れる電流は、例えば、負荷62のA/D変換のためだけに使用される。従って、外部回路から測定端622に流れる電流は、負荷62及び負荷64の夫々の動作を阻害しない。

#### [0046]

一方、図4を参照すると、蓄電回路30のスイッチ部50が遮断状態にあるとき、負荷62及び負荷64の夫々は、停止状態にある。このとき、負荷62の測定端622が、ハイインピーダンス状態にない場合がある。より具体的には、負荷62の回路構造に起因して、測定端622と電源ライン126(電源ライン12)との間に、予期しない抵抗R62が形成される場合がある。即ち、測定端622が、抵抗R62を介して、電源ライン126と導通する場合がある。この場合、外部回路(図示せず)から測定端622に流れる電流は、負荷62の回路を流れ、これにより負荷62の動作を阻害するおそれがある。また、外部回路から測定端622に流れる電流は、電源ライン126を経由して負荷64に

流入するおそれがある。

# [0047]

一般的に、負荷62及び負荷64を含む負荷60(図1参照)が停止状態にあるとき、電源ライン126を経由しない電流が負荷60に流入すると、負荷60が、誤動作したり故障したりするおそれがある。加えて、負荷62の測定端622に接続された外部回路(外部機器:図示せず)の電流が奪われる。この結果、外部機器の消費電流が増加したり外部機器が故障したりするおそれがある。

# [0048]

一方、図5を参照すると、本実施の形態の蓄電型システム10は、電源20、蓄電回路30及び負荷60に加えて、遮断回路70を備えている。負荷60は、1以上の負荷(センサ)62を含んでいる。即ち、図5に示した蓄電型システム10は、負荷60の一つとしてセンサ62を備えたセンサシステムである。負荷62の夫々は、遮断回路70を介して外部回路(図示せず)に接続されている。外部回路のグランド電圧は、蓄電型システム10のグランド電圧と一致している。以下に説明するように、このような蓄電型システム10(センサシステム)において、遮断回路70を設けることで、負荷62を含む負荷60の夫々を安定的に動作させることができる。

# [0049]

図6を参照すると、遮断回路70は、入力端72と、出力端78と、電源検知端74とを有している。遮断回路70の入力端72は、外部回路(図示せず)に接続されている。このように接続された入力端72には、外部回路の測定電圧Vxinが印加される。遮断回路70の出力端78は、蓄電回路30から供給された電力によって動作する負荷62に接続されている。詳しくは、出力端78は、負荷62の測定端622に接続されている。このように接続された出力端78は、測定端622に、測定電圧Vxinと実質的に同電圧の測定電圧Vxoutを印加する。

#### [0050]

図5を参照すると、遮断回路70の電源検知端74は、電源ライン126(電源ライン12)の検知点162に接続されている。このように接続された電源検知端74には、出力電圧 Voutに応じた検出電圧 Vxdが印加される。本実施の形態によれば、蓄電回路30のスイッチ部50が導通状態にあるとき、負荷62の動作開始電圧 VSよりも高い出力電圧 Voutが電源検知端74に印加される。一方、図3及び図4から理解されるように、スイッチ部50が遮断状態になると、電源ライン126は、速やかにグランドされ、これにより、グランド電圧である出力電圧 Voutが電源検知端74に印加される。

#### [ 0 0 5 1 ]

図6を参照すると、本実施の形態の遮断回路70は、P型MOSFETからなる第1素子702と、N型MOSFETからなる第2素子704と、3つの抵抗R71,R72,R73とを備えている。第1素子702、第2素子704及び抵抗R71,R72,R73は、図6に示したように接続されている。

# [0052]

本実施の形態によれば、第2素子704のゲートに検出電圧V×dが印加される。検出電圧V×dが第2素子704のゲート閾値よりも低い場合、第2素子704のソースとドレインとの間が遮断され、第1素子702のゲートに、第1素子702のソースと同じ電位の電圧が印加される。この結果、第1素子702のソースとドレインとの間が遮断される。即ち、遮断回路70の入力端72と出力端78との間が遮断される。

# [ 0 0 5 3 ]

一方、検出電圧 V x d が第 2 素子 7 0 4 のゲート閾値よりも高い場合、第 2 素子 7 0 4 のソースとドレインとの間が導通し、第 1 素子 7 0 2 のゲートは、抵抗 R 7 2 を介してグランドされる。この結果、第 1 素子 7 0 2 のゲートに印加される電圧が、第 1 素子 7 0 2 のソースに印加される電圧よりも低くなる。従って、抵抗 R 7 1 及び抵抗 R 7 2 の抵抗値を、第 1 素子 7 0 2 のゲート閾値を考慮して適切に設定することで、第 1 素子 7 0 2 のソースとドレインとの間が導通する。即ち、遮断回路 7 0 の入力端 7 2 と出力端 7 8 との間

10

20

30

40

が導通する。

# [0054]

以上の説明から理解されるように、遮断回路70は、電源検知端74に印加された電圧が所定電圧VP以下である場合、出力端78を入力端72から遮断する一方、電源検知端74に印加された電圧が所定電圧VPよりも大きい場合、出力端78を入力端72と導通させる。本実施の形態において、所定電圧VPは、第2素子704のゲート閾値である。但し、本発明は、これに限られず、所定電圧VPは、遮断回路70の回路構造に応じて決まる。

# [0055]

図5を参照すると、遮断回路70によれば、電源検知端74に印加された検出電圧Vxdが所定電圧VP以下である場合、入力端72と出力端78との間が遮断される。また、前述したように、遮断回路70の出力端78は、負荷62に接続されている。負荷62は、外部回路(図示せず)によって負荷62の測定端622に印加された電圧を測定するセンサ62である。

### [0056]

本実施の形態によれば、負荷62が蓄電回路30から受ける電圧を遮断回路70の電源検知端74に印加することで、蓄電回路30のスイッチ部50が遮断状態にあるとき(即ち、負荷62が停止状態にあり動作していないとき)、負荷62は、外部回路(図示せず)から遮断される。即ち、本発明によれば、動作していない負荷62を外部回路から遮断可能な遮断回路70を提供でき、これにより、蓄電回路30に接続された負荷62の安定的な動作を可能にする機構を提供できる。

#### [0057]

詳しくは、負荷62が停止状態にあるとき、外部回路(図示せず)から遮断回路70に流れる電流は、負荷62まで流れないため、負荷62や負荷64(図4参照)等の負荷60の動作を阻害しない。また、外部回路からの電流に起因する負荷60の誤動作や故障が防止される。加えて、外部回路(外部機器)の消費電流の増加や外部機器の故障が防止される。

#### [0058]

本実施の形態の電源20は、周囲の環境に依存して電力を生成するため、長時間にわたって蓄電部32に電力が供給されない場合がある。この場合、蓄電部32が生成する供給電圧Vinは、比較的0Vになり易い。このような蓄電型システム10において、遮断回路70は特に必要である。但し、本発明は、これに限られず、遮断回路70は、様々な蓄電型システムに適用可能である。例えば、遮断回路70は、従来の蓄電型システムに適用してもよい。

# [0059]

本実施の形態によれば、遮断回路70の電源検知端74は、電源ライン126上の検知点162に直接的に接続されている。検知点162における電圧は、負荷60が蓄電部32から遮断されているとき、グランド電圧であり、負荷60が蓄電部32と導通しているとき、グランド電圧よりも高い出力電圧Voutである。この構造によれば、遮断回路70の回路構造を簡易にできる。但し、本発明は、これに限られず、電源検知端74の接続方法は、様々に変形可能である。

# [0060]

例えば、電源検知端74が接続される検知点162は、電源ライン122上に位置していてもよい。但し、この接続方法によれば、遮断回路70は、検知点162における電圧が降下中である場合にのみ、入力端72と出力端78との間が導通するような回路構造を有する必要がある。この結果、遮断回路70の回路構造は複雑になる。従って、特に必要性がない限り、この接続方法に比べて本実施の形態の接続方法が好ましい。

#### [0061]

図 7 を参照すると、図示した負荷 6 0 は、負荷 (センサ) 6 2 に加えて、負荷 (マイクロコンピュータ) 6 6 を含んでいる。負荷 6 6 は、制御端 6 6 8 を有している。負荷 6 6

10

20

30

40

の制御端668は、電源ライン126上の検知点162Aの電圧がグランド電圧よりも高い場合、遮断回路70の所定電圧VPよりも高い電圧(High)を出力し、検知点162Aの電圧がグランド電圧である場合、遮断回路70の所定電圧VPよりも低い電圧(Low)を出力する。即ち、負荷66は、検知点162Aの電圧に応じて、High及びLowのうちのいずれか一方を制御端668に出力する。遮断回路70の電源検知端74は、負荷66の制御端668に接続されている。遮断回路70の入力端72は、外部回路(図示せず)に接続されており、遮断回路70の出力端78は、負荷62の測定端622に接続されている。

# [0062]

図7の遮断回路70の電源検知端74は、負荷66の制御端668に接続されている。従って、電源検知端74は、負荷66を介して電源ライン126上の検知点162Aに間接的に接続されている。この接続構造によっても、負荷62が蓄電部32から遮断されているとき、負荷62の測定端622を外部回路(図示せず)から確実に遮断できる。また、この接続構造によれば、負荷62による測定が実際に行われる場合にのみ制御端668にHighが出力されるように、負荷66を設定できる。図6を参照すると、この設定によれば、遮断回路70の抵抗R73による電力消費を削減できる。

# [0063]

遮断回路70の回路構造は、様々に変形可能である。例えば、図8を参照すると、変形例による遮断回路70Aは、遮断回路70(図6参照)の部品に加えて、2つの抵抗R74,R75を備えている。遮断回路70Aは、遮断回路70と同様に、電源検知端74に印加された電圧が所定電圧VP以下である場合、出力端78を入力端72から遮断する一方、電源検知端74に印加された電圧が所定電圧VPよりも大きい場合、出力端78を入力端72と導通させる。

#### [0064]

但し、遮断回路70Aは、遮断回路70と異なり、外部回路(図示せず)が入力端72に印加した測定電圧Vxinを、抵抗R74,R75によって分圧して負荷62の測定端622に印加する。この分圧機構によれば、負荷62が測定可能な電圧よりも測定電圧Vxinが高い場合、測定電圧Vxoutを負荷62が測定可能な電圧まで下げて測定できる。

### [0065]

遮断回路70Aによれば、出力端78が入力端72と導通しているとき、入力端72に流入した電流は、抵抗R74及び抵抗R75を経由して流れ続け消費される。このような電流の消費を抑制するという観点から、遮断回路70Aの電源検知端74は、負荷66(図7参照)の制御端668に接続し、これにより、抵抗R74及び抵抗R75を流れる電流を負荷66によって制御することが好ましい。

# [0066]

図5から図8までを参照すると、図示した遮断回路70及び遮断回路70Aの夫々は、センサ62である負荷62に接続される。但し、本発明は、これに限られない。例えば、負荷62は、外部回路(図示せず)から受ける制御信号に応じて動作する電子機器であってもよい。この場合も、遮断回路70や遮断回路70Aを、外部回路と負荷62との間に接続すればよい。

#### [0067]

以下、本実施の形態における蓄電回路30の構造及び機能について更に詳しく説明する

# [0068]

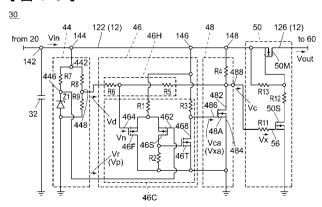

図9を図1と併せて参照すると、蓄電回路30は、蓄電部32として機能するキャパシタ32と、スイッチ部50として機能するスイッチ回路50とを備えている。蓄電回路30の制御部40は、電圧検知回路44と、比較回路46と、付加的回路48とを含んでいる。

# [0069]

10

20

30

図9を図10と併せて参照すると、電源ライン122(電源ライン12)は、第1接続点(接続点)142、第2接続点(接続点)144、第3接続点(接続点)146、及び、第4接続点(接続点)148を有している。4つの接続点142、144、146、148は、電源20に最も近い接続点142からスイッチ回路50に最も近い接続点148まで、この順に並んでいる。

# [0070]

キャパシタ32は、接続点142において電源ライン12に接続されている。詳しくは、キャパシタ32の一端は、接続点142に接続されており、キャパシタ32の他端は、グランドされている。

# [0071]

電圧検知回路44は、接続点144において電源ライン12に接続されている。詳しくは、電圧検知回路44は、検知入力端442と、参照出力端446と、検知出力端448とを有している。検知入力端442は、接続点144において電源ライン12に接続されており、これにより、検知入力端442に供給電圧Vinが印加される。参照出力端446は、印加された供給電圧Vinに応じて参照電圧Vrを出力する。検知出力端448は、印加された供給電圧Vinに応じて検知電圧Vdを出力する。

# [0072]

参照出力端446は、検知入力端442に印加された供給電圧Vinが基準電圧VZよりも低い場合、供給電圧Vinを出力し、供給電圧Vinが基準電圧VZ以上の場合、基準電圧VZを出力する。また、検知出力端448は、供給電圧Vinを分圧した電圧を検知電圧Vdとして出力する。即ち、検知電圧Vdは、供給電圧Vinに応じて変化し、且つ、供給電圧Vinよりも低い。

#### [0073]

比較回路46は、コンパレータ46Cと、抵抗R5,R6からなるヒステリシス回路46Hとを備えている。比較回路46(コンパレータ46C)は、接続点146において電源ライン12に接続されており、これにより、比較回路46(コンパレータ46C)に供給電圧Vinが印加される。比較回路46(コンパレータ46C)は、ポジティブ入力端462と、ネガティブ入力端464と、出力端468とを有している。ポジティブ入力端462は、電圧検知回路44の参照出力端446に接続されており、参照電圧Vrに応じた非反転電圧Vpが印加される。ネガティブ入力端464は、電圧検知回路44の検知出力端448に接続されており、検知電圧Vdに応じた反転電圧Vnが印加される。

# [0074]

比較回路46(コンパレータ46C)は、非反転電圧Vpと反転電圧Vnとを比較し、比較結果に基づいた付加的制御電圧Vcaを出力端468から出力する。付加的制御電圧Vcaは、非反転電圧Vpが反転電圧Vnよりも高い場合、供給電圧Vinに応じた高電圧であり、非反転電圧Vpが反転電圧Vnよりも低い場合、グランド電圧に応じた低電圧である。

# [0075]

付加的回路48は、電源端482と、グランド端484と、付加的入力端486と、スイッチ制御端488と、抵抗R4とを有している。電源端482は、接続点148において電源ライン12に接続されており、これにより、電源端482に供給電圧Vinに応じた電圧が印加される。詳しくは、供給電圧Vinを抵抗R4と(R5+R6+R9)とで分圧した電圧が電源端482に印加される。グランド端484は、グランドされている。付加的入力端486は、比較回路46の出力端468に接続されており、付加的制御電圧Vcaに応じた付加的印加電圧Vxaが印加される。スイッチ制御端488は、電源端482と接続点148との間に接続されている。付加的回路48は、付加的印加電圧Vxaによって動作し、スイッチ制御端488から制御電圧Vcを出力する。

### [0076]

付加的回路48は、付加的制御電圧Vcaに応じて付加的入力端486に印加された付加的印加電圧Vxaによって、電源端482とグランド端484との間を遮断する非グラ

10

20

30

40

ンド状態と、電源端482をグランド端484と導通させてグランドするグランド状態との間を遷移可能である。付加的回路48が非グランド状態にある場合、スイッチ制御端488は、供給電圧Vinに応じた高電圧を出力する。一方、付加的回路48がグランド状態にある場合、スイッチ制御端488はグランドされ、グランド電圧(低電圧)を出力する。即ち、制御電圧Vcは、付加的回路48がずランド状態にある場合、供給電圧Vinに応じた高電圧であり、付加的回路48がグランド状態にある場合、グランド電圧に応じた低電圧である。

# [0077]

以上のように構成された付加的回路48は、付加的印加電圧Vxaと所定の電圧値(付加的閾値TA)との大小関係によって状態遷移するように設定可能である。本実施の形態において、付加的閾値TAは、基準電圧VZよりも低くなるように設定されている。付加的回路48は、供給電圧Vinがゼロから上昇して付加的印加電圧Vxaが付加的閾値TAに達するまでは、非グランド状態を取る。付加的回路48は、供給電圧Vinがゼロから上昇して付加的印加電圧Vxaが最初に付加的閾値TAに達した以降は、付加的印加電圧Vxaが付加的閾値TAに達した以降は、付加的印加電圧Vxaが付加的閾値TAよりも高い場合、グランド状態を取り、付加的印加電圧Vxaが付加的閾値TAよりも低い場合、非グランド状態を取り、付加的印加電圧Vxaが付加的閾値TAよりも低い場合、非グランド状態を取る。

# [0078]

本実施の形態において、電源端482は、電圧検知回路44の検知出力端448とスイッチ回路50のスイッチ端56との間に接続されている。即ち、電源端482は、電源ライン12に接続されると共に、検知出力端448に接続されており、この構成により、電源端482には、検知電圧Vdに応じた電圧が印加される。本実施の形態によれば、付加的回路48が非グランド状態にある場合、スイッチ制御端488は、検知電圧Vdに応じた高電圧(供給電圧Vinよりも低く且つ検知電圧Vdよりも高い電圧)を出力する。本実施の形態における制御電圧Vcは、付加的回路48が非グランド状態にある場合、検知電圧Vdに応じた高電圧であり、付加的回路48がグランド状態にある場合、グランド電圧に応じた低電圧である。但し、本発明は、これに限られず、電源端482は、必要に応じて検知出力端448に接続すればよい。

# [0079]

スイッチ回路50のスイッチ端56は、付加的回路48のスイッチ制御端488に接続されており、制御電圧Vcに応じた印加電圧Vxが印加される。スイッチ回路50は、制御電圧Vcに応じてスイッチ端56に印加された印加電圧Vxによって、遮断状態と導通状態との間を遷移可能である。詳しくは、スイッチ回路50は、供給電圧Vinがゼロから上昇して、印加電圧Vxが所定閾値TPに達するまでは、遮断状態を取る。スイッチ回路50は、供給電圧Vinがゼロから上昇して印加電圧Vxが最初に所定閾値TPに達した以降は、印加電圧Vxと所定閾値TPとの間の大小関係に応じて状態を遷移させる。より具体的には、スイッチ回路50は、印加電圧Vxが所定閾値TPよりも高い場合、導通状態を取り、印加電圧Vxが所定閾値TPよりも低い場合、遮断状態を取る。

#### [0800]

図9及び図10から理解されるように、所定閾値TP、付加的閾値TA、付加的印加電圧Vxa及び印加電圧Vxは、蓄電回路30の回路構造に応じて調整可能である。本実施の形態によれば、供給電圧Vinがゼロから上昇して付加的印加電圧Vxaが付加的閾値TAに達するまで、印加電圧Vxは、所定閾値TPよりも低い。即ち、付加的回路48は、印加電圧Vxが所定閾値TPに達する前に非グランド状態からグランド状態に遷移し、これにより、スイッチ回路50にグランド電圧に応じた低電圧が印加される。この結果、付加的回路48がグランド状態に遷移した後も、スイッチ回路50は、遮断状態を維持する。特に、本実施の形態によれば、所定閾値TPは、付加的閾値TA以上であり、スイッチ回路50の遮断状態を維持し易い。但し本発明は、これに限られず、所定閾値TPは、付加的閾値TAより小さくてもよい。

10

20

30

#### [ 0 0 8 1 ]

以下、以上のように構成された蓄電回路30の動作について詳細に説明する。

### [0082]

図9及び図11を参照すると、蓄電回路30が動作開始した時点(図11の時間軸の値が0であるゼロ時間)において、キャパシタ32は空である。従って、供給電圧Vin、付加的制御電圧Vca(=付加的印加電圧Vxa)及び制御電圧Vc(=印加電圧Vx)の夫々は、0Vである。この結果、付加的回路48は、非グランド状態にあり、電源端482とグランド端484との間を遮断している。同様に、スイッチ回路50は遮断状態にあり、キャパシタ32と負荷60との間を遮断している。また、蓄電回路30は、初期状態にある。

[0083]

蓄電回路30が動作開始すると、キャパシタ32が徐々に充電され、これにより、供給電圧Vinが徐々に高くなる。蓄電回路30が動作開始して所定のT0時間になるまで、付加的回路48は、非グランド状態を維持し、スイッチ回路50は、遮断状態を維持する。一方、制御電圧Vcがスイッチ回路50の所定閾値TPに達するよりも前のT0時間において、付加的制御電圧Vcaが付加的回路48の付加的閾値TAに達する。

# [0084]

付加的制御電圧VcaがT0時間において付加的閾値TAに達した後、供給電圧Vinは、上昇し続ける。この結果、付加的制御電圧Vcaは、付加的回路48の付加的閾値TAを超えて上昇し続け、付加的回路48は、T0時間の直後にグランド状態になる。付加的回路48がグランド状態になると、制御電圧Vcは、グランド電圧(0V)になる。この結果、スイッチ回路50は遮断状態を維持し、キャパシタ32は、充電され続ける。

[0085]

供給電圧Vinは、T0時間以降も上昇し続ける。前述したように、基準電圧VZは、付加的閾値TAよりも高い。この設定により、供給電圧Vinは、T0時間よりも後のT1時間に基準電圧VZに達し、このとき、参照電圧Vr(非反転電圧Vp)は、基準電圧VZになる。

[0086]

供給電圧Vinは、T1時間以降も上昇し続け、これにより検知電圧Vd及び反転電圧Vnは、上昇し続ける。一方、非反転電圧Vpは、基準電圧VZに維持される。この結果、反転電圧Vnは、所定のT2時間において、非反転電圧Vpと等しくなり、その後、非反転電圧Vpを超える。T2時間において、供給電圧Vinは、開始電圧VHに達する。T0時間からT2時間の間、キャパシタ32に電力が蓄積され続ける。

[0087]

T 2 時間以降、非反転電圧 V p は、反転電圧 V n よりも低くなり、これにより、比較回路 4 6 の付加的制御電圧 V c a は、グランド電圧(0 V)になる。この結果、付加的回路 4 8 は、非グランド状態になり、スイッチ回路 5 0 は導通状態になる。導通状態において、電源 2 0 が生成した電力は、キャパシタ 3 2 に蓄積された電力と共に負荷 6 0 に供給される。

[0088]

以上に説明したように、本実施の形態の蓄電回路30は、供給電圧Vinが負荷60の動作開始電圧VSよりも高い開始電圧VHに達するまで電力を蓄積し続け、供給電圧Vinが開始電圧VHに達すると、負荷60に電力を供給する。即ち、本実施の形態の蓄電回路30は、負荷60に安定的に電力を供給できる。

[0089]

本実施の形態の蓄電回路30は、例えば、図10に示したように構成できる。

[0090]

図10を参照すると、電圧検知回路44は、3つの抵抗R7、R8、R9と、1つの定電圧素子(ツェナーダイオード)Z1とを備えている。この電圧検知回路44によれば、基準電圧VZは、ツェナーダイオードZ1のツェナー電圧である。

10

20

30

40

### [0091]

比較回路46のコンパレータ46Cは、3つのスイッチング素子(第1スイッチング素子46F、第2スイッチング素子46S及び第3スイッチング素子46T)と、3つの抵抗R1、R2、R3とを備えている。第1スイッチング素子46F及び第2スイッチング素子46F及び第2スイッチング素子46F及び第2スイッチング素子46Tは、N型MOSFETからなる。スイッチング素子の夫々は、ゲートに印加される電圧に応じて、ソースとドレインとの間が導通したON状態と、ソースとドレインとの間が遮断されたOFF状態との間を遷移可能である。

# [0092]

蓄電回路30が定常状態にあるとき、反転電圧Vnが非反転電圧Vpよりも低い場合、第1スイッチング素子46Fは、ON状態になり、第2スイッチング素子46Sは、OFF状態になる。この結果、第3スイッチング素子46Tのゲートにグランド電圧が印加され、第3スイッチング素子46Tは、OFF状態になる。即ち、第3スイッチング素子46Tのドレイン(出力端468)がグランドから遮断され、出力端468は、高電圧(供給電圧Vin)を出力する。

#### [0093]

一方、蓄電回路30が定常状態にあるとき、反転電圧Vnが非反転電圧Vpを超えると、第1スイッチング素子46Fは、OFF状態になり、第2スイッチング素子46Sは、ON状態になる。この結果、第3スイッチング素子46Tのゲートに、供給電圧Vinを抵抗R2と抵抗R1とによって分圧した電圧が印加され、第3スイッチング素子46Tは、ON状態になる。即ち、第3スイッチング素子46Tのドレイン(出力端468)がグランドと導通し、出力端468は、低電圧(グランド電圧)を出力する。

# [0094]

付加的回路48は、抵抗R4に加えて、N型MOSFETからなる付加的スイッチング素子48Aを備えている。付加的スイッチング素子48Aにおいて、ゲートは、付加的入力端486として機能し、ソースは、グランド端484として機能し、ドレインは、電源端482として機能する。付加的スイッチング素子48Aは、N型MOSFETからなり、ゲートに印加される電圧に応じて、ソースとドレインとの間が導通したON状態と、ソースとドレインとの間が遮断されたOFF状態との間を遷移可能である。以上のように構成された付加的回路48は、供給電圧Vinがゼロから上昇して付加的印加電圧Vxaが付加的閾値TAに達するまでは、非グランド状態を取る。本実施の形態において、付加的閾値TAは、付加的スイッチング素子48Aのゲート閾値である。本実施の形態における定電圧素子Z1の基準電圧VZは、付加的閾値TAに比べて十分に高い。

# [0095]

スイッチ回路50は、2つのスイッチング素子(主スイッチング素子50M及び副スイッチング素子50S)と、3つの抵抗R11、R12、R13とを備えている。主スイッチング素子50Mは、P型MOSFETからなり、副スイッチング素子50Sは、N型MOSFETからなる。スイッチング素子の夫々は、ゲートに印加される電圧に応じて、ソースとドレインとの間が導通したON状態と、ソースとドレインとの間が遮断されたOFF状態との間を遷移可能である。

# [0096]

主スイッチング素子50Mにおいて、ソースは、電源ライン12の電源20側(電源ライン122)に接続されており、ドレインは、電源ライン12の負荷60側(電源ライン126)に接続されている。副スイッチング素子50Sのゲートは、抵抗R11を介して付加的回路48のスイッチ制御端488に接続されており、スイッチ端56として機能する。副スイッチング素子50Sにおいて、ソースは、グランドされており、ドレインは、2つの抵抗R12、R13を介して主スイッチング素子50Mのソースに接続されている。主スイッチング素子50Mのゲートは、2つの抵抗R12、R13の間に接続されている。

# [0097]

50

10

20

30

以上のように構成されたスイッチ回路 5 0 は、供給電圧 V i n がゼロから上昇して、印加電圧 V x が所定閾値 T P に達するまでは、遮断状態を取る。本実施の形態において、所定閾値 T P は、副スイッチング素子 5 0 S のゲート閾値である。本実施の形態における定電圧素子 Z 1 の基準電圧 V Z は、所定閾値 T P に比べて十分に高い。

# 【実施例】

# [0098]

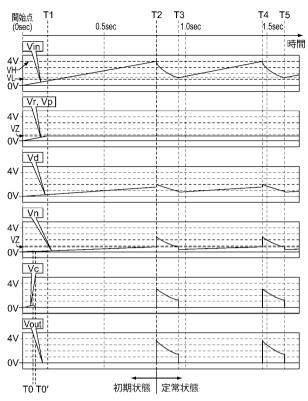

シミュレータにおいて、実施例の回路として図10の蓄電回路30を構築して動作を検証した。実施例の回路における各要素の容量値、抵抗値等は表1の通りだった。

# [0099]

# 【表1】

| #   |            | 要素の名称            | 符号    | 容量値、抵抗値等                                                                                                                                                                                                                                                                                                                                                               |

|-----|------------|------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | キャパシタ(32)  |                  | 32    | 10mF                                                                                                                                                                                                                                                                                                                                                                   |

| 2   |            | 定電圧素子(ツェナーダイオード) | Z1    | <1. 8V                                                                                                                                                                                                                                                                                                                                                                 |

| 3   |            | 第7抵抗             | R7    | 100kΩ                                                                                                                                                                                                                                                                                                                                                                  |

| 4   | 電圧検知回路(44) | 第8抵抗             | R8    | 100kΩ                                                                                                                                                                                                                                                                                                                                                                  |

| 5   |            | 第9抵抗             | R9    | 100kΩ $VGS(th) < 1. \text{ OV}$ $VGS(th) < 1. \text{ OV}$ $VGS(th) < 0. \text{ 8V}$ $100kΩ$ $100kΩ$ $100kΩ$ $100kΩ$                                                                                                                                                                                                                                                    |

| 6   |            | 第1スイッチング素子       | 465   | \/CS(#b) < 1 0\/                                                                                                                                                                                                                                                                                                                                                       |

| O   |            | (PチャネルのMOSFET)   | 401   | 100kΩ $100kΩ$ $100kΩ$ $VGS(th) < 1. 0V$ $VGS(th) < 0. 8V$ $100kΩ$ $100kΩ$ $100kΩ$ $100kΩ$ $VGS(th) < 0. 8V$ $100kΩ$ $VGS(th) < 0. 8V$ $VGS(th) < 0. 8V$                                                                                                                                                                                                                |

| 7   |            | 第2スイッチング素子       | 465   | VCS(+b) < 1 0V                                                                                                                                                                                                                                                                                                                                                         |

| ′   |            | (PチャネルのMOSFET)   | 405   | 10mF $<1.8V$ 100kΩ 100kΩ 100kΩ $<1.0V$ $<0.8V$ |

| 8   |            | 第3スイッチング素子       | 460   | VCC(H-) < 0, 8)/                                                                                                                                                                                                                                                                                                                                                       |

| 0   | 比較回路(46)   | (NチャネルのMOSFET)   | 405   | VGS(th) < 0. 8V                                                                                                                                                                                                                                                                                                                                                        |

| 9   |            | 第1抵抗             | R1    | 100kΩ                                                                                                                                                                                                                                                                                                                                                                  |

| 10  |            | 第2抵抗             | R2    | 100kΩ                                                                                                                                                                                                                                                                                                                                                                  |

| 11  |            | 第3抵抗             | R3    | 100kΩ                                                                                                                                                                                                                                                                                                                                                                  |

| 12  |            | 第5抵抗             | R5    | 100kΩ                                                                                                                                                                                                                                                                                                                                                                  |

| 13  |            | 第6抵抗             | R6    | 100kΩ                                                                                                                                                                                                                                                                                                                                                                  |

| 14  |            | 付加的スイッチング素子      | 404   |                                                                                                                                                                                                                                                                                                                                                                        |

| 14  | 付加的回路(48)  | (NチャネルのMOSFET)   | 46A   |                                                                                                                                                                                                                                                                                                                                                                        |

| 15  |            | 第4抵抗             | R7    | 100kΩ                                                                                                                                                                                                                                                                                                                                                                  |

| 16  |            | 主スイッチング素子        | EOM.  | 100k $\Omega$<br>100k $\Omega$<br>VGS(th) < 0.8V<br>100k $\Omega$<br>VGS(th) < 1.0V                                                                                                                                                                                                                                                                                    |

| 10  |            | (PチャネルのMOSFET)   | SOIVI |                                                                                                                                                                                                                                                                                                                                                                        |

| 17  |            | 副スイッチング素子        | 500   | VCS(+k) < 0, 8\/                                                                                                                                                                                                                                                                                                                                                       |

| 1 / | スイッチ回路(50) | (NチャネルのMOSFET)   | 505   | VG5(tn) < 0.8V                                                                                                                                                                                                                                                                                                                                                         |

| 18  |            | 第11抵抗            | R11   | 10kΩ                                                                                                                                                                                                                                                                                                                                                                   |

| 19  |            | 第12抵抗            | R12   | 1kΩ                                                                                                                                                                                                                                                                                                                                                                    |

| 20  |            | 第13抵抗            | R13   | 10kΩ                                                                                                                                                                                                                                                                                                                                                                   |

# [0100]

表 1 に記載した抵抗値に基づき、開始電圧 V H、停止電圧 V L、及び、蓄電回路 3 0 の合成抵抗 R を計算した。この計算において、スイッチング素子による影響は考慮しなかった。計算の結果、開始電圧 V H は、4 .5 V であり、停止電圧 V L は、1 .3 V だった。スイッチング素子の夫々のゲート閾値 V G S ( t h )は、計算による停止電圧 V L よりも

10

20

30

低かった。また、合成抵抗Rは、供給電圧Viが開始電圧VHから停止電圧VLまで下降するまでの間は、33kであり、供給電圧Viが停止電圧VLから開始電圧VHまで上昇するまでの間は、33k だった。

#### [0101]

実施例の回路を電源20及び負荷60の間に接続して、実施例の回路の動作を検証した。動作検証において、電源20として、直列に接続した8つの光電池を使用し、負荷60として、10 の抵抗器を使用した。光電池の夫々において、受光面積は57.8cm²であり、直射日光による開放電圧Vocは1Vであり、直射日光による短絡電流Iscは50mAだった。光電池の垂直上方から太陽光相当のスペクトルを持つ光を10mW/cm²の強度で与え、これにより、電源20から約50mAの電流を実施例の回路に供給した。ツェナーダイオードZ1のツェナー電圧VZ(公称値:1.8V)は、電源20から供給される電流値によって異なり、上述の条件では、0.9Vだった。以上の条件において、キャパシタ32が空の状態(即ち、キャパシタ32の電圧が0Vの状態)を開始点(0秒時点)として、供給電圧Vin、参照電圧Vr(非反転電圧Vp)、検知電圧Vd 反転電圧Vn、制御電圧Vc、及び、出力電圧Voutの夫々の変動を、シミュレータにより測定した。

# [0102]

図12に測定結果を示す。図12から理解されるように、実施例の回路は、負荷60に 安定的に電力を供給できる。

# 【産業上の利用可能性】

#### [0103]

電源、蓄電回路及び様々な負荷を備えた蓄電型システムにおいて、負荷を動作させるための電源としてエネルギーハーベスティングを応用することで、電池が不要になり、これにより、蓄電型システムの軽量化、高耐環境化、メンテナンスフリー化等の様々な効果が期待できる。蓄電型システムの応用例として、負荷としてセンサを備えたセンサシステムが考えられる。様々なセンサシステム、特に無線センサシステムは、近年発展が著しいIoT分野及びM2M分野において、産業機器(電子機器)の状態を把握するために欠かせないものとなっている。

# [0104]

エネルギーハーベスティングを応用したセンサシステムによって産業機器の状態を把握する場合、産業機器から出力される何らかの信号線をセンサシステムに接続する必要がある。一方、このようなセンサシステムにおける蓄電回路は、エネルギーハーベスティングによって得られる微小な電力でセンサシステムを間欠的に動作させる。蓄電回路がセンサに電力を供給していないときに信号線を通じてセンサに電流が流れると様々な問題が生じうる。例えば、高価な産業機器が故障するおそれがある。このような問題は、エネルギーハーベスティングの実用化が進まない原因の1つになっていた。

# [0105]

一方、本発明によれば、センサの信号線を通じて電流が流れ込むことが無い。従って、エネルギーハーベスティングを応用したセンサシステムは、本来の効果を発揮できる。加えて、センサを高価な産業機器に安心して接続できる。本発明によれば、IoT分野及びM2M分野でのエネルギーハーベスティングの応用が促進されると考えられる。

#### 【符号の説明】

# [0106]

| 1 0   | 蓄電型システム             |

|-------|---------------------|

| 1 2   | 電源ライン               |

| 1 2 2 | 入力側電源ライン(電源ライン)     |

| 1 2 6 | 出力側電源ライン(電源ライン)     |

| 1 4 2 | 第 1 接 続 点 ( 接 続 点 ) |

| 1 4 4 | 第 2 接 続 点 ( 接 続 点 ) |

| 1 4 6 | 第 3 接 続 点 ( 接 続 点 ) |

10

20

30

40

| 1 4 8                 | 第 4 接 続 点 ( 接 続 点 ) |            |

|-----------------------|---------------------|------------|

| 162,162A              | 検 知 点               |            |

| 2 0                   | 電源                  |            |

| 3 0                   | 蓄電回路                |            |

| 3 2                   | キャパシタ(蓄電部)          |            |

| 4 0                   | 制御部                 |            |

| 4 4                   | 電圧検知回路              |            |

| 4 4 2                 | 検知入力端               |            |

| 4 4 2                 |                     |            |

|                       | 参照出力端               | 10         |

| 4 4 8                 | 検知出力端               | 10         |

| 4 6                   | 比較回路                |            |

| 4 6 C                 | コンパレータ              |            |

| 4 6 H                 | ヒステリシス回路            |            |

| 4 6 F                 | 第 1 スイッチング素子        |            |

| 4 6 S                 | 第 2 スイッチング素子        |            |

| 4 6 T                 | 第 3 スイッチング素子        |            |

| 4 6 2                 | ポジティブ入力端            |            |

| 4 6 4                 | ネガティブ入力端            |            |

| 4 6 8                 | 出力端                 |            |

| 4 8                   | 付加的回路               | 20         |

| • •                   |                     | 20         |

| 4 8 A                 | 付加的スイッチング素子         |            |

| 4 8 2                 | 電源端                 |            |

| 4 8 4                 | グランド端               |            |

| 4 8 6                 | 付 加 的 入 力 端         |            |

| 4 8 8                 | スイッチ制御端             |            |

| 5 0                   | スイッチ回路(スイッチ部)       |            |

| 5 0 M                 | 主スイッチング素子           |            |

| 5 0 S                 | 副スイッチング素子           |            |

| 5 6                   | スイッチ端               |            |

| 6 0                   | 負荷                  | 30         |

| 6 2                   | 負荷(センサ)             |            |

| 6 2 2                 | 測定端                 |            |

| 6 4                   | 負荷(DC-DCコンバータ)      |            |

| 6 6                   | 負荷(マイクロコンピュータ)      |            |

|                       |                     |            |

| 6 6 8                 | 制御端                 |            |

| 7 0 , 7 0 A           | 遮断回路                |            |

| 7 0 2                 | 第 1 素 子             |            |

| 7 0 4                 | 第 2 素子              |            |

| 7 2                   | 入力端                 |            |

| 7 4                   | 電 源 検 知 端           | 40         |

| 7 8                   | 出力端                 |            |

| R 7 , R 8 , R 9       | 抵抗(電圧検知回路の抵抗)       |            |

| R 1 , R 2 , R 3       | 抵抗(コンパレータの抵抗)       |            |

| R 5 , R 6             | 抵抗(ヒステリシス回路の抵抗)     |            |

| R 4                   | 抵抗(付加的回路の抵抗)        |            |

| R 1 1 , R 1 2 , R 1 3 | 抵抗(スイッチ回路の抵抗)       |            |

| R 6 1 , R 6 2         | 抵抗(センサの抵抗)          |            |

|                       |                     |            |

| R 6 4                 | 抵抗(DC/DCコンバータの抵抗)   |            |

| R 7 1 , R 7 2 , R 7 3 | 抵抗(遮断回路の抵抗)         | <b>5</b> 0 |

| R 7 4 , R 7 5         | 抵抗(変形例の遮断回路の抵抗)     | 50         |

10

定電圧素子(ツェナーダイオード) Z 1 Vin 供給電圧 出力電圧 Vout V Z 基準電圧 Vr 参照電圧 V d 検知電圧 非反転電圧 V p V n 反転電圧 Vса 付加的制御電圧 V x a 付加的印加電圧 制御電圧 V c V x 印加電圧 動作開始電圧 V S VH 開始電圧 V L 停止電圧  $V \times i n$ 測定電圧 Vxout 測定電圧  $V \times d$ 検出電圧 V P 所定電圧

# 【図1】

10 20 30 蓄電回路 50 122 (12) Vin 32 蓄電部 制御部 Vx 1 56 Vout 負荷

# 【図2】

# 【図3】

# 【図4】

# 【図5】

# 【図8】

# 【図6】

【図7】

【図9】

# 【図10】

# 【図11】

# 【図12】

# 【図13】

# フロントページの続き

F ターム(参考) 5J055 AX23 BX16 DX14 DX22 EY01 EY10 EY12 EY13 EY21 EZ10 FX05 FX32 GX01 GX02