## (19) 대한민국특허청(KR) (12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.)

**H01L 23/12** (2006.01) **H01L 23/48** (2006.01)

(21) 출원번호

10-2013-0123599

(22) 출원일자

2013년10월16일

심사청구일자 없음

(43) 공개일자

(11) 공개번호

10-2015-0044329 2015년04월24일

(71) 출원인

삼성전자주식회사

경기도 수원시 영통구 삼성로 129 (매탄동)

(72) 발명자

강운병

경기 화성시 동탄지성로 42, 223동 1901호 (반송 동, 시범한빛마을동탄아이파크아파트)

노병혁

경기 용인시 수지구 진산로 90, 514동 1302호 (풍 덕천동, 진산마을삼성5차아파트)

조태제

경기 화성시 금반1길 53, 푸르지오하임 227호 (반 송동, 대우)

(74) 대리인

리앤목특허법인

전체 청구항 수 : 총 20 항

## (54) 발명의 명칭 **칩 적충 반도체 패키지 및 그 제조 방법**

#### (57) 요 약

본 발명의 기술적 사상의 칩 적층 반도체 패키지는 제1 전면 및 이에 반대되는 제1 후면을 가지며. 상기 제1 전면에 제1 연결 부재를 갖는 제1 칩과, 제2 전면 및 이에 반대되는 제2 후면을 가지며, 상기 제1 전면에 대향한 상기 제2 전면에 형성된 제2 연결 부재, 및 상기 제2 연결 부재와 전기적으로 연결된 제1 관통 실리콘 비아(TS V)를 갖는 제2 칩과, 상기 제1 전면 및 제2 전면의 사이에서 상기 제1 연결 부재와 상기 제2 연결 부재 사이를 채우도록 형성된 제1 밀봉재를 포함하고. 상기 제1 칩의 제1 연결 부재는 상기 제2 칩의 제2 연결 부재에 대해미러(mirror) 대칭 형태로 형성되어 있다.

## 대 표 도 - 도13

### 명세서

### 청구범위

#### 청구항 1

제1 전면 및 이에 반대되는 제1 후면을 가지며. 상기 제1 전면에 제1 연결 부재를 갖는 제1 칩;

제2 전면 및 이에 반대되는 제2 후면을 가지며, 상기 제1 전면에 대향한 상기 제2 전면에 형성된 제2 연결 부재, 및 상기 제2 연결 부재와 전기적으로 연결된 제1 관통 실리콘 비아(TSV)를 갖는 제2 칩; 및

상기 제1 전면 및 제2 전면의 사이에서 상기 제1 연결 부재와 상기 제2 연결 부재 사이를 채우도록 형성된 제1 밀봉재를 포함하고.

상기 제1 칩의 제1 연결 부재는 상기 제2 칩의 제2 연결 부재에 대해 미러(mirror) 대칭 형태로 형성되어 있는 것을 특징으로 하는 칩 적충 반도체 패키지.

#### 청구항 2

제1항에 있어서, 상기 제1 밀봉재는 상기 제1 연결 부재 및 제2 연결 부재가 연결된 부분들 사이에서 확장하여 상기 제2 칩의 측면에 더 형성되어 있는 것을 특징으로 하는 칩 적층 반도체 패키지.

#### 청구항 3

제1항에 있어서, 상기 제2 칩의 제2 후면에는 외부 부재와 연결할 수 있는 제3 연결 부재가 더 형성되어 있는 것을 특징으로 하는 칩 적충 반도체 패키지.

#### 청구항 4

제3항에 있어서, 상기 제1 칩 및 제2 칩은 상기 제3 연결 부재를 통해 메인 칩 또는 보드 기판에 실장되는 것을 특징으로 하는 칩 적충 반도체 패키지.

### 청구항 5

제3항에 있어서, 상기 제2 칩의 제2 후면에 형성된 상기 제3 연결부재와 전기적으로 연결된 제4 연결 부재가 제3 전면에 형성되고, 내부에는 제2 관통 실리콘 비아가 형성된 적어도 하나의 제3 칩이 더 형성되어 있는 것을 특징으로 하는 칩 적층 반도체 패키지.

## 청구항 6

제5항에 있어서, 상기 제3 칩의 후면에는 외부 부재와 연결할 수 있는 제5 연결 부재가 형성되어 있는 것을 특징으로 하는 칩 적층 반도체 패키지.

### 청구항 7

제5항에 있어서, 상기 제3 연결 부재와 상기 제4 연결 부재 사이를 채우도록 제2 밀봉재가 더 형성되어 있는 것을 특징으로 하는 칩 적층 반도체 패키지.

#### 청구항 8

제5항에 있어서, 상기 제2 밀봉재는 상기 제3 연결 부재 및 제4 연결 부재가 연결된 부분들 사이에서 확장하여 상기 제3 칩의 측면에 더 형성되어 있는 것을 특징으로 하는 칩 적충 반도체 패키지.

#### 청구항 9

제1항에 있어서, 상기 제1 칩의 크기는 제2 칩의 크기보다 크거나 동일한 것을 특징으로 하는 칩 적층 반도체 패키지.

#### 청구항 10

제1항에 있어서, 상기 제1 칩의 후면 및 양측면은 노출되어 있는 것을 특징으로 하는 칩 적층 반도체 패키지.

#### 청구항 11

제1 전면 및 이에 반대되는 제1 후면을 가지는 제1 바디층과, 상기 제1 전면에 형성된 제1 연결 부재를 갖는 제 1 침;

제2 전면 및 이에 반대되는 제2 후면을 갖는 제2 바디층과, 상기 제2 바디층 내에 형성된 제1 관통 실리콘 비아 (TSV)와, 상기 제1 전면에 대향한 상기 제2 전면에 형성되고 상기 제1 관통 실리콘 비아와 전기적으로 연결된 제2 연결 부재 및 상기 제2 칩의 후면에는 형성되고 상기 제1 관통 실리콘 비아와 전기적으로 연결된 제3 연결 부재를 갖는 제2 칩;

상기 제1 전면 및 제2 전면 사이에서 상기 제1 연결 부재와 상기 제2 연결 부재 사이를 채우도록 형성된 제1 밀 봉재; 및

상기 제2 칩의 제2 후면에는 적어도 하나의 제3 칩이 형성되고,

상기 제3 칩은 제3 전면 및 이에 반대되는 제3 후면을 갖는 제3 바디층과, 상기 제3 바디층 내에 형성된 제2 관통 실리콘 비아(TSV)와, 상기 제2 후면에 대향한 상기 제3 전면 상에는 상기 제3 연결 부재와 전기적으로 연결된 제4 연결 부재를 가지며;

상기 제2 후면 및 제3 전면 사이에서 상기 제3 연결 부재와 상기 제4 연결 부재 사이를 채우도록 형성된 제2 밀 봉재를 포함하고,

상기 제1 칩의 제1 연결 부재는 상기 제2 칩의 제2 연결 부재에 대해 미러 대칭 형태로 형성되어 있는 것을 특징으로 하는 칩 적층 반도체 패키지.

### 청구항 12

제1 전면 및 이에 반대되는 제1 후면을 가지며. 상기 제1 전면에 제1 연결 부재를 갖는 제1 칩을 복수개 포함하는 기저 웨이퍼를 준비하는 단계;

제2 전면 및 이에 반대되는 제2 후면을 가지며, 상기 제2 전면에 상기 제1 연결 부재에 대응되는 제2 연결 부재를 갖는 제2 칩을 복수개 준비하는 단계;

상기 기저 웨이퍼 상에 형성된 개개의 제1 칩 상에 상기 제2 칩을 적충하되, 상기 제2 연결 부재는 상기 제1 전 면 및 제2 전면 사이에서 상기 제1 연결 부재와 전기적으로 연결되는 단계;

상기 기저 웨이퍼 상에 형성된 제2 칩을 밀봉제로 밀봉하는 단계;

상기 제2 첩에 상기 제2 연결 부재와 전기적으로 연결되는 제1 관통 실리콘 비아를 형성하는 단계; 및

상기 기저 웨이퍼에 형성된 제1 칩 및 제2 칩들 각각을 분리하는 단계를 포함하고,

상기 기저 웨이퍼에 포함된 제1 칩의 제1 연결 부재는 상기 제2 칩의 제2 연결 부재에 대해 미러 대칭 형태로 형성하는 것을 특징으로 하는 칩 적층 반도체 패키지 제조방법.

## 청구항 13

제12항에 있어서, 상기 제1 관통 실리콘 비아를 형성하는 단계 후에, 상기 제2 칩의 제2 후면 상에서 상기 제1 관통 실리콘 비아와 연결되는 제3 연결 부재를 더 형성하는 것을 특징으로 하는 칩 적층 반도체 패키지 제조 방법.

### 청구항 14

제13항에 있어서, 상기 제2 칩들 각각에는 적어도 하나의 제3 칩을 부착하는 단계를 포함하되,

상기 제3 칩은 제3 전면 및 이에 반대되는 제3 후면과, 상기 제3 전면에 형성된 제4 연결 부재를 가지며, 상기 제4 연결 부재는 상기 제2 후면 및 제3 전면 에서 상기 제3 연결 부재와 전기적으로 연결하는 것을 특징으로 하는 칩 적층 반도체 패키지 제조 방법.

### 청구항 15

제14항에 있어서, 상기 기저 웨이퍼 상에 형성된 제3 칩을 제2 밀봉제로 밀봉하고, 상기 제3 칩에 상기 제3 연결 부재와 전기적으로 연결되는 제2 관통 실리콘 비아를 더 형성하는 단계를 포함하는 것을 특징으로 하는 칩적층 반도체 패키지 제조방법.

## 청구항 16

제12항에 있어서, 상기 기저 웨이퍼에 형성된 제1 칩 및 제2 칩들 각각을 분리하는 단계는 상기 제2 칩의 양측 면에 제1 밀봉재가 형성되도록 상기 기저 웨이퍼를 절단하는 것을 특징으로 하는 칩 적충 반도체 패키지 제조 방법.

#### 청구항 17

제12항에 있어서, 상기 기저 웨이퍼에 형성된 제1 칩 및 제2 칩들 각각을 분리하는 단계는 상기 제2 칩의 양측 면이 노출되도록 상기 기저 웨이퍼를 절단하는 것을 특징으로 하는 칩 적충 반도체 패키지 제조 방법.

#### 청구항 18

제1 전면 및 이에 반대되는 제1 후면을 가지며. 상기 제1 전면에 제1 연결 부재를 갖는 제1 칩을 복수개 포함하는 기저 웨이퍼를 준비하는 단계;

제2 전면 및 이에 반대되는 제2 후면을 가지며, 상기 제2 전면에 상기 제1 연결 부재에 대응되는 제2 연결 부재를 갖고, 내부에는 제2 연결 부재와 전기적으로 연결되는 제1 관통 실리콘 비아를 갖는 제2 칩을 복수개 준비하는 단계;

상기 기저 웨이퍼 상에 형성된 개개의 제1 칩 상에 상기 제2 칩을 적층하되,

상기 제1 연결 부재는 상기 제2 연결 부재에 대해 미러 대칭 형태로 형성되어 있어 상기 제2 연결 부재는 상기 제1 전면 및 제2 전면 사이에서 상기 제1 연결 부재와 전기적으로 연결되는 단계;

상기 기저 웨이퍼 상에 형성된 제2 칩을 제1 밀봉제로 밀봉하는 단계;

상기 제2 칩의 제2 후면 상에서 상기 제1 관통 실리콘 비아와 연결되는 제3 연결 부재를 형성하는 단계;

상기 제2 칩들 각각에 적어도 하나의 제3 칩을 부착하되, 상기 제3 칩은 제3 전면 및 이에 반대되는 제3 후면과, 상기 제3 전면에 형성된 제4 연결 부재 및 이에 연결된 제2 관통 실리콘 비아를 가지며, 상기 제4 연결 부재를 상기 제2 후면 및 제3 전면 사이에서 상기 제3 연결 부재와 전기적으로 연결하는 단계;

상기 기저 웨이퍼 상에 형성된 제3 칩을 제2 밀봉제로 밀봉하는 단계; 및

상기 기저 웨이퍼에 형성된 상기 제1 칩, 제2 칩 및 제3 칩들 각각을 분리하는 단계를 포함하여 이루어지는 것을 특징으로 하는 칩 적충 반도체 패키지 제조방법.

#### 청구항 19

제18항에 있어서, 상기 기저 웨이퍼에 형성된 제1 칩, 제2 칩 및 제3 칩들 각각을 분리하는 단계는 상기 제2 칩 및 제3 칩의 양측면에 상기 제1 밀봉재 및 제2 밀봉재가 형성되도록 상기 기저 웨이퍼를 절단하는 것을 특징으로 하는 칩 적충 반도체 패키지 제조 방법.

### 청구항 20

제18항에 있어서, 상기 기저 웨이퍼에 형성된 제1 칩, 제2 칩 및 제3 칩들 각각을 분리하는 단계는 상기 제2 칩 및 제3 칩의 양측면이 노출되도록 상기 기저 웨이퍼를 절단하는 것을 특징으로 하는 칩 적충 반도체 패키지 제조 방법.

## 발명의 설명

#### 기술분야

[0001]

본 발명의 기술적 사상은 반도체 패키지 및 그 제조방법에 관한 것으로서, 보다 상세하게는 칩이 복수개 적충된 칩 적충 반도체 패키지 및 그 제조 방법에 관한 것이다.

## 배경기술

[0002] 반도체 산업은 소형화, 다기능화 및 고용량화된 높은 신뢰성을 갖는 반도체 제품을 저렴하게 제조하는 것이다. 이와 같은 복합적인 목표를 달성 가능하게 하는 중요한 기술중의 하나가 반도체 패키지 기술이다. 패키지 기술 중에서 앞서 설명한 같은 복합적인 목표를 달성하는 위한 방법으로, 칩들을 복수개 적층하는 칩 적층 반도체 패키지가 제안되고 있다.

### 발명의 내용

### 해결하려는 과제

- [0003] 본 발명의 기술적 사상이 해결하려는 과제는 칩들을 적충하여 소형화, 다기능화 및 고용량화를 가질 수 있는 칩 적층 반도체 패키지를 제공하는 데 있다.

- [0004] 또한, 본 발명의 기술적 사상이 해결하고자 하는 다른 과제는 상술한 특성을 구비하는 칩 적층 반도체 패키지를 저렴하게 제조할 수 있는 칩 적층 반도체 패키지 제조 방법을 제공하는 데 있다.

### 과제의 해결 수단

- [0005] 상술한 과제를 해결하기 위하여 본 발명의 기술적 사상의 칩 적충 반도체 패키지는 제 제1 전면 및 이에 반대되는 제 후면을 가지며. 상기 제1 전면에 제1 연결 부재를 갖는 제1 칩과, 제2 전면 및 이에 반대되는 제2 후면을 가지며, 상기 제1 전면에 대향한 상기 제2 전면에 형성된 제2 연결 부재, 및 상기 제2 연결 부재와 전기적으로 연결된 제1 관통 실리콘 비아(TSV)를 갖는 제2 칩과, 상기 제1 전면 및 제2 전면의 사이에서 상기 제1 연결 부재와 상기 제2 연결 부재 사이를 채우도록 형성된 제1 밀봉재를 포함하고. 상기 제1 칩의 제1 연결 부재는 상기 제2 칩의 제2 연결 부재에 대해 미러(mirror) 대칭 형태로 형성되어 있는 것을 포함한다.

- [0006] 본 발명의 기술적 사상의 일 실시예에 있어서, 상기 제1 밀봉재는 상기 제1 연결 부재 및 제2 연결 부재가 연결 된 부분들 사이에서 확장하여 상기 제2 칩의 측면에 더 형성되어 있을 수 있다.

- [0007] 본 발명의 기술적 사상의 일 실시예에 있어서, 상기 제2 칩의 제2 후면에는 외부 부재와 연결할 수 있는 제3 연결 부재가 더 형성되어 있을 수 있다. 상기 제1 칩 및 제2 칩은 상기 제3 연결 부재를 통해 메인 칩 또는 보드 기판에 실장될 수 있다. 상기 제2 칩의 제2 후면에 형성된 상기 제3 연결부재와 전기적으로 연결된 제4 연결 부재가 제3 전면에 형성되고, 내부에는 제2 관통 실리콘 비아가 형성된 적어도 하나의 제3 칩이 더 형성되어 있을 수 있다.

- [0008] 본 발명의 기술적 사상의 일 실시예에 있어서, 상기 제3 칩의 후면에는 외부 부재와 연결할 수 있는 제5 연결 부재가 형성되어 있을 수 있다. 상기 제3 연결 부재와 상기 제4 연결 부재 사이를 채우도록 제2 밀봉재가 더 형 성되어 있을 수 있다. 상기 제2 밀봉재는 상기 제3 연결 부재 및 제4 연결 부재가 연결된 부분들 사이에서 확장 하여 상기 제3 칩의 측면에 더 형성되어 있을 수 있다.

- [0009] 본 발명의 기술적 사상의 일 실시예에 있어서, 상기 제1 칩의 크기는 제2 칩의 크기보다 크거나 동일할 수 있다. 상기 제1 칩의 두께는 제2 칩의 두께보다 두껍거나 동일할 수 있다.

- [0010] 본 발명의 기술적 사상의 일 실시예에 있어서, 상기 제1 칩의 후면 및 양측면은 노출되어 있을 수 있다. 상기 제2 칩의 양측면은 노출되어 있을 수 있다.

- [0011] 본 발명의 기술적 사상의 일 실시예에 있어서, 상기 제1 밀봉재는 언더필, 접착제 또는 몰딩재일 수 있다.

- [0012] 본 발명의 기술적 사상에 의한 칩 적충 반도체 패키지는 제1 전면 및 이에 반대되는 제1 후면을 가지는 제1 바다층과, 상기 제1 전면에 형성된 제1 연결 부재를 갖는 제1 칩과, 제2 전면 및 이에 반대되는 제2 후면을 갖는 제2 바다층과, 상기 제2 바다층 내에 형성된 제1 관통 실리콘 비아(TSV)와, 상기 제1 전면에 대향한 상기 제2 전면에 형성되고 상기 제1 관통 실리콘 비아와 전기적으로 연결된 제2 연결 부재 및 상기 제2 칩의 후면에는 형성되고 상기 제1 관통 실리콘 비아와 전기적으로 연결된 제3 연결 부재를 갖는 제2 칩과, 상기 제1 전면 및 제2 전면 사이에서 상기 제1 연결 부재와 상기 제2 연결 부재 사이를 채우도록 형성된 제1 밀봉재를 포함한다.

- [0013] 본 발명의 칩 적충 반도체 패키지는 상기 제2 칩의 제2 후면에는 적어도 하나의 제3 칩이 형성되고, 상기 제3 칩은 제3 전면 및 이에 반대되는 제3 후면을 갖는 제3 바디충과, 상기 제3 바디충 내에 형성된 제2 관통 실리콘비아(TSV)와, 상기 제2 후면에 대향한 상기 제3 전면 상에는 상기 제3 연결 부재와 전기적으로 연결된 제4 연결

부재를 가지고, 상기 제2 후면 및 제3 전면 사이에서 상기 제3 연결 부재와 상기 제4 연결 부재 사이를 채우도록 형성된 제2 밀봉재를 포함하고, 상기 제1 칩의 제1 연결 부재는 상기 제2 칩의 제2 연결 부재에 대해 미러 대칭 형태로 형성되어 있다.

- [0014] 본 발명의 기술적 사상의 일 실시예에 있어서, 상기 제1 관통 실리콘 비아 및 제2 관통 실리콘 비아는 각각 상기 제2 바디층 및 제3 바디층을 전체를 관통하도록 형성되어 있을 수 있다.

- [0015] 본 발명의 기술적 사상의 일 실시예에 있어서, 상기 제1 관통 실리콘 비아 및 제2 관통 실리콘 비아는 각각 상기 제2 바디층 및 제3 바디층의 일부를 관통하는 일부 관통 실리콘 비아이고, 일부 관통 실리콘 비아 상에는 절연충에 의하여 절연된 다층 배선 패턴이 형성되어 있고, 상기 다층 배선 패턴은 상기 일부 관통 실리콘 비아와 전기적으로 연결될 수 있다.

- [0016] 본 발명의 기술적 사상의 일 실시예에 있어서, 상기 제3 칩의 후면에는 외부 부재와 연결할 수 있는 제5 연결 부재가 더 형성되어 있을 수 있다. 상기 제1 칩 내지 제3 칩은 상기 제5 연결 부재를 통해 메인 칩 또는 보드 기판에 실장될 수 있다.

- [0017] 본 발명의 기술적 사상의 일 실시예에 있어서, 상기 제1 밀봉재는 상기 제1 연결 부재 및 제2 연결 부재가 연결 된 부분들 사이에서 확장하여 상기 제2 칩의 측면에 더 형성되고, 상기 제2 밀봉재는 상기 제3 연결 부재 및 제4 연결 부재가 연결된 부분들 사이에서 확장하여 상기 제3 칩의 측면에 더 형성될 수 있다.

- [0018] 본 발명의 기술적 사상의 일 실시예에 있어서, 상기 제1 칩의 두께는 제2 칩이나 제3 칩의 두께보다 두껍거나 동일할 수 있다.

- [0019] 본 발명의 기술적 사상의 일 실시예에 있어서, 상기 제1 칩의 후면 및 양측면은 노출되어 있고, 상기 제2 칩 및 제3 칩의 양측면은 노출되어 있을 수 있다.

- [0020] 본 발명의 기술적 사상의 일 실시예에 의한 칩 적충 반도체 패키지의 제조 방법은 제1 전면 및 이에 반대되는 제1 후면을 가지며. 상기 제1 전면에 제1 연결 부재를 갖는 제1 칩을 복수개 포함하는 기저 웨이퍼를 준비하는 단계와, 제2 전면 및 이에 반대되는 제2 후면을 가지며, 상기 제2 전면에 상기 제1 연결 부재에 대응되는 제2 연결 부재를 갖는 제2 칩을 복수개 준비하는 단계와, 상기 기저 웨이퍼 상에 형성된 개개의 제1 칩 상에 상기 제2 칩을 적충하되, 상기 제2 연결 부재는 상기 제1 전면 및 제2 전면 사이에서 상기 제1 연결 부재와 전기적으로 연결되는 단계와, 상기 기저 웨이퍼 상에 형성된 제2 칩을 밀봉제로 밀봉하는 단계와, 상기 제2 칩에 상기 제2 연결 부재와 전기적으로 연결되는 제1 관통 실리콘 비아를 형성하는 단계와, 상기 기저 웨이퍼에 형성된 제1 칩 및 제2 칩들 각각을 분리하는 단계를 포함하고, 상기 기저 웨이퍼에 포함된 제1 칩의 제1 연결 부재는 상기 제2 칩의 제2 연결 부재에 대해 미러 대칭 형태로 형성한다.

- [0021] 본 발명의 기술적 사상의 일 실시예에 있어서, 상기 제1 관통 실리콘 비아를 형성하는 단계 후에, 상기 제2 칩의 제2 후면 상에서 상기 제1 관통 실리콘 비아와 연결되는 제3 연결 부재를 더 형성할 수 있다.

- [0022] 본 발명의 기술적 사상의 일 실시예에 있어서, 상기 제2 칩들 각각에는 적어도 하나의 제3 칩을 부착하는 단계를 포함하되, 상기 제3 칩은 제3 전면 및 이에 반대되는 제3 후면과, 상기 제3 전면에 형성된 제4 연결 부재를 가지며, 상기 제4 연결 부재는 상기 제2 후면 및 제3 전면에서 상기 제3 연결 부재와 전기적으로 연결할 수 있다.

- [0023] 본 발명의 기술적 사상의 일 실시예에 있어서, 상기 기저 웨이퍼 상에 형성된 제3 칩을 제2 밀봉제로 밀봉하고, 상기 제3 칩에 상기 제3 연결 부재와 전기적으로 연결되는 제2 관통 실리콘 비아를 더 형성할 수 있다.

- [0024] 본 발명의 기술적 사상의 일 실시예에 있어서, 상기 기저 웨이퍼에 형성된 제1 칩 및 제2 칩들 각각을 분리하는 단계는 상기 제2 칩의 양측면에 제1 밀봉재가 형성되도록 상기 기저 웨이퍼를 절단할 수 있다.

- [0025] 본 발명의 기술적 사상의 일 실시예에 있어서, 상기 기저 웨이퍼에 형성된 제1 칩 및 제2 칩들 각각을 분리하는 단계는 상기 제2 칩의 양측면이 노출되도록 상기 기저 웨이퍼를 절단할 수 있다.

- [0026] 본 발명의 기술적 사상의 칩 적충 반도체 패키지의 제조 방법은, 제1 전면 및 이에 반대되는 제1 후면을 가지며. 상기 제1 전면에 제1 연결 부재를 갖는 제1 칩을 복수개 포함하는 기저 웨이퍼를 준비하는 단계와, 제2 전면 및 이에 반대되는 제2 후면을 가지며, 상기 제2 전면에 상기 제1 연결 부재에 대응되는 제2 연결 부재를 갖고, 내부에는 제2 연결 부재와 전기적으로 연결되는 제1 관통 실리콘 비아를 갖는 제2 칩을 복수개 준비하는 단계와, 상기 기저 웨이퍼 상에 형성된 개개의 제1 칩 상에 상기 제2 칩을 적충하되, 상기 제1 연결 부재는 상

기 제2 연결 부재에 대해 미러 대칭 형태로 형성되어 있어 상기 제2 연결 부재는 상기 제1 전면 및 제2 전면 사이에서 상기 제1 연결 부재와 전기적으로 연결되는 단계와, 상기 기저 웨이퍼 상에 형성된 제2 칩을 제1 밀봉제로 밀봉하는 단계와, 상기 제2 칩의 제2 후면 상에서 상기 제1 관통 실리콘 비아와 연결되는 제3 연결 부재를 형성하는 단계와, 상기 제2 칩들 각각에 적어도 하나의 제3 칩을 부착하되, 상기 제3 칩은 제3 전면 및 이에 반대되는 제3 후면과, 상기 제3 전면에 형성된 제4 연결 부재 및 이에 연결된 제2 관통 실리콘 비아를 가지며, 상기 제4 연결 부재를 상기 제2 후면 및 제3 전면 사이에서 상기 제3 연결 부재와 전기적으로 연결하는 단계와, 상기 기저 웨이퍼 상에 형성된 제3 칩을 제2 밀봉제로 밀봉하는 단계와, 상기 기저 웨이퍼에 형성된 상기 제1 칩, 제2 칩 및 제3 칩들 각각을 분리하는 단계를 포함한다.

- [0027] 본 발명의 기술적 사상의 일 실시예에 있어서, 상기 기저 웨이퍼에 형성된 제1 칩, 제2 칩 및 제3 칩들 각각을 분리하는 단계는 상기 제2 칩 및 제3 칩의 양측면에 제1 및 제2 밀봉재가 형성되도록 상기 기저 웨이퍼를 절단할 수 있다.

- [0028] 본 발명의 기술적 사상의 일 실시예에 있어서, 상기 기저 웨이퍼에 형성된 제1 칩, 제2 칩 및 제3 칩들 각각을 분리하는 단계는 상기 제2 칩 및 제3 칩의 양측면이 노출되도록 상기 기저 웨이퍼를 절단할 수 있다.

### 발명의 효과

- [0029] 본 발명의 기술적 사상에 따르면, 제1 칩과 제2 칩의 적층시 임시 캐리어 웨이퍼(temporary carrier wafer)를 이용하지 않고 기저 웨이퍼에 형성된 제1 칩들 각각의 상부에 제2 칩을 바로 적층한다. 이에 따라, 임시 캐리어 웨이퍼를 기저 웨이퍼(10)에 붙이거나 띠는 제조 공정을 수행하지 않아도 되고, 임시 캐리어 웨이퍼를 사용하지 않아도 되므로 패키지 제조 비용을 대폭적으로 줄일 수 있다.

- [0030] 본 발명의 기술적 사상은 제1 칩 상에 제2 칩을 적충하되, 제1 칩의 두께가 제2 칩보다 두껍게 할 수 있다. 이에 따라, 제1 칩의 파손 가능성을 줄일 수 있고, 열 방출도 용이하게 할 수 있다.

- [0031] 본 발명의 기술적 사상은 제1 칩 상에 제2 칩을 적충하되, 제1 칩의 측면 및 후면을 노출할 수 있어 칩 적충 반도체 패키지의 열 방출을 용이하게 할 수 있다.

- [0032] 본 발명의 기술적 사상은 제1 칩을 복수개 포함하는 제1 칩을 포함하는 기저 웨이퍼 상에 제2 칩을 적충하되, 제2 칩의 크기를 제1 칩보다 작거나 동일하게 탑재한다. 이에 따라, 고집적화된 기저 웨이퍼에서 스크라이브 라인 영역의 크기, 예컨대 폭에 제한을 받지 않고 언더필이나 소잉 공정을 보다 용이하게 수행할 수 있어 칩 적충반도체 패키지를 신뢰성 있게 제조할 수 있다.

- 본 발명의 기술적 사상에 따르면, 제1 칩의 측면 및 후면이나, 제2 칩의 측면이 노출된 칩 적충 반도체 패키지를 얻을 수 있다. 이러한 칩 적충 반도체 패키지를 메인 칩이나 보드 기판 상에 실장하여 재차 몰딩할 경우 추가 밀봉재가 제1 칩의 후면이나 측면. 제2 칩의 측면과 잘 결합 및 부착될 수 있다.

### 도면의 간단한 설명

[0033]

[0034] 도 1 내지 도 13은 본 발명의 기술적 사상의 일 실시예에 따른 칩 적충 반도체 패키지의 제조 방법 및 이에 의해 제조된 칩 적충 반도체 패키지를 설명하기 도면들이다.

도 14 및 도 15는 본 발명의 기술적 사상의 일 실시예에 의한 제2 칩의 제조 방법을 설명하기 단면도들이다.

도 16 및 도 17은 본 발명의 기술적 사상의 일 실시예에 따른 칩 적층 반도체 패키지 제조 방법 및 이에 의해 제조된 칩 적층 반도체 패키지를 설명하기 단면도들이다.

도 18 내지 도 23은 본 발명의 기술적 사상의 일 실시예에 따른 칩 적층 반도체 패키지 제조 방법 및 이에 의해 제조된 칩 적층 반도체 패키지를 설명하기 단면도들이다.

도 24 및 도 25는 본 발명의 기술적 사상의 일 실시예에 따른 칩 적층 반도체 패키지 제조 방법 및 이에 의해 제조된 칩 적층 반도체 패키지를 설명하기 단면도들이다.

도 26은 본 발명의 기술적 사상의 일 실시예에 따른 칩 적충 반도체 패키지 제조 방법 및 이에 의해 제조된 칩 적충 반도체 패키지를 설명하기 위한 단면도이다.

도 27은 본 발명의 기술적 사상의 일 실시예에 따른 칩 적층 반도체 패키지 제조 방법 및 이에 의해 제조된 칩 적층 반도체 패키지를 설명하기 위한 단면도이다. 도 28은 본 발명의 기술적 사상의 일 실시예에 따른 칩 적층 반도체 패키지 제조 방법 및 이에 의해 제조된 칩 적층 반도체 패키지를 설명하기 위한 단면도이다.

도 29 내지 도 32는 본 발명의 기술적 사상의 일 실시예에 따른 칩 적충 반도체 패키지 제조 방법 및 이에 의해 제조된 칩 적충 반도체 패키지를 설명하기 위한 단면도들이다.

도 33 및 도 34는 본 발명의 기술적 사상의 일 실시예에 따른 칩 적층 반도체 패키지 제조 방법 및 그에 의해 제조된 칩 적층 반도체 패키지를 설명하기 위한 단면도들이다.

도 35 및 도 36은 본 발명의 기술적 사상의 일 실시예에 따른 칩 적층 반도체 패키지 제조 방법에 이용되는 제2 칩의 제조 방법을 설명하기 단면도들이다.

도 37a 내지 37f는 본 발명의 기술적 사상의 일 실시예에 따른 칩 적층 반도체 패키지 제조 방법에 이용되는 제 2 칩의 제조 방법을 설명하기 단면도들이다.

도 38은 본 발명의 기술적 사상의 일 실시예에 따른 칩 적층 반도체 패키지 제조 방법에 이용되는 제2 칩의 제조 방법을 설명하기 단면도이다.

도 39a 및 도 39b는 본 발명의 기술적 사상의 일 실시예에 의한 칩 적층 반도체 패키지를 도시한 단면도들이다.

도 40은 본 발명의 기술적 사상의 일 실시예에 따른 칩 적층 반도체 패키지의 단면도이다.

도 41은 본 발명의 기술적 사상의 일 실시예에 따른 칩 적층 반도체 패키지의 단면도이다.

도 42는 본 발명의 기술적 사상의 일 실시예에 따른 칩 적층 반도체 패키지의 단면도이다.

도 43은 본 발명의 기술적 사상의 칩 적층 반도체 패키지를 포함하는 메모리 카드를 개략적으로 보여주는 블럭구성도이다.

도 44는 본 발명의 기술적 사상의 칩 적충 반도체 패키지를 포함하는 전자시스템을 개략적으로 보여주는 블럭구성도이다.

## 발명을 실시하기 위한 구체적인 내용

[0035] 이하, 첨부된 도면을 참조하여 본 발명의 바람직한 실시예를 상세히 설명하기로 한다.

본 발명의 실시예들은 당해 기술 분야에서 통상의 지식을 가진 자에게 본 발명을 더욱 완전하게 설명하기 위하여 제공되는 것이며, 하기 실시예는 여러 가지 다른 형태로 변형될 수 있으며, 본 발명의 범위가 하기 실시예에 한정되는 것은 아니다. 오히려 이들 실시예들은 본 개시를 더욱 충실하고 완전하게 하고, 당업자에게 본 발명의 기술적 사상을 완전하게 전달하기 위하여 제공되는 것이다. 또한, 도면에서 각 층의 두께나 크기는 설명의 편의 및 명확성을 위하여 과장된 것이다.

명세서 전체에 걸쳐서, 막, 영역 또는 기판 등과 같은 하나의 구성요소가 다른 구성요소 "상에", "연결되어", 또는 "커플링되어" 위치한다고 언급할 때는, 상기 하나의 구성요소가 직접적으로 다른 구성요소 "상에", "연결되어", 또는 "커플링되어" 접촉하거나, 그 사이에 개재되는 또 다른 구성요소들이 존재할 수 있다고 해석될 수 있다. 반면에, 하나의 구성요소가 다른 구성요소 "직접적으로 상에", "직접 연결되어", 또는 "직접 커플링되어" 위치한다고 언급할 때는, 그 사이에 개재되는 다른 구성요소들이 존재하지 않는다고 해석된다. 동일한 부호는 동일한 요소를 지칭한다.

본 명세서에서 제1, 제2등의 용어가 다양한 부재, 부품, 영역, 층들 및/또는 부분들을 설명하기 위하여 사용되지만, 이들 부재, 부품, 영역, 층들 및/또는 부분들은 이들 용어에 의해 한정되어서는 안됨은 자명하다. 이들 용어는 하나의 부재, 부품, 영역, 층 또는 부분을 다른 영역, 층 또는 부분과 구별하기 위하여만 사용된다. 따라서, 이하 상술할 제1부재, 부품, 영역, 층 또는 부분은 본 발명의 가르침으로부터 벗어나지 않고서도 제2부재, 부품, 영역, 층 또는 부분을 지칭할 수 있다.

또한, "상의" 또는 "위의" 및 "하의" 또는 "아래의"와 같은 상대적인 용어들은 도면들에서 도해되는 것처럼 다른 요소들에 대한 어떤 요소들의 관계를 기술하기 위해 여기에서 사용될 수 있다. 상대적 용어들은 도면들에서 묘사되는 방향에 추가하여 소자의 다른 방향들을 포함하는 것을 의도한다고 이해될 수 있다. 예를 들어, 도면들에서 소자가 뒤집어 진다면(turned over), 다른 요소들의 상부의 면 상에 존재하는 것으로 묘사되는 요소들은 상기 다른 요소들의 하부의 면 상에 방향을 가지게 된다. 그러므로, 예로써 든 "상의"라는 용어는, 도면의 특정

[0036]

# [0038]

한 방향에 의존하여 "하의" 및 "상의" 방향 모두를 포함할 수 있다. 소자가 다른 방향으로 향한다면(다른 방향에 대하여 90도 회전), 본 명세서에 사용되는 상대적인 설명들은 이에 따라 해석될 수 있다.

- [0040] 본 명세서에서 사용된 용어는 특정 실시예를 설명하기 위하여 사용되며, 본 발명을 제한하기 위한 것이 아니다. 본 명세서에서 사용된 바와 같이, 단수 형태는 문맥상 다른 경우를 분명히 지적하는 것이 아니라면, 복수의 형태를 포함할 수 있다. 또한, 본 명세서에서 사용되는 경우 "포함한다(comprise)" 및/또는 "포함하는 (comprising)"은 언급한 형상들, 숫자, 단계, 동작, 부재, 요소 및/또는 이들 그룹의 존재를 특정하는 것이며, 하나 이상의 다른 형상, 숫자, 동작, 부재, 요소 및/또는 그룹들의 존재 또는 부가를 배제하는 것이 아니다.

- [0041] 이하의 본 발명의 실시예들은 본 발명의 이상적인 실시예들을 개략적으로 도시하는 도면들을 참조하여 설명한다. 도면들에 있어서, 예를 들면, 제조 기술 및/또는 공차(tolerance)에 따라, 도시된 형상의 변형들이 예상될 수 있다. 따라서, 본 발명 사상의 실시예는 본 명세서에 도시된 영역의 특정 형상에 제한된 것으로 해석 되어서는 아니 되며, 예를 들면 제조상 초래되는 형상의 변화를 포함하여야 한다. 이하의 본 발명의 실시예들은 어느 하나로 구현될 수 있으며, 또한, 이하의 실시예들은 하나 이상을 조합하여 구현될 수 있다.

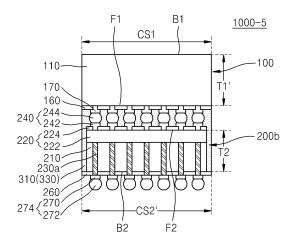

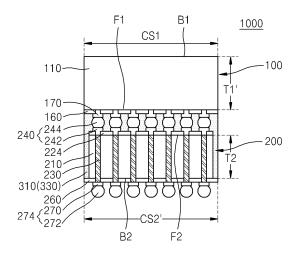

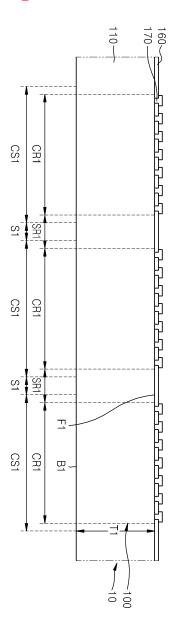

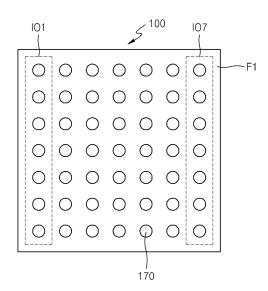

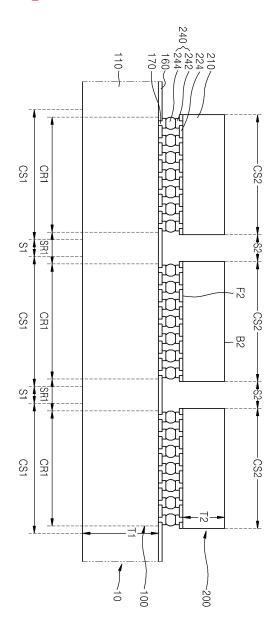

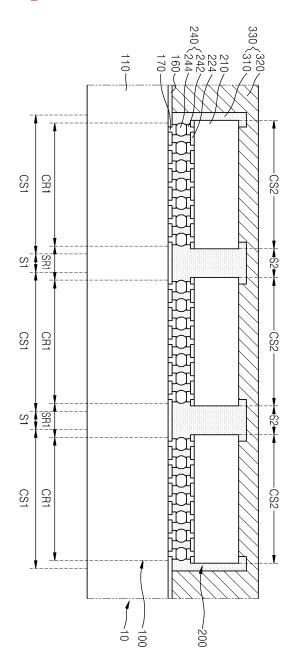

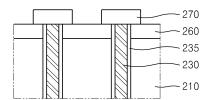

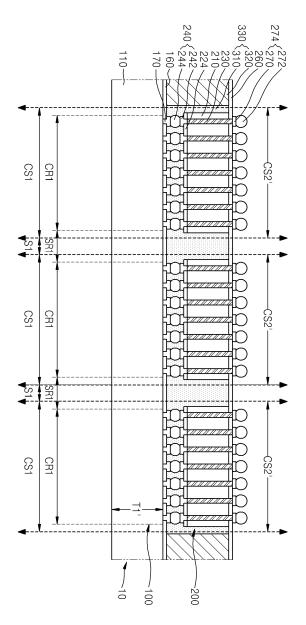

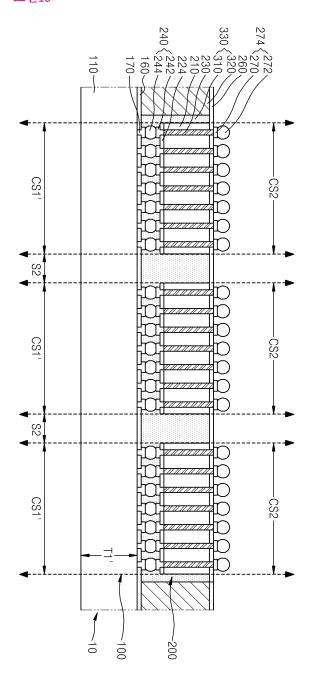

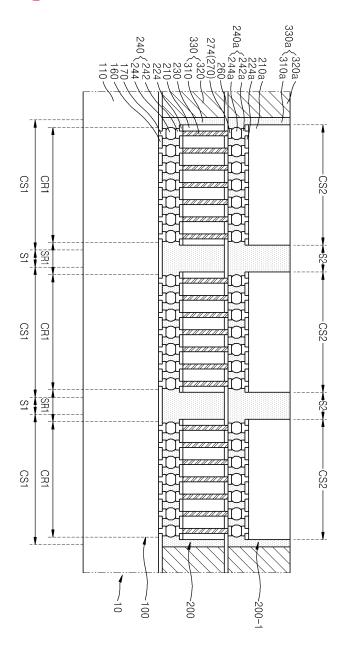

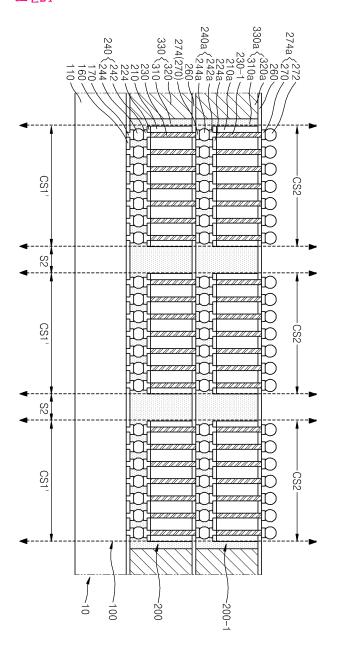

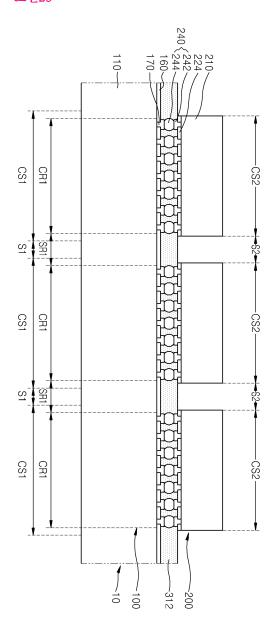

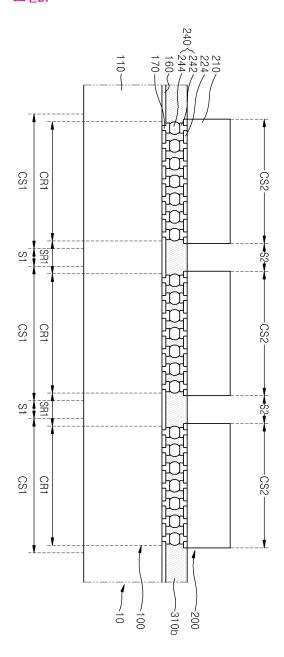

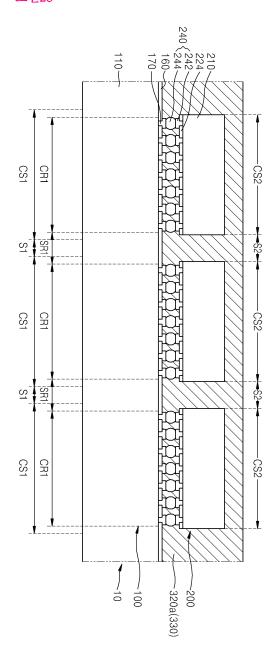

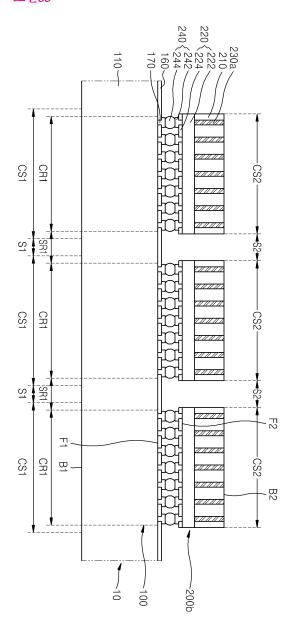

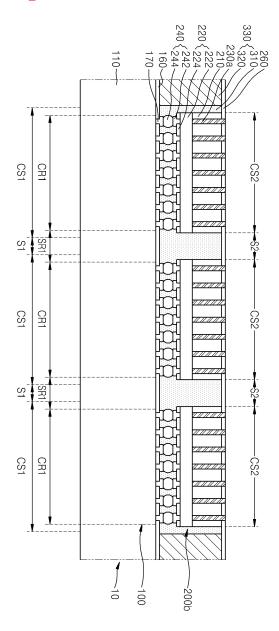

- [0042] 도 1 내지 도 13은 본 발명의 기술적 사상의 일 실시예에 따른 칩 적충 반도체 패키지의 제조 방법 및 이에 의해 제조된 칩 적충 반도체 패키지를 설명하기 도면들이다. 도 1, 도 3, 도 5 내지 도 13은 단면도들이고, 도 2 및 4는 평면도이다.

- [0043] 도 1 및 도 2를 참조하면, 제1 칩(100)을 복수개 포함하는 기저 웨이퍼(10, base wafer)를 준비한다. 기저 웨이퍼(10)는 웨이퍼 레벨에서 제1 칩(100)들을 동시에 형성하여 완성한다.

- [0044] 기저 웨이퍼(10)에서, 제1 칩 영역의 크기(size)는 CR1로 표시되어 있다. 제1 칩 영역의 크기(CR1)는 폭 또는 길이일 수 있다. 제1 칩(100)들 사이의 스크라이브 라인 영역의 크기는 SR1로 표시되어 있다. 스크라이브 라인 영역의 크기(SR1)는 폭 또는 길이일 수 있다.

- [0045] 기저 웨이퍼(10)에서 후 공정의 절단에 의해 완성되는 제1 칩(100)의 크기는 CS1로 표시할 수 있다. 제1 칩(100)의 크기(CS1)는 폭 또는 길이일 수 있다. 후공정을 통해 스크라이브 라인 영역 내에서 블레이드(blade)에 의해 절단되는 크기는 S1로 도시되어 있다. 블레이드(blade)에 의해 절단되는 크기(S1)는 폭 또는 길이일 수 있다. 블레이드(blade)에 의해 절단되는 크기(S1)는 블레이드의 폭일 수 있다. 도 1에서는 편의상 기저 웨이퍼(10)에 3개의 제1 칩(100)이 도시되어 있지만 기저 웨이퍼(10)에 수십 내지 수백 개의 칩들이 형성되어 있을 수 있다.

- [0046] 제1 칩(100)은 두께(T1)를 가질 수 있다. 제1 칩(100)은 제1 전면(F1, front side) 및 제1 전면(F1)과 반대되는 제1 후면(B1,back side)을 가질 수 있다. 제1 전면(F1)은 기저 웨이퍼(10)의 표면 측일 수 있다. 제1 칩(100)은 제1 바디층(110), 패시베이션층(160) 및 제1 연결 부재(170)를 포함할 수 있다.

- [0047] 제1 바디층(110)은 실리콘 기판(미도시), 상기 실리콘 기판 상에 형성된 집적 회로층 및 상기 집적 회로층을 덮는 층간 절연층(미도시)을 포함할 수 있다. 제1 바디층(110)은 제1 칩(100)과 마찬가지로 제1 전면(F1) 및 제1 전면(F1)과 반대되는 제1 후면(B1)을 가질 수 있다.

- [0048] 제1 연결 부재(170)는 범프 패드일 수 있다. 제1 연결 부재(170)는 제1 칩(100)에 마련되는 도전 패드일 수 있다. 제1 연결 부재(170)는 도 2에 도시한 바와 같이 제1 전면(F1)에 형성될 수 있고 좌측에 입출력 패드 그룹 (I01)이 형성될 수 있고, 우측에 입출력 패드 그룹(I07)이 형성될 수 있다. 입출력 패드 그룹들(I01, I07)은 예시적인 것이며 본 발명의 기술적 사상이 이에 한정되지 않는다.

- [0049] 입출력 패드 그룹(I01, I07)은 후에 탑재되는 제2 칩(도 3의 200)의 제2 연결 부재(도 3의 240)에 대해 미러 (mirror) 대칭 형태로 형성될 수 있다. 다시 말해, 제1 연결 부재(170)는 후에 탑재되는 제2 칩(도 3의 200)의 제2 연결 부재(도 3의 240)를 미리 고려하여 미러 대칭 형태로 형성될 수 있다. 제1 연결 부재(170)는 도전성 물질로 형성될 수 있다. 제1 연결 부재(170)는 알루미늄(Al)이나 구리(Cu) 등으로 형성될 수 있고, 펄스 도금이나 직류 도금 방법을 통해 형성될 수 있다. 그러나 제1 연결 부재(170)는 상기 재질이나 방법에 한정되는 것은 아니다.

- [0050] 패시베이션층(160)은 바디층(110) 상면으로 형성되고 상기 제1 바디층(110)을 외부로부터 보호할 수 있다. 패시베이션층(160)은 제1 연결 부재(170)들 사이를 절연할 수 있다. 패시베이션층(160)은 산화막 또는 질화막으로 형성될 수 있고, 또는 산화막과 질화막의 이중층으로 형성될 수 있다. 또한, 패시베이션층(160)은 고밀도 플라즈마 화학기상 증착(HDP-CVD) 공정을 이용하여 산화막, 예컨대 실리콘 산화막(SiO2)으로 형성할 수 있다.

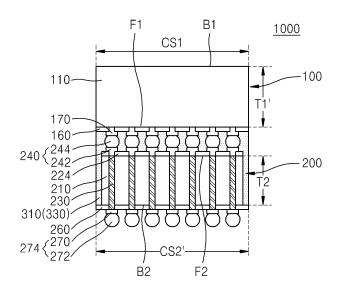

- [0051] 도 3 및 도 4를 참조하면, 제2 전면(F2) 및 제2 전면(F2)에 반대되는 제2 후면(B2)을 갖는 제2 칩(200)을 복수 개 준비한다. 제2 칩(200)의 구체적인 제조 과정은 후의 도 14 및 도 15에서 설명한다. 제2 칩(200)은 제2 바디 층(210), 패시베이션층(224), 및 제2 연결 부재(240)를 포함할 수 있다.

- [0052] 제2 바디층(210)은 제1 칩(100)과 마찬가지로 실리콘 기판(미도시), 상기 실리콘 기판 상에 형성된 집적 회로층 및 상기 집적 회로층을 덮는 층간 절연층(미도시)을 포함할 수 있다. 제2 바디층(210)은 제2 전면(F2) 및 제2 전면(F2)과 반대되는 제2 후면(B2)을 가질 수 있다. 제2 바디층(210)의 제2 전면(F2)은 집적 회로층이 형성될 수 있다. 제2 바디층(210)의 제2 전면(F2)은 소자 구성 요소들이 형성되는 활성면일 수 있다. 제2 바디층(210)의 제2 후면(B2)은 소자 구성 요소들이 형성되지 않는 비활성면일 수 있다. 패시베이션층(224)은 제2 바디층(210) 하부로 형성될 수 있다.

- [0053] 제2 연결 부재(240)는 범프 패드(242) 및 범프(244)를 포함할 수 있다. 범프 패드(242)는 패시베이션층(224) 상에 도전성 물질로 형성될 수 있다. 범프 패드(242) 상에는 UBM(Under Bump Metal, 미도시)이 형성될 수 있다. 범프 패드(242)는 앞서 제1 연결 부재(170)와 동일 재질 또는 다른 재질로 형성될 수 있고, 또한 형성 방법도 동일 또는 다르게 형성될 수 있다.

- [0054] 범프(244)는 범프 패드(242) 상에 형성될 수 있다. 범프(244)는 도전성 재질로 형성되며, 구리(Cu), 알루미늄 (A1), 금(Au), 솔더(solder) 등으로 형성될 수 있다. 그러나 범프(244)의 재질이 그에 한정되는 것은 아니다.

- [0055] 기저 웨이퍼(10)에 형성된 제1 칩들(100) 각각의 상부에 제2 칩(200)을 적충한다. 즉, 제1 칩(100)의 제1 전면 (F1) 상에 제2 칩(200)의 제2 전면(F2)을 대향하여 적충한다. 제2 연결 부재(240)는 제1 전면(F1) 및 제2 전면 (F2) 상에서 상기 제1 연결 부재(170)와 전기적으로 연결된다. 적충은 제2 칩(200)의 제2 연결 부재(240)를 제1 칩(100)의 제1 연결 부재(170) 상에 열 압착 방법을 통해 접착함으로써 이루어질 수 있다. 제2 연결 부재(240)는 제1 칩(100)의 제1 연결 부재(170)에 연결될 수 있다.

- [0056] 도 4에 도시한 바와 같이 제2 연결 부재(240)는 제2 전면(F2)에 형성될 수 있다. 제2 연결 부재(240)는 앞서 설명한 바와 같이 제1 연결 부재(도 1 및 도 2의 170)에 대응하여 미러(104) 대칭 형태로 형성될 수 있다. 즉, 제 2 연결 부재(240)는 좌측에 입출력 패드 그룹(I07)이 형성될 수 있고, 우측에 입출력 패드 그룹(I01)이 형성될 수 있다. 다시 말해, 제2 칩(200)의 입출력 패드 그룹(I01, I07)은 제1 칩(100)의 제1 연결 부재(170)에 대해 미러(mirror) 대칭 형태로 형성될 수 있다.

- [0057] 제2 칩(200)의 제2 연결 부재(240)의 배치는 제1 칩(100)의 제1 연결 부재(170)의 배치를 미러 대칭 형태로 할 경우 제2 칩(200)을 제1 칩(100)상에 적흥할 수 있다. 제2 칩(200)은 제1 칩(100)과 이종의 칩일 수 있다. 또한, 제2 칩(200)은 제1 칩(100)과 동종의 칩일 수도 있다.

- [0058] 제2 칩(200)은 두께(T2)를 가질 수 있다. 제2 칩(200)의 두께(T2)는 제1 칩(100)의 두께(T1)보다 작을 수 있다. 제2 칩(200)의 크기(CS2)는 폭 또는 길이일 수 있다. 제2 칩(200)의 크기(CS2)는 제1 칩(100)의 크기(CS1)보다 작거나 같을 수 있다.

- [0059] S2는 제2 칩용 웨이퍼(미도시)의 스크라이브 라인 영역 내에서 블레이드(blade)에 의해 절단되는 크기로써 폭 또는 길이일 수 있고, S1보다는 크게 형성한다. S2는 블레이드의 폭일 수 있다. 제2 칩(200)의 크기(CS2)를 제1 칩(100)의 크기(CS1)보다 작거나 같게 하고, 블레이드에 의해 절단되는 크기(S2)를 S1보다 크게 하기 때문에 후 의 언더필 공정 및 절단 공정을 용이하게 수행할 수 있다.

- [0060] 앞서 설명한 바와 같이 본 발명의 기술적 사상은 도 3 및 도 4에 도시한 바와 같이 기저 웨이퍼(10)에 형성된 제1 칩들(100) 각각의 상부에 제2 칩(200)을 적충하는 것을 포함한다. 즉, 본 발명의 기술적 사상은 제1 칩들 (100)을 포함하는 기저 웨이퍼(10) 상에 제2 칩(200)을 적충하는 COW(chip on wafer) 형태로 적충한다.

- [0061] 그리고, 본 발명의 기술적 사상은 제1 칩(100)과 제2 칩(200)의 적층시 임시 캐리어 웨이퍼(temporary carrier wafer)를 이용하지 않고 기저 웨이퍼(10)에 형성된 제1 칩들(100) 각각의 상부에 제2 칩(200)을 바로 적층한다. 이에 따라, 임시 캐리어 웨이퍼를 기저 웨이퍼(10)에 붙이고 다시 분리하는 제조 공정을 수행하지 않아도 되고, 임시 캐리어 웨이퍼를 사용하지 않아도 되므로 패키지 제조 비용을 대폭적으로 줄일 수 있다.

- [0062] 도 5를 참조하면, 제1 칩(100)과 제2 칩(200)의 연결 부분을 채우는 언더필(310)을 형성한다. 제1 칩(100) 상에 적충되는 제2 칩(200)의 크기를 작게 하여 고집적화된 웨이퍼에서 스크라이브 라인 영역의 크기, 예컨대 스크라이브 라인 영역의 폭이 좁더라도 언더필 공정을 용이하게 수행할 수 있다. 언더필(310)은 제1 칩(100) 및 제2 칩(200)의 연결 부분, 즉 제1 칩(100)의 제1 연결 부재(170)와 제2 연결 부재(240)가 연결되는 부분을 채울 수

있다. 언더필(310)은 에폭시 수지와 같은 언더필 수지로 형성될 수 있고, 실리카 필러(filler)나 플럭스(flux) 등이 포함될 수 있다. 언더필(310)은 후에 형성되는 몰딩재와 다른 재질로 형성될 수 있지만 동일 재료로 형성될 수도 있다.

- [0063]

- 도시된 바와 같이, 언더필(310)은 제1 칩(100) 및 제2 칩(200)의 연결 부분뿐만 아니라, 상기 연결 부분에서 확장하여 제2 칩(200)의 측면 및 제2 칩(200)의 후면 일부분을 밀봉시킬 수 있다. 즉, 언더필(310)은 제1 칩(10 0)과 제2 칩(200)의 연결 부분만을 채울 수도 있지만, 도시된 바와 같이 제1 칩(100)과 제2 칩(200)의 연결 부분을 채우면서 제2 칩(200)의 측면을 감싸도록 형성될 수도 있다. 언더필(310)은 인접하는 언더필(310)과 겹쳐지도록 형성될 수도 있다. 이와 같이 언더필(310)이 제2 칩(200)의 측면을 감싸게 되면, 반도체 패키지 완성 후에, 언더필(310)이 측면으로 노출될 수도 있다. MUF(molded underfill)공정을 이용하는 경우에는 본 단계의 언더필 공정은 생략될 수도 있다.

- [0064]

- 도 6 및 도 7을 참조하면, 도 6에 도시한 바와 같이 기저 웨이퍼(10) 상에 접착된 제2 칩(200)을 몰딩하는 몰딩 재(320)를 형성한다. 몰딩재(320)는 레진과 같은 폴리머로 형성될 수 있다. 예컨대, 몰딩재(320)는 EMC(Epoxy Molding Compound)로 형성될 수 있다. 이에 따라, 제1 칩(100) 및 제2 칩(200)은 언더필(310)과 몰딩재(320)를 구비한 제1 밀봉재(330)로 밀봉된다. 제1 밀봉재(330)는 제2 칩(200)의 측면들 및 후면을 밀봉할 수 있다. 언더 필(310)의 존재로 인해 몰딩재(320)는 언더필(310)의 측면을 밀봉할 수 있다.

- [0065]

- 도 7에 도시한 바와 같이, 제1 밀봉재(330) 상면을 그라인딩하여, 제2 칩(200)의 상면(후면)을 노출시킬 수 있다. 제1 밀봉재(330)의 상면은 제2 칩(200)의 상면(후면)과 동일 수평면을 구성할 수 있다. 제2 칩(200) 상면은, 집적 회로층이 형성되지 않는 반도체 기판(즉 실리콘 기판)의 후면일 수 있고, 그에 따라, 실리콘 기판의 후면이 외부로 노출될 수 있다.

- [0066]

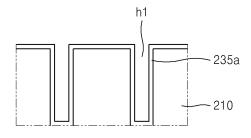

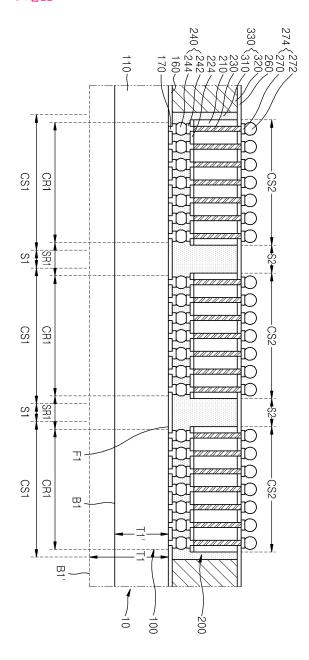

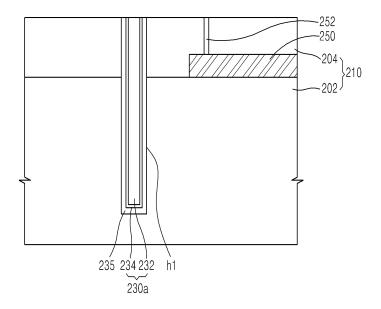

- 도 8 내지 도 10을 참조하면, 도 8에 도시한 바와 같이 제2 칩(200)의 제2 바디층(210) 내에 트랜치(h1, 비아홀)를 형성한다. 트랜치(h1)는 제2 바디층(210)을 관통하도록 형성될 수 있다. 트랜치(h1)는 제2 바디층(210)의 후면에서 전면까지 형성할 수 있다. 트랜치(h1)는 제2 칩(200)의 후면에서부터 전면까지 형성할 수 있다. 트랜치(h1)는 제2 연결 부재(240)를 노출하게 형성할 수 있다.

- [0067]

- 도 9에 도시한 바와 같이 트랜치(h1)를 매립하는 제1 관통 실리콘 비아(230)를 형성한다. 제1 관통 실리콘 비아(230)는 제2 연결 부재(240)와 전기적으로 연결될 수 있다. 제2 칩(200)의 후면, 즉 제2 바디층(210)의 후면 상에 보호층(260)과 제3 연결 부재(도 11의 274)를 구성하는 범프 패드(270)를 형성한다. 범프 패드(270)는 도전성 물질로 형성될 수 있다. 범프 패드(270) 상에는 UBM(Under Bump Metal, 미도시)이 형성될 수 있다. 범프 패드(270)는 앞서 제1 연결 부재(170)와 동일 재질 또는 다른 재질로 형성될 수 있고, 또한 형성 방법도 동일 또는 다르게 형성될 수 있다.

- [0068]

- 여기서, 도 10a 내지 도 10d를 참조하여 제1 관통 실리콘 비아(230) 및 제3 연결 부재(270)의 형성 과정을 자세히 설명한다.

- [0069]

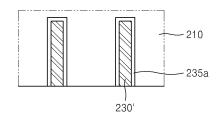

- 도 10a에 도시한 바와 같이 제2 바디층(210)의 표면 및 트랜치(h1, 비아홀)의 내벽에 스페이서 절연층(235a)을 형성한다. 스페이서 절연층(235a)은 트랜치(h1)에 형성되는 관통 실리콘 비아(235)와 제2 바디층(210)간을 절연 하는 역할을 수행한다.

- [0070]

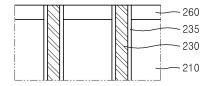

- 도 10b에 도시한 바와 같이 트랜치(h1) 내에 제1 관통 실리콘 비아(230)를 형성한다. 제1 관통 실리콘 비아(230)은 다양한 제조 공정을 통하여 형성할 수 있다. 예컨대, 트랜치(h1)의 내벽 및 제2 바디층(210) 상에 스페이서 절연층(235a)를 형성한다. 이어서, 트랜치(h1)를 매립하고 스페이서 절연층(235a) 상에 도전층을 형성한 후 평탄화한다. 이에 따라, 제1 관통 실리콘 비아(230)와, 제1 관통 실리콘 비아(230)와 제2 바디층(210)을 절연시키기 위한 패턴된 스페이서 절연층(235)이 형성된다.

- [0071]

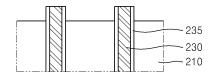

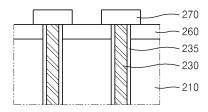

- 도 10c에 도시한 바와 같이, 제2 바디층(210)을 리세스시킨 후, 상기 제1 관통 실리콘 비아(230)의 양측벽 및 리세스된 제2 바디층(210) 상에 보호층(260)을 형성한다. 보호층(260)은 제2 바디층(210)을 보호하는 역할을 수행한다. 보호층(260)은 제1 관통 실리콘 비아들(230) 사이를 절연하는 역할을 수행한다. 도 10d에 도시한 바와 같이, 제1 관통 실리콘 비아(230) 상에 범프 패드(270)를 형성한다.

- [0072]

- 도 11을 참조하면, 제2 칩(200)의 범프 패드(270) 상에 범프(272)를 형성한다. 이에 따라, 범프 패드(270) 및 범프(272)로 구성되는 제3 연결 부재(274)를 형성한다. 범프(272)는 도전성 재질로 형성되며, 구리(Cu), 알루미늄(Al), 금(Au), 솔더(solder) 등으로 형성될 수 있다. 그러나 범프(272)의 재질이 그에 한정되는 것은 아니다.

제3 연결 부재(274) 상에는 후술하는 바와 같이 제3 칩이 더 적충될 수 있다.

- [0073] 그리고, 제1 칩(100)의 후면(B1')을 연마하여 제1 칩(100)의 두께를 줄인다. 이에 따라, 제1 칩(100)의 최종 두 께는 T1'이 될 수 있다. 제1 칩(100)의 최종 두께(T1')를 제2 칩(200)의 두께(T2)보다 두껍게 조절할 수 있다.

- [0074] 도 12 및 도 13을 참조하면, 도 13은 제1 칩(100)을 위에 위치시켜 도시한다. 기저 웨이퍼(10) 및 밀봉재(330)를 소잉(sawing, 절단)하여 각각의 칩 적층 반도체 패키지(1000)로 분리한다. 도 12에서는 제1 칩(100)의 크기 (CS1)를 기준으로 기저 웨이퍼(10) 및 밀봉재(330)를 절단한다. S2보다 작은 S1의 블레이드 폭을 기준으로 기저 웨이퍼(10)와 제2 칩들(200) 사이의 밀봉재(330)를 절단하기 때문에 매우 용이하게 절단 공정을 수행할 수 있다. 이렇게 될 경우, 밀봉재(330), 즉 언더필(310)을 포함하는 제2 칩(200)의 크기는 CS2에서 CS2'로 약간 크게 될 수 있다.

- [0075] 앞서와 같이 절단 공정을 통하여 개개의 칩 적층 반도체 패키지(1000)를 형성하고 나면, 제1 칩(100)의 양측면 이 노출된다. 이렇게 할 경우, 칩 적층 반도체 패키지(1000)를 보드 기판 상에 실장하여 재차 몰딩할 경우 추가 밀봉재가 제1 칩(100)의 측면과 잘 결합 및 부착될 수 있다.

- [0076] 본 실시예의 칩 적층 반도체 패키지 제조 방법에 따르면, 제1 칩(100)을 복수개 포함하는 기저 웨이퍼(10) 상에, 제2 칩(200)을 탑재한다. 이 과정에서, 제2 칩(200)의 크기(CS2)는 제2 칩(200)을 포함하는 웨이퍼를 절단하여 제2 칩(200)을 준비할 때, 블레이드폭(S2)을 크게 함으로써 제1 칩(100)보다 작거나 동일하게 준비한다.

- [0077] 이에 따라, 고집적화된 웨이퍼에서 스크라이브 라인 영역의 크기, 예컨대 스크라이브 라인 영역의 폭이 좁더라도 언더필 공정을 용이하게 수행할 수 있다. 또한, 기저 웨이퍼(10) 및 밀봉재(330)를 절단할 때 보다 용이하게수행하여 칩 적층 반도체 패키지(1000)를 제조할 수 있다.

- [0078] 본 실시예의 칩 적층 반도체 패키지 제조 방법에 따르면, 제1 칩(100)이 포함된 기저 웨이퍼(10) 상에 제2 칩 (200)을 적층하고 밀봉재(330)를 형성한 후 절단하여 개개의 칩 적층 반도체 패키지를 형성하고 나면, 제1 칩 (100)의 양측면이 노출된다. 이렇게 할 경우, 칩 적층 반도체 패키지를 보드 기판 상에 실장하여 재차 몰딩할 경우 추가 밀봉재가 제1 칩(100)의 측면과 잘 결합 및 부착될 수 있다.

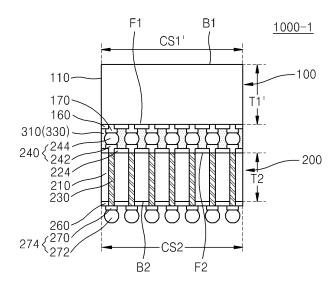

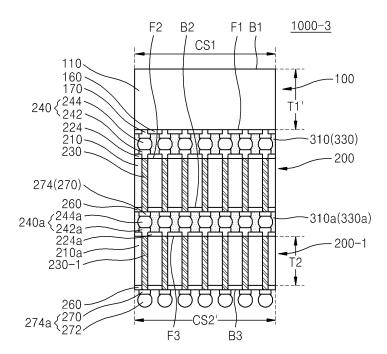

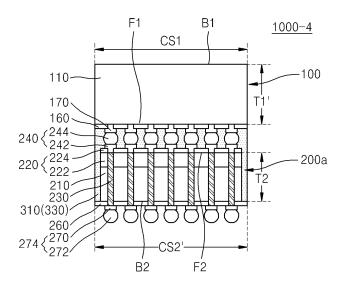

- [0079] 여기서, 도 13을 참조하여 앞서 칩 적층 반도체 패키지의 제조 방법에 의해 제조된 칩 적층 반도체 패키지 (1000)의 구조 및 특징에 대하여 간단히 설명한다.

- [0080] 구체적으로, 도 13의 칩 적층 반도체 패키지(1000)는 제1 칩(100)을 위에 위치시켜 도시하며, 제1 칩(100), 제2 칩(200) 및 밀봉재(330)를 포함할 수 있다. 제1 칩(100)은 제1 바디충(110), 패시베이션충(160) 및 제1 연결 부재(170)를 포함할 수 있다. 제1 칩(100)은 제1 전면(F1) 및 이에 반대되는 제1 후면(B1)을 가질 수 있다. 제1 연결 부재(170)는 제1 전면(F1)에 제2 칩(200)의 제2 연결 부재(240)에 대해 미러(mirror) 대칭 형태로 형성될 수 있다.

- [0081] 제1 칩(100)의 아래에 제2 칩(200)이 위치할 수 있다. 제2 칩(200)은 제2 바디층(210), 패시베이션층(224), 제 1 관통 실리콘 비아(230) 및 제2 연결 부재(240)를 포함할 수 있다. 제2 칩(200)은 제2 전면(F2) 및 이에 반대되는 제2 후면(B2)을 가진다. 제2 연결 부재(240)는 상기 제1 전면(F1) 및 제2 전면(F2) 사이에서 상기 제1 연결 부재(170) 및 제1 관통 실리콘 비아(230)와 전기적으로 연결된다.

- [0082] 제2 칩(200)의 하부에는 보호층(260) 및 제3 연결 부재(274)가 형성될 수 있다. 제3 연결 부재(274)는 범프 패드(270) 및 범프(272)로 구성될 수 있고, 범프(272)는 외부로 노출되어 있다. 제3 연결 부재(274)는 외부 부재와 연결할 수 있다.

- [0083] 밀봉재(330)는 제1 칩(100) 및 제2 칩(200)의 연결 부분, 즉 제1 칩(100)의 제1 연결 부재(170)와 제2 연결 부재(240)가 연결되는 부분에 채워져 있다. 밀봉재(330)는 제2 칩(200)의 양측면을 둘러싸도록 형성될 수 있다. 따라서, 제2 칩(200)의 양측면에 형성된 밀봉재(330)는 제1 칩(100) 및 제2 칩(200)의 연결 부분에 형성된 밀봉재(330)와 동일한 소재로 이루어질 수도 있다.

- [0084] 제1 칩(100)의 후면(B1)은 밀봉재(330)가 형성되지 않고 노출되어 있다. 제1 칩(100)의 양측면도 밀봉재가 형성되어 있지 않아 노출되어 있다. 이에 따라, 칩 적충 반도체 패키지(1000)를 후술하는 바와 같이 메인 칩이나 보드 기판 상에 실장하여 재차 몰딩할 경우 추가 밀봉재가 제1 칩(100)의 상면이나 제1 칩(100)의 측면과 잘 결합 및 부착될 수 있다.

- [0085] 제2 칩(200)의 양측면을 둘러싸도록 형성된 밀봉재(330)의 양단부가 제1 칩(100)의 모서리와 수직적으로 일치되는 구조를 갖는다. 다시 말해, 밀봉재(330)를 포함하는 제2 칩(200)의 크기(CS2')는 제1 칩(100)의 크기(CS1)와 동일하게 할 수 있다.

- [0086] 제1 칩(100)의 최종 두께(T1')가 제2 칩(200)의 두께(T2)보다 두껍게 할 수 있다. 이에 따라, 제1 칩(100)의 파손 가능성을 줄일 수 있고 열 방출을 용이하게 할 수 있다. 또한, 제1 칩(100)의 측면 및 후면(B1)을 노출할 수 있어 칩 적층 반도체 패키지(1000)의 열 방출을 용이하게 할 수 있다.

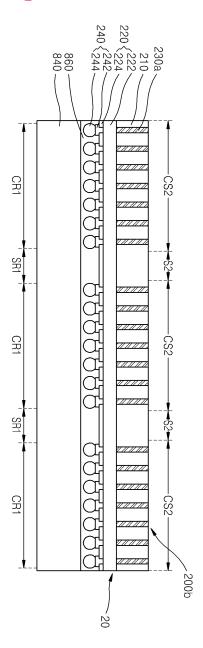

- [0087] 도 14 및 도 15는 본 발명의 기술적 사상의 일 실시예에 의한 제2 칩의 제조 방법을 설명하기 단면도들이다. 도 14 및 도 15는 도 3의 제2 칩의 제조 방법을 설명하기 단면도이다.

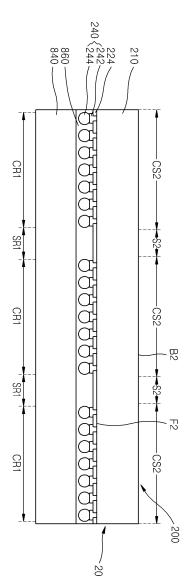

- [0088] 도 14를 참조하면, 다수의 제2 칩들(200)을 포함한 웨이퍼(20)를 준비한다. 웨이퍼(20)는 지지 기판(840) 상에 접착 부재(860)를 통해 접착되어 준비될 수 있다. 웨이퍼(20)에서, 칩 영역의 크기(size)는 제1 칩(100)과 마찬 가지로 CR1로 표시되어 있다. 칩 영역의 크기(CR1)는 폭 또는 길이일 수 있다. 제2 칩(200)들 사이의 스크라이브 라인 영역의 크기도 제1 칩(100)과 마찬가지로 SR1로 표시되어 있다. 스크라이브 라인 영역의 크기(SR1)는 폭 또는 길이일 수 있다.

- [0089] 제2 칩(200)은 제2 바디층(210), 패시베이션층(224), 및 제2 연결 부재(240)를 포함할 수 있다. 제2 칩(200)은 제2 전면(F2) 및 제2 전면(F2)에 반대되는 제2 후면(B2)을 가질 수 있다. 앞서 설명한 바와 같이 제2 전면(F2)은 소자 구성 요소들이 형성되는 활성면일 수 있고, 제2 후면(B2)은 비활성면일 수 있다.

- [0090] 지지 기판(840)은 실리콘, 게르마늄, 실리콘-게르마늄, 갈륨-비소(GaAs), 유리, 플라스틱, 세라믹 기판 등으로 형성될 수 있다. 접착 부재(860)는 NCF, ACF, 순간 접착제, 열경화성 접착제, 레이저 경화형 접착제, 초음파 경화형 접착제, NCP 등으로 형성될 수 있다. 웨이퍼(20)는 제2 연결 부재(240)가 지지 기판(800)을 향하도록 접착될 수 있다. 즉, 웨이퍼(20)는 제2 전면(F2)이 지지 기판(800)을 향하도록 접착될 수 있다.

- [0091] 도 15를 참조하면, 웨이퍼(20)의 스크라이브 라인 영역을 따라 소잉(sawing, 절단)하여 각각의 제2 칩(200)들로 분리한다. 웨이퍼(20)에서 후 공정의 절단에 의해 완성되는 제2 칩(200)의 크기는 CS2로 표시할 수 있다. 제2 칩(200)의 크기(CS1)는 폭 또는 길이일 수 있다. 스크라이브 라인 영역 내에서 블레이드(blade)에 의해 절단되는 크기는 S2로 도시되어 있다. 블레이드(blade)에 의해 절단되는 크기(S2)는 폭 또는 길이일 수 있다. 블레이드(blade)에 의해 절단되는 크기(S2)는 블레이드의 폭일 수 있다.

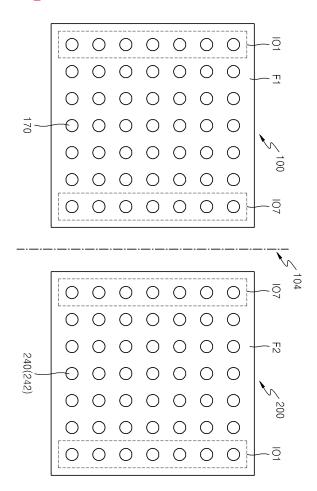

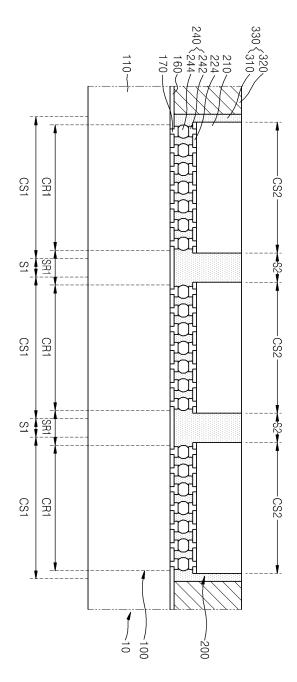

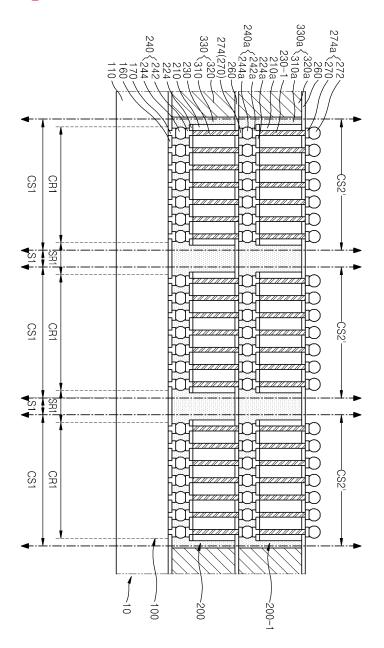

- [0092] 도 16 및 도 17은 본 발명의 기술적 사상의 일 실시예에 따른 칩 적층 반도체 패키지 제조 방법 및 이에 의해 제조된 칩 적층 반도체 패키지를 설명하기 단면도들이다.

- [0093] 구체적으로, 도 16 및 도 17의 실시예는 도 1 내지 도 13의 실시예와 비교할 때, 기저 웨이퍼(10) 및 밀봉재 (330)의 절단 공정을 제외하고는 동일하다. 도 16 및 도 17에서, 앞서 도 1 내지 도 13과 중복된 내용은 편의상 생략하거나 간략하게 설명한다.

- [0094] 먼저, 도 1 내지 도 11에 도시한 제조 공정을 수행한다. 이렇게 되면, 제1 칩(100)들을 포함하는 기저 웨이퍼 (10) 상에 밀봉재(330)로 밀봉된 복수개의 제2 칩(200)들이 위치한다.

- [0095] 도 16을 참조하면, 제2 칩(200)의 폭(CS2)을 기준으로 기저 웨이퍼(10) 및 밀봉재(330)를 절단한다. 앞서 설명한 바와 같이 S2는 블레이드 폭일 수 있고, S2의 블레이드 폭을 기준으로 기저 웨이퍼(10)를 용이하게 절단할수 있다. 이렇게 될 경우, 제1 칩(100)의 크기는 CS1에서 CS1'으로 약간 작게 된다.

- [0096] 도 17을 참조하면, 절단 공정을 통하여 개개의 칩 적층 반도체 패키지(1000-1)를 형성하고 나면, 제1 칩(100) 및 제2 칩(200)의 양측면이 노출된다. 도 16 및 도 17에 도시한 실시예의 칩 적층 반도체 패키지 제조 방법에 따르면, 도 1 내지 도 13과 마찬가지로 제2 칩(200)을 포함하는 웨이퍼를 절단하여 제2 칩(200)을 준비할 때, 제2 칩(200)의 크기는, 블레이드폭(S2)을 크게 함으로써 제1 칩(100)보다 작거나 동일하게 준비한다. 이에 따라, 기저 웨이퍼(10) 및 밀봉재(330)를 절단할 때 보다 용이하게 수행하여 칩 적층 반도체 패키지(1000-1)를 제조할 수 있다.

- [0097] 도 16 및 도 17에 도시한 실시예의 칩 적층 반도체 패키지 제조 방법에 따르면, 제1 칩(100)의 상면 및 양측면을 노출시킨다. 더하여, 제2 칩(200)의 양측면도 노출시킨다. 이렇게 할 경우, 칩 적층 반도체 패키지(1000-1)를 보드 기판 상에 실장하여 재차 몰딩할 경우 추가 밀봉재가 제1 칩(100) 및 제2 칩(200)의 측면과 잘 결합 및 부착될 수 있다.

- [0098] 여기서, 도 17을 참조하여 앞서 칩 적충 반도체 패키지의 제조 방법에 의해 제조된 칩 적충 반도체 패키지의 구조 및 특징에 대하여 간단히 설명한다.

- [0099] 구체적으로, 도 17의 칩 적충 반도체 패키지(1000-1)는 제2 칩(200)의 양측면이 노출된 것을 제외하고는 도 13 의 칩 적충 반도체 패키지(1000)와 동일하다.

- [0100] 밀봉재(330)는 제1 칩(100) 및 제2 칩(200)의 연결 부분, 즉 제1 칩(100)의 제1 연결 부재(170)와 제2 연결 부 재(240)가 연결되는 부분을 채워져 있으나, 제2 칩(200)의 양측면에는 형성되어 있지 않다. 물론, 제1 칩(100)의 양측면도 밀봉재(330)가 형성되어 있지 않아 노출되어 있다.

- [0101] 이에 따라, 칩 적층 반도체 패키지(1000-1)를 보드 기판 상에 실장하여 재차 몰딩할 경우 추가 밀봉재가 제1 칩 (100)의 후면 및 양측면이나 제2 칩(200)의 측면과 잘 결합 및 부착될 수 있다. 제2 칩(200)의 양단부가 제1 칩 (100)의 모서리와 수직적으로 일치되는 구조를 갖는다. 다시 말해, 제2 칩(200)의 크기(CS2)는 제1 칩(100)의 크기(CS1)와 동일한 크기를 갖는다.

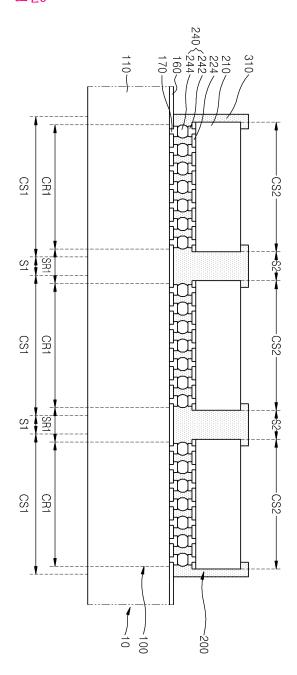

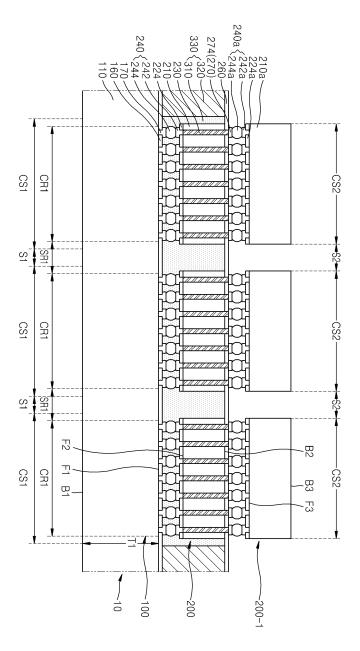

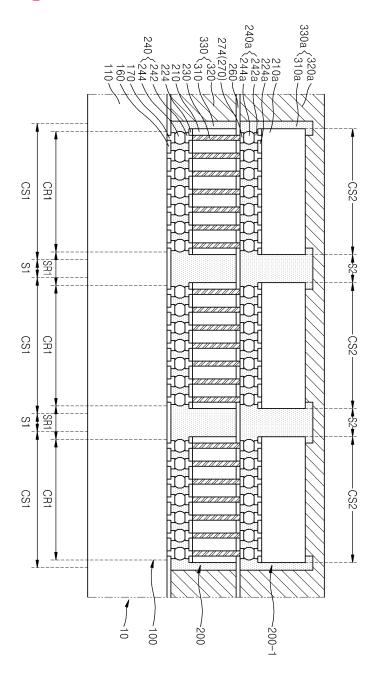

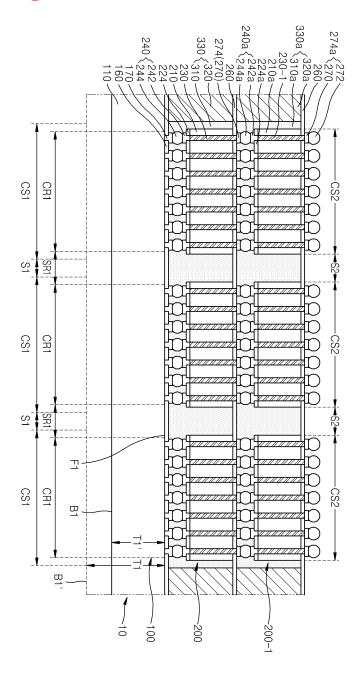

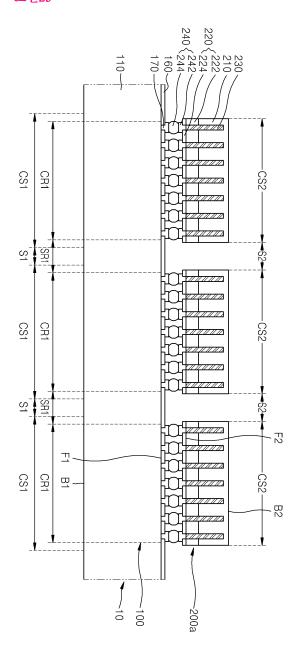

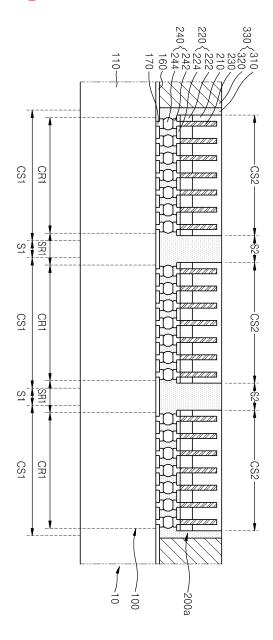

- [0102] 도 18 내지 도 23은 본 발명의 기술적 사상의 일 실시예에 따른 칩 적층 반도체 패키지 제조 방법 및 이에 의해 제조된 칩 적층 반도체 패키지를 설명하기 단면도들이다.

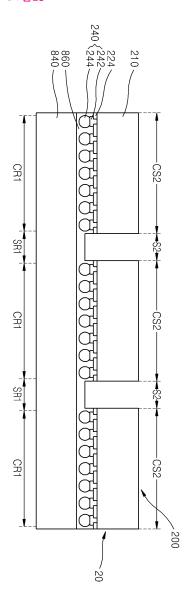

- [0103] 구체적으로, 도 18 내지 도 23의 실시예는 도 1 내지 도 13의 실시예와 비교할 때 제2 칩(200) 상에 제3 칩 (200-1)을 더 적층하여 칩 적층 반도체 패키지(1000-2)를 형성한 것을 제외하고는 동일하다. 도 18 내지 도 23 에서는 편의상 제3 칩(200-1)을 하나 적충하는 것을 예로 들고 있지만, 하나 이상의 복수개의 제3 칩(200-1)을 적층할 수 도 있다.

- [0104] 먼저, 도 1 내지 도 9에 도시한 제조 공정을 수행한다. 이렇게 되면, 제1 칩(100)들을 포함하는 기저 웨이퍼 (10) 상에 밀봉재(330)로 밀봉된 복수개의 제2 칩(200)들이 위치하고, 제2 칩(200)의 제2 후면(B2) 상에는 제3 연결 부재(274)의 구성 요소로써 범프 패드(270)가 형성되어 있다.

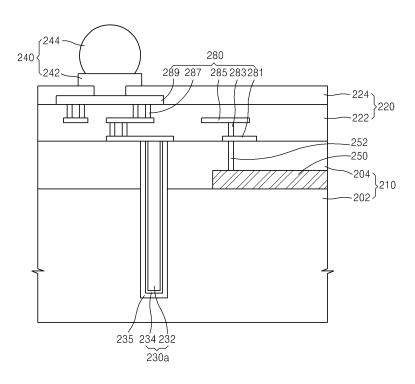

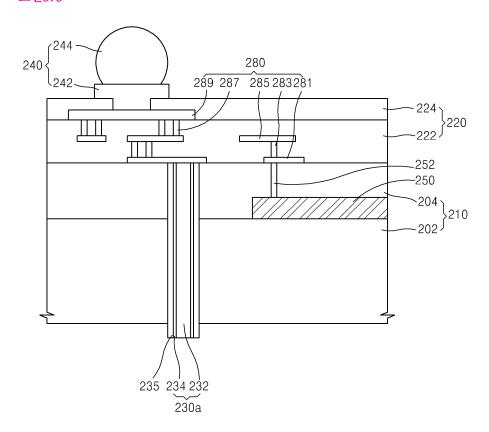

- [0105] 도 18을 참조하면, 제3 칩(200-1)을 준비한다. 제3 칩(200-1)은 앞서 도 14 및 도 15에 도시한 제2 칩(200)과 동일한 구조일 수 있고, 동일하게 제조될 수 있다. 제3 칩(200-1)은 제3 전면(F3) 및 제3 전면(F3)에 반대되는 제3 후면(B3)을 가질 수 있다. 제3 칩(200-1)은 제3 바디층(210a), 패시베이션층(224a) 및 제4 연결 부재 (240a)를 가질 수 있다. 제3 바디층(210a)은 제2 칩(200)의 제2 바디층(210)에 해당되는 것으로, 실리콘 기판, 집적 회로층 및 층간 절연층을 포함할 수 있다.

- [0106] 제3 바디충(210a)은 제3 전면(F3) 및 제3 전면(F3)과 반대되는 제3 후면(B3)을 가질 수 있다. 제3 바디충(210a)의 제3 전면(F3)은 집적 회로층이 형성되는 활성면일 수 있다. 제3 바디층(210a)의 제3 후면(B3)은 소자 구성 요소들이 형성되지 않는 비활성면일 수 있다. 패시베이션충(224a)은 제3 바디층(210a) 하부로 형성될 수 있다. 제4 연결 부재(240a)는 도 3에서 설명한 바와 같이 범프 패드(242a) 및 범프(244a)를 포함할 수 있다.

- [0107] 제2 칩들(200) 각각의 상부에 제3 칩(200-1)을 적충한다. 즉, 제2 칩(200)의 제2 후면(B2) 상에 제3 칩(200-1)의 제3 전면(F3)을 대향하여 적충한다. 제4 연결 부재(240a)는 제2 후면(B2) 및 제3 전면(F3) 사이에서 상기 제3 연결 부재(274)와 전기적으로 연결된다. 적충은 제3 칩(200-1)의 제4 연결 부재(240a)를 제2 칩(200)의 제3 연결 부재(274) 상에 열 압착 방법을 통해 접착함으로써 이루어질 수 있다. 제3 전면(F3)에 형성된 제4 연결 부재(240a)는 제2 칩(200)의 제3 연결 부재(274)에 연결될 수 있다.

- [0108] 제3 칩(200-1)의 제4 연결 부재(240a)의 배치를 평면적으로 제2 칩(200)의 제2 연결 부재(240)와 동일하게 할 경우 제3 칩(200-1)을 제2 칩(200)상에 적충할 수 있다. 따라서, 제3 칩(200-1)은 제2 칩(200)과 이종의 칩일수 있다. 또한, 제3 칩(200-1)은 제2 칩(200)과 동종의 칩일수도 있다.

- [0109] 제3 칩(200-1)의 크기는 제2 칩(200)과 마찬가지로 CS2로 표시되어 있다. 제3 칩(200-1)의 크기(CS2)는 폭 또는 길이일 수 있다. 제3 칩(200-1)의 크기(CS2)는 제1 칩(100)의 크기(CS1)보다 작거나 같을 수 있다.

- [0110] S2는 제3 칩용 웨이퍼(미도시)의 스크라이브 라인 영역 내에서 블레이드(blade)에 의해 절단되는 크기로써 폭 또는 길이일 수 있고, S1보다는 크게 형성한다. S2는 블레이드의 폭일 수 있다. 제3 칩(200-1)의 크기(CS2)를 제1 칩(100)의 크기(CS1)보다 작거나 같게 하고, 블레이드에 의해 절단되는 크기(S2)를 S1보다 크게 하기 때문 에 후의 언더필 공정 및 절단 공정을 용이하게 수행할 수 있다.

- [0111] 도 19를 참조하면, 제2 칩(200)과 제3 칩(200-1)의 연결 부분을 채우는 언더필(310a)을 형성한다. 제2 칩(200) 상에 적충되는 제3 칩(200-1)의 크기를 작게 하여 고집적화된 웨이퍼에서 스크라이브 라인 영역의 크기, 예컨대

폭이 좁더라도 언더필 공정을 용이하게 수행할 수 있다. 언더필(310a)은 제2 칩(200) 및 제3 칩(200-1)의 연결 부분, 즉 제2 칩(200)의 제3 연결 부재(274)와 제3 칩(200-1)의 제4 연결 부재(240a)가 연결되는 부분을 채울수 있다.

- [0112] 언더필(310a)은 앞서 도 5에서 설명한 언더필(310)과 동일한 재질로 형성할 수 있다. 언더필(310a)은 후에 형성되는 몰당재와 다른 재질로 형성될 수 있지만 동일 재료로 형성될 수도 있다. 도시된 바와 같이, 언더필(310a)은 제2 칩(200) 및 제3 칩(200-1)의 연결 부분뿐만 아니라, 상기 연결 부분에서 확장하여 제3 칩(200-1)의 측면 및 제2 칩(200)의 후면 일부분을 밀봉시킬 수 있다. 즉, 언더필(310a)은 제2 칩(200)과 제3 칩(200-1)의 연결부분만을 채울 수도 있지만, 도시된 바와 같이 제2 칩(200)과 제3 칩(200-1)의 연결부분을 채우면서 제3 칩(200-1)의 측면을 감싸도록 형성될 수도 있다. 이와 같이 언더필(310a)이 제3 칩(200-1)의 측면을 감싸게 되면, 반도체 패키지 완성 후에, 언더필(310a)이 측면으로 노출될 수도 있다. MUF(molded underfill)공정을 이용하는 경우에는 본 단계의 언더필 공정은 생략될 수도 있다.

- [0113] 이어서, 제3 칩(200-1)을 몰딩하는 몰딩재(320a)를 형성한다. 몰딩재(320a)는 레진과 같은 폴리머로 형성될 수 있다. 예컨대, 몰딩재(320a)는 EMC(Epoxy Molding Compound)로 형성될 수 있다. 이에 따라, 제3 칩(200-1)은 언더필(310a)과 몰딩재(320a)를 구비하여 제2 밀봉재(330a)로 밀봉된다. 제2 밀봉재(330a)는 제3 칩(200-1)의 측면들 및 후면을 밀봉할 수 있다. 언더필(310a)의 존재로 인해 몰딩재(320a)는 언더필(310)의 측면을 밀봉할수 있다.

- [0114] 도 20을 참조하면, 제2 밀봉재(330a) 상면을 그라인딩하여, 제3 칩(200-1)의 상면(후면)을 노출시킬 수 있다. 제2 밀봉재(330a)의 상면은 제3 칩(200-1)의 상면(후면)과 동일 수평면을 구성할 수 있다. 제3 칩(200-1) 상면은, 집적 회로층이 형성되지 않는 반도체 기판(즉 실리콘 기판)의 후면일 수 있고, 그에 따라, 실리콘 기판의 후면이 외부로 노출될 수 있다.

- [0115] 도 21을 참조하면, 앞서 도 8 내지 도 10에서 설명한 바와 동일한 방법으로 제3 칩(200-1)의 제3 바디층(210a) 내에 제2 관통 실리콘 비아(230-1)를 형성한다. 제2 관통 실리콘 비아(230-1)는 제4 연결 부재(240a)와 전기적으로 연결될 수 있다.

- [0116] 이어서, 앞서 도 10 및 도 11에서 설명한 바와 동일한 방법으로 제3 칩(200--1)의 후면, 즉 제3 바디층(210a)의 후면 상에 보호층(260)과 제5 연결 부재(274a)를 형성한다. 제5 연결 부재(274a)는 범프 패드(270) 및 범프 (272)로 구성될 수 있다. 제5 연결 부재(274a)는 제3 연결 부재(274)와 동일한 물질로 형성될 수 있다.

- [0117] 그리고, 제1 칩(100)의 후면(B1')을 연마하여 제1 칩(100)의 두께를 줄인다. 이에 따라, 제1 칩(100)의 최종 두 께는 T1'이 될 수 있다. 제1 칩(100)의 최종 두께(T1')를 제2 칩(200) 및 제3 칩(200-1)의 두께(T2)보다 두껍 게 조절할 수 있다.

- [0118] 도 22 및 도 23을 참조하면, 기저 웨이퍼(10) 및 밀봉재(330, 330a)를 소잉(sawing, 절단)하여 각각의 칩 적층 반도체 패키지(1000-2)로 분리한다. 도 22에서는 제1 칩(100)의 크기(CS1)을 기준으로 기저 웨이퍼(10) 및 밀봉 재(330, 330a)를 절단한다. S2보다 작은 S1의 블레이드 폭을 기준으로 기저 웨이퍼(10)와 제2 칩들(200), 제3 칩들(200-1) 사이의 밀봉재(330, 330a)를 절단하기 때문에 매우 용이하게 절단 공정을 수행할 수 있다. 이렇게 될 경우, 밀봉재(330, 330a), 즉 언더필(310, 310a)을 포함하는 제2 칩(200) 및 제3 칩(200-1)의 크기는 CS2에서 CS2'로 약간 크게 될 수 있다. 도 23은 편의상 제1 칩(100)을 위에 위치시켜 도시한다.

- [0119] 앞서와 같이 절단 공정을 통하여 개개의 칩 적층 반도체 패키지(1000-2)를 형성하고 나면, 제1 칩(100)의 양측면 및 후면이 노출된다. 이렇게 할 경우, 칩 적층 반도체 패키지(1000-2)를 보드 기판 상에 실장하여 재차 몰딩할 경우 추가 밀봉재가 제1 칩(100)의 측면과 잘 결합 및 부착될 수 있다.

- [0120] 본 실시예의 칩 적충 반도체 패키지 제조 방법에 따르면, 제1 칩(100)을 복수개 포함하는 기저 웨이퍼(10) 상에, 제2 칩(200) 및 제3 칩(200-1)을 탑재한다. 이 과정에서, 제2 칩(200) 및 제3 칩(200-1)의 크기(CS2)는 제2 칩(200) 및 제3 칩(200-1)을 포함하는 웨이퍼를 절단하여 제2 칩(200) 및 제3 칩(200-1)을 준비할 때, 블레이드폭(S2)을 크게 함으로써 제1 칩(100)보다 작게 준비한다.

- [0121] 이에 따라, 고집적화된 웨이퍼에서 스크라이브 라인 영역의 크기, 예컨대 스크라이브 라인 영역의 폭이 좁더라도 언더필 공정을 용이하게 수행할 수 있다. 또한, 기저 웨이퍼(10) 및 밀봉재(330, 300a)를 절단할 때 보다 용이하게 수행하여 칩 적층 반도체 패키지(1000-2)를 제조할 수 있다.

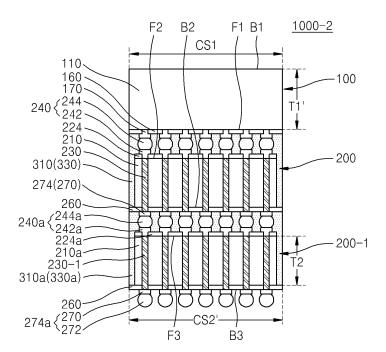

- [0122] 여기서, 도 23을 참조하여 앞서 칩 적층 반도체 패키지의 제조 방법에 의해 제조된 칩 적층 반도체 패키지의 구

조 및 특징에 대하여 간단히 설명한다.

- [0123] 구체적으로, 도 23의 칩 적층 반도체 패키지(1000-2)는 앞서 설명한 바와 같이 제1 칩(100)을 위에 위치시켜 도 시하며, 제1 칩(100), 제2 칩(200), 제3 칩(200-1) 및 밀봉재(330, 330a)를 포함할 수 있다.

- [0124] 제1 칩(100)은 제1 바디층(110), 패시베이션층(160) 및 제1 연결 부재(170)를 포함할 수 있다. 제1 칩(100)은 제1 전면(F1) 및 이에 반대되는 제1 후면(B1)을 가질 수 있다. 제1 연결 부재(170)는 제1 전면(F1)에 제2 칩(200)의 제2 연결 부재(240)에 대해 미러(mirror) 대칭 형태로 형성될 수 있다.

- [0125] 제1 칩(100)의 아래에 제2 칩(200)이 위치할 수 있다. 제2 칩(200)은 제2 바디층(210), 패시베이션층(224), 제 1 관통 실리콘 비아(230) 및 제2 연결 부재(240)를 포함할 수 있다. 제2 칩(200)은 제2 전면(F2) 및 이에 반대되는 제2 후면(B2)을 가진다. 제2 연결 부재(240)는 상기 제1 전면(F1) 및 제2 전면(F2) 사이에서 상기 제1 연결 부재(170) 및 제1 관통 실리콘 비아(230)와 전기적으로 연결된다.

- [0126] 제2 칩(200)의 하부에는 보호층(260) 및 제3 연결 부재(274)가 형성될 수 있다. 제3 연결 부재(274)는 범프 패드(270)로 구성될 수 있다. 밀봉재(330)는 제1 칩(100) 및 제2 칩(200)의 연결 부분, 즉 제1 칩(100)의 제1 연결 부재(170)와 제2 연결 부재(240)가 연결되는 부분에 채워져 있다.

- [0127] 밀봉재(330)는 제2 칩(200)의 양측면을 둘러싸도록 형성될 수 있다. 따라서, 제2 칩(200)의 양측면에 형성된 밀봉재(330)는 제1 칩(100) 및 제2 칩(200)의 연결 부분에 형성된 밀봉재(330)와 동일한 소재로 이루어질 수도 있다.

- [0128] 제2 칩(200)의 아래에 제3 칩(200-1)이 위치할 수 있다. 제3 칩(200-1)은 제3 바디층(210a), 패시베이션층 (224a), 제2 관통 실리콘 비아(230-1) 및 제4 연결 부재(240a)를 포함할 수 있다. 제3 칩(200-1)은 제3 전면 (F3) 및 이에 반대되는 제3 후면(B3)을 가진다. 제4 연결 부재(240a)은 상기 제2 후면(B2) 및 제3 전면(F3) 사이에서 상기 제3 연결 부재(274) 및 제2 관통 실리콘 비아(230-1)와 전기적으로 연결된다.

- [0129] 제3 칩(200-1)의 하부에는 보호충(260) 및 제5 연결 부재(274a)가 형성될 수 있다. 제5 연결 부재(274a)는 범프 패드(270) 및 범프(272)로 구성될 수 있다. 밀봉재(330a)는 제2 칩(200) 및 제3 칩(200-1)의 연결 부분, 즉 제 2 칩(200)의 제3 연결 부재(274)와 제4 연결 부재(240a)가 연결되는 부분에 채워져 있다. 밀봉재(330a)는 제3 칩(200-1)의 양측면을 둘러싸도록 형성될 수 있다. 따라서, 제3 칩(200-1)의 양측면에 형성된 밀봉재(330a)는 제2 칩(200) 및 제3 칩(200-1)의 연결 부분에 형성된 밀봉재(330a)와 동일한 소재로 이루어질 수도 있다.

- [0130] 제1 칩(100)의 후면은 밀봉재(330)가 형성되지 않고 노출되어 있다. 제1 칩(100)의 양측면도 밀봉재가 형성되어 있지 않아 노출되어 있다. 이에 따라, 칩 적층 반도체 패키지(1000-2)를 후술하는 바와 같이 메인 칩이나 보드 기판 상에 실장하여 재차 몰딩할 경우 추가 몰딩재가 제1 칩(100)의 상면이나 제1 칩(100)의 측면과 잘 결합 및 부착될 수 있다.

- [0131] 제2 칩(200) 및 제3 칩(200-1)의 양측면을 둘러싸도록 형성된 밀봉재(330, 330a)의 양단부가 제1 칩(100)의 모 서리와 수직적으로 일치되는 구조를 갖는다. 다시 말해, 밀봉재(330, 330a)를 포함하는 제2 칩(200) 및 제3 칩 (200-1)의 크기(CS2')는 제1 칩(100)의 크기(CS1)와 동일하게 할 수 있다.

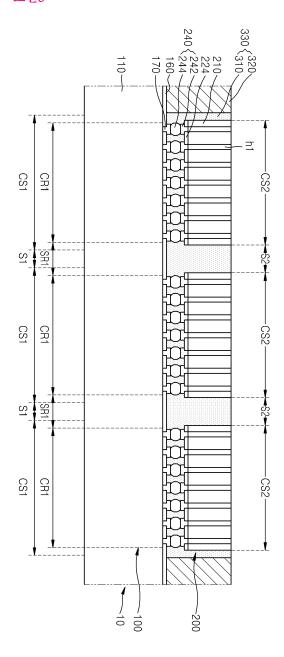

- [0132] 도 24 및 도 25는 본 발명의 기술적 사상의 일 실시예에 따른 칩 적층 반도체 패키지 제조 방법 및 이에 의해 제조된 칩 적층 반도체 패키지를 설명하기 단면도들이다.

- [0133] 구체적으로, 도 24 및 도 25의 실시예는 도 18 내지 도 23의 실시예와 비교할 때, 기저 웨이퍼(10) 및 밀봉재 (330, 330a)의 절단 공정을 제외하고는 동일하다.

- [0134] 먼저, 도 18 내지 도 21에 도시한 제조 공정을 수행한다. 이렇게 되면, 제1 칩(100)들을 포함하는 기저 웨이퍼 (10) 상에 밀봉재(330, 330a)로 밀봉된 제2 칩(200) 및 제3 칩(200-1)이 위치한다.

- [0135] 도 24를 참조하면, 제2 칩(200) 및 제3 칩(200-1)의 폭(CS2)을 기준으로 기저 웨이퍼(10) 및 밀봉재(330, 330a)를 절단한다. 앞서 설명한 바와 같이 S2는 블레이드 폭일 수 있고, S2의 블레이드 폭을 기준으로 기저 웨이퍼(10)을 용이하게 절단할 수 있다. 이렇게 될 경우, 제1 칩(100)의 크기는 CS1에서 CS1'으로 약간 작게되다

- [0136] 도 25를 참조하면, 절단 공정을 통하여 개개의 칩 적충 반도체 패키지(1000-3)를 형성하고 나면, 제1 칩(100), 제2 칩(200) 및 제3 칩(200-1)의 양측면이 노출된다. 도 24 및 도 25에 도시한 실시예의 칩 적충 반도체 패키지 제조 방법에 따르면, 도 18 내지 도 23과 마찬가지로 제2 칩(200)을 포함하는 웨이퍼를 절단하여 제2 칩(200)을

준비할 때, 제2 칩(200) 및 제3 칩(200-1)의 크기는, 블레이드폭(S2)을 크게 함으로써 제1 칩(100)보다 작게 준비한다. 이에 따라, 기저 웨이퍼(10) 및 밀봉재(330, 330a)를 절단할 때 보다 용이하게 수행하여 칩 적충 반도 제 패키지(1000-3)를 제조할 수 있다.

- [0137] 도 24 및 도 25에 도시한 실시예의 칩 적층 반도체 패키지 제조 방법에 따르면, 제1 칩(100)의 상면 및 양측면을 노출시킨다. 더하여, 제2 칩(200) 및 제3 칩(200-1)의 양측면도 노출시킨다. 이렇게 할 경우, 칩 적층 반도체 패키지(1000-3)를 보드 기판 상에 실장하여 재차 몰딩할 경우 추가 밀봉재가 제1 칩(100), 제2 칩(200), 제3 칩(200-1)의 측면과 잘 결합 및 부착될 수 있다.

- [0138] 여기서, 도 25를 참조하여 앞서 칩 적충 반도체 패키지의 제조 방법에 의해 제조된 칩 적충 반도체 패키지의 구조 및 특징에 대하여 간단히 설명한다.

- [0139] 구체적으로, 도 25의 칩 적충 반도체 패키지(1000-3)는 제2 칩(200) 및 제3 칩(200-1)의 양측면이 노출된 것을 제외하고는 도 23의 칩 적충 반도체 패키지(1000-2)와 동일하다.

- [0140] 밀봉재(330, 330a)는 제2 칩(200) 및 제3 칩(200-1)의 양측면에는 형성되어 있지 않다. 물론, 제1 칩(100)의 양측면도 밀봉재(330)가 형성되어 있지 않아 노출되어 있다.

- [0141] 이에 따라, 칩 적층 반도체 패키지(1000-3)를 보드 기판 상에 실장하여 재차 몰딩할 경우 추가 몰딩재가 제1 칩 (100)의 후면 및 양측면이나 제2 칩(200) 및 제3 칩(200-1)의 측면과 잘 결합 및 부착될 수 있다. 제2 칩(200) 및 제3 칩(200-1)의 양단부가 제1 칩(100)의 모서리와 수직적으로 일치되는 구조를 갖는다. 다시 말해, 제2 칩(200) 및 제3 칩(200-1)의 크기(CS2)는 제1 칩(100)의 크기(CS1)와 동일한 크기를 갖는다.

- [0142] 도 26은 본 발명의 기술적 사상의 일 실시예에 따른 칩 적층 반도체 패키지 제조 방법 및 이에 의해 제조된 칩 적층 반도체 패키지를 설명하기 위한 단면도이다.

- [0143] 구체적으로, 도 26의 실시예는 도 5의 실시예와 비교할 때, 언더필(310) 부분을 접착 부재(312)로 형성한 것을 제외하고는 동일하다. 도 26의 공정 후에는 도 6 내지 도 13의 제조 공정을 진행할 수 있다.

- [0144] 도 26의 실시예에서, 제1 연결 부재(170)가 형성된 기저 웨이퍼(10)의 전면에 접착 부재(312)를 형성한 후, 제2 칩(200)을 제1 칩(100) 상에 적층한다. 즉, 제2 칩(200)의 적층은, 접착 부재(312)로 인해 제2 칩(200)의 제2 연결 부재(240)를 제1 칩(100)의 제1 연결 부재(170)에 단순 압착하여 이루어질 수 있다.

- [0145] 이에 따라, 제1 칩(100)과 제2 칩(200)의 연결 부분은 접착 부재(312)로 채워진다. 접착 부재(312)는 제1 칩 (100)과 제2 칩(200) 사이에 채워지며, 도 5와 같이 제2 칩(200)의 측벽을 감싸게 형성하지 않는다. 접착 부재 (312)는 예컨대, NCF(Non-Conductive Film), ACF(Anisotropic Conductive Film), UV 필름, 순간 접착제, 열경 화성 접착제, 레이저 경화형 접착제, 초음파 경화형 접착제, NCP(Non-Conductive Paste) 등으로 형성될 수 있다.

- [0146] NCF는 보통의 접착 필름으로서, 절연성을 갖는 필름이다. 이러한 NCF를 이용하면, 압착하는 방식으로 제2 칩 (200)을 제1 칩(100) 상에 적층할 수 있다. 그에 따라, 열 및 압착을 통해 제2 칩(200)을 제1 칩(100) 상에 적층할 때 발생할 수 있는 칩의 뒤틀림과 같은 워피지(warpage) 현상, 즉 휨 현상을 해결할 수 있어 다수의 칩들을 적층하는데 유리할 수 있다.

- [0147] 한편, ACF는 이방성 전도 필름으로, 절연 접착 필름 내에 도전성 입자가 분산되어 있는 구조를 가지며, 접속시, 연결 부재들(170, 240)이 형성된 수직 방향으로만 통전이 되도록 하며, 연결 부재들(170, 240) 사이 방향, 즉 수평 방향으로는 절연되는 이방성의 전기적 특성을 가질 수 있다. 이러한, ACF는 열과 압력을 가하여 접착제를 용융시키면, 도전입자는 대치하는 전극 사이에 배열되어 도전성이 발생하는 반면, 인접하는 전극 사이에는 접착제가 충진되어 절연되게 된다.

- [0148] 접착 부재(312)는 전술한 재질에 한정되지 않고, 칩들(100, 200)을 견고하게 접착할 수 있고, 연결 부분의 범프 와 패드들을 밀봉할 수 있는 다양한 다른 재질의 접착물질로 형성될 수 있음은 물론이다.

- [0149] 본 실시예에서는 다층 칩들을 적충하기 위하여 접착 부재(312)로서, NCF를 사용할 수 있다. 본 실시예에서, 접 착 부재(312)가 제1 칩(100) 및 제2 칩(200)의 연결 부분에만 형성됨으로써, 후공정에서 밀봉재(330)는 제2 칩(200)의 측면들에 직접 접촉하면서 제2 칩(200)의 측면들을 밀봉할 수 있다.

- [0150] 도 27은 본 발명의 기술적 사상의 일 실시예에 따른 칩 적층 반도체 패키지 제조 방법 및 이에 의해 제조된 칩 적층 반도체 패키지를 설명하기 위한 단면도이다.

- [0151] 구체적으로, 도 27의 실시예는 도 5의 실시예와 비교할 때, 언더필(310b)이 제1 칩(100) 및 제2 칩(200) 사이에 형성한 것을 제외하고는 동일하다. 도 27의 공정 후에는 도 6 내지 도 13의 제조 공정을 진행할 수 있다.

- [0152] 도 27의 실시예에서, 도 3에 도시한 바와 같이 제1 칩(100)의 제1 연결 부재(170) 상에 제2 칩(200)을 적충한다. 적충은 제2 칩(200)의 제2 연결 부재(240)를 제1 칩(100)의 제1 연결 부재(170) 상에 열 압착 방법을 통해 접착한다.

- [0153] 이어서, 제1 칩(100) 및 제2 칩(200)의 연결 부분에 언더필(310b)을 형성한다. 즉, 언더필(310b)은 제2 칩(200)의 측면이나 제2 칩(200)의 후면 일부분을 밀봉키시키지 않고, 제1 칩(100)과 제2 칩(200)의 연결 부분만을 채운다. 언더필(310b)은 앞서 설명한 바와 같이 에폭시 수지와 같은 언더필 수지로 형성될 수 있고, 실리카 필러(filler)나 플럭스(flux) 등이 포함될 수 있다. 언더필(310b)은 후에 형성되는 몰당재와 다른 재질로 형성될 수 있지만 동일 재료로 형성될 수도 있다.

- [0154] 본 실시예에서, 언더필(310b)은 제1 칩(100) 및 제2 칩(200)의 연결 부분에만 형성됨으로써, 후공정에서 밀봉재 (330)는 제2 칩(200)의 측면들에 직접 접촉하면서 제2 칩(200)의 측면들을 밀봉할 수 있다.

- [0155] 도 28은 본 발명의 기술적 사상의 일 실시예에 따른 칩 적충 반도체 패키지 제조 방법 및 이에 의해 제조된 칩 적충 반도체 패키지를 설명하기 위한 단면도이다.

- [0156] 구체적으로, 도 28의 실시예는 도 5 및 도 6의 실시예와 비교할 때, 언더필(310)을 형성하지 않고 몰딩재(320 a)로 밀봉재(330)를 형성한 것을 제외하고는 동일하다. 도 26의 공정 후에는 도 7 내지 도 13의 제조 공정을 진행할 수 있다.

- [0157] 도 28의 실시예에서, 도 3에 도시한 바와 같이 제1 칩(100)의 제1 연결 부재(170) 상에 제2 칩(200)을 적충한다. 적충은 제2 칩(200)의 제2 연결 부재(240)를 제1 칩(100)의 제1 연결 부재(170) 상에 열 압착 방법을 통해 접착할 수 있다.

- [0158] 이어서, 제1 칩(100)과 제2 칩(200)의 연결 부분을 채우면서 제2 칩(200)의 양측면 및 상부를 밀봉하는 몰딩재 (320a)를 형성하여 밀봉재(330)를 형성한다. 몰딩재(320a)는 제1 칩(100) 및 제2 칩(200)의 연결 부분, 즉 제1 칩(100)의 제1 연결 부재(170)와 제2 연결 부재(240)가 연결되는 부분을 채울 수 있다.

- [0159] 몰딩재(320a)는 앞서 설명한 바와 같이 레진과 같은 폴리머로 형성될 수 있다. 예컨대, 몰딩재(320a)는 EMC(Epoxy Molding Compound)로 형성될 수 있다. 몰딩재(320a)는 제2 칩(200)의 측면들 및 상면들을 밀봉할 수 있다.

- [0160] 도 29 내지 도 32는 본 발명의 기술적 사상의 일 실시예에 따른 칩 적층 반도체 패키지 제조 방법 및 이에 의해 제조된 칩 적층 반도체 패키지를 설명하기 위한 단면도들이다.

- [0161] 구체적으로, 도 29 내지 도 32의 실시예는 도 1 내지 도 13의 실시예와 비교할 때 제2 칩(200a)에 제1 관통 실리콘 비아(230)가 형성된 것을 제외하고는 동일하다.

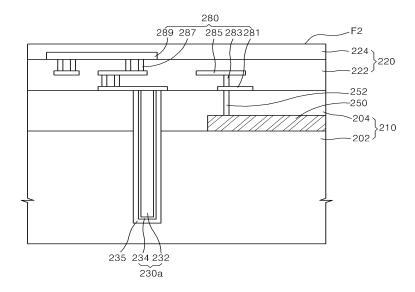

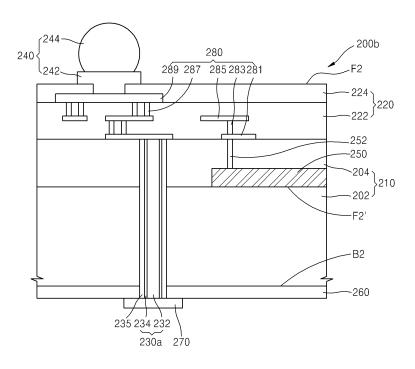

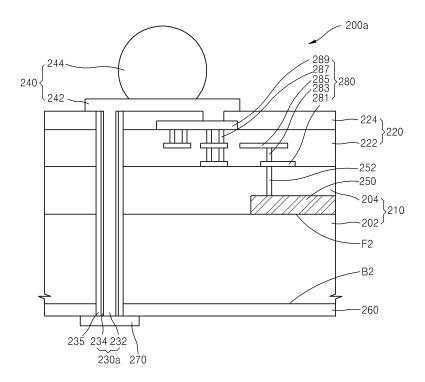

- [0162] 도 29를 참조하면, 제1 관통 실리콘 비아(230)가 형성된 다수의 제2 칩들(200a)을 준비한다. 즉, 제2 칩(200a)은 제1 관통 실리콘 비아(230), 제2 바디충(210), 금속간 절연충(222) 및 패시베이션충(224)을 포함하는 절연충(220) 및 제2 연결 부재(240)를 포함할 수 있다.

- [0163] 제1 관통 실리콘 비아(230)는 제2 연결 부재(240)와 전기적으로 연결될 수 있다. 제1 관통 실리콘 비아(230)는 제2 바디충(210)의 전면(F2)에서 후면(B2)까지 형성되지 않을 수 있다. 이에 따라, 제1 관통 실리콘 비아(230)은 제2 바디충(210) 내에 형성될 수 있다. 제2 칩(200a)의 크기는 CS2로 표시할 수 있다. 제2 칩(200a)의 크기 (CS2)는 폭 또는 길이일 수 있다. 제2 칩(200a)의 구체적인 제조 과정은 후에 자세하게 설명한다.

- [0164] 이어서, 도 3에서 설명한 바와 같이 제1 칩들(100) 각각의 상부에 제1 관통 실리콘 비아(230)를 포함하는 제2 칩(200)을 적충한다. 즉, 제1 칩(100)의 제1 전면(F1) 상에 제2 칩(200a)의 제2 전면(F2)을 대향하여 적충한다. 제2 연결 부재(240) 는 제1 전면(F1) 및 제2 전면(F2) 상에서 상기 제1 연결 부재(170)와 전기적으로 연결된다. 적충은 제2 칩(200)의 제2 연결 부재(240)를 제1 칩(100)의 제1 연결 부재(170) 상에 열 압착 방법을 통해 접착함으로써 이루어질 수 있다.

- [0165] 도 30을 참조하면, 도 5 내지 도 7에 도시한 바와 같이 제2 칩(200a)을 밀봉하는 밀봉재(330)를 형성한다. 밀봉 재(330)는 언더필(310) 및 몰딩재(330)로 이루어질 수 있다. 언더필(310)은 제1 칩(100)과 제2 칩(200a)의 연 결 부분을 채우면서 제2 칩(200a)의 양측면을 밀봉할 수 있다. 몰딩재(330)는 언더필(310)의 외측에 형성되어

제2 칩(200a)의 측면들 및 후면을 밀봉할 수 있다.

- [0166] 도 31 및 32를 참조하면, 도 9 및 도 10에서 설명한 바와 같이 제2 칩(200a)의 후면, 즉 제2 바디층(210)의 후면 상에 노출된 제1 관통 실리콘 비아(230) 및 제3 연결 부재(도 11의 274)를 구성하는 범프 패드(270)를 형성하다.

- [0167] 여기서, 도 32a 내지 도 32c를 참조하여 제1 관통 실리콘 비아(230) 및 제3 연결 부재(270)의 형성 과정을 자세히 설명한다. 제1 관통 실리콘 비아(230) 및 제3 연결 부재(270)의 형성 과정은 10a 내지 10d와 비슷한 방법일수 있다. 제1 관통 실리콘 비아(230) 및 제3 연결 부재(270)의 형성 과정은 다양한 방법이 있을 수 있을 수 있다.

- [0168] 도 32a에 도시한 바와 같이, 제2 바디층(210) 내에 스페이서 절연층(235a)에 의해 절연되고. 후면에 노출되지 않은 제1 관통 실리콘 비아(230')가 형성되어 있다. 이어서, 도 32b에 도시한 바와 같이 제2 바디층(210)의 후 면을 식각하여 리세스시킨다. 이렇게 되면, 제1 관통 실리콘 비아(230)는 후면이 노출되고 스페이서 절연층(235a)은 패턴된 스페이서 절연층(235)이 될 수 있다.

- [0169] 도 32c에 도시한 바와 같이, 리세스된 제2 바디충(210)의 후면 상부 및 제1 관통 실리콘 비아(230)의 양측벽 상에 보호충(260)을 형성한다. 보호충(260)은 제2 바디충(210)을 보호하는 역할을 수행한다. 보호충(260)은 제1 관통 실리콘 비아들(230) 사이를 절연하는 역할을 수행한다.

- [0170] 일 실시예에서, 앞서 설명한 바와 같이 제1 바디층(210)의 후면 리세스시 제1 관통 실리콘 비아(230) 상에 형성된 스페이서 절연층(235)은 남길 수 있다. 그리고, 제2 바디층(210) 상에 절연 물질층을 충분한 두께로 형성한후 식각하여 보호층(260)을 형성할 때 제1 관통 실리콘 비아(230)를 노출시킬 수도 있다.

- [0171] 제1 관통 실리콘 비아(230) 상에 제3 연결 부재(도 11의 274)를 구성하는 범프 패드(270)를 형성한다. 계속하여, 도 11 내지 도 13의 제조 공정을 수행함으로써 후의 도 39에 설명하는 칩 적층 반도체 패키지를 완성할 수 있다.

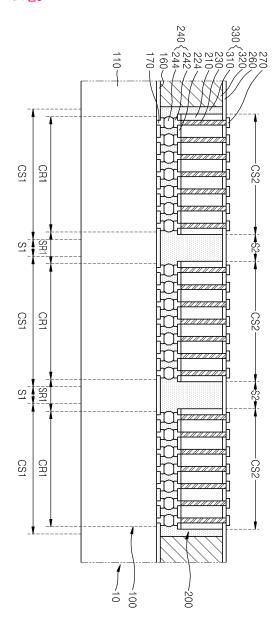

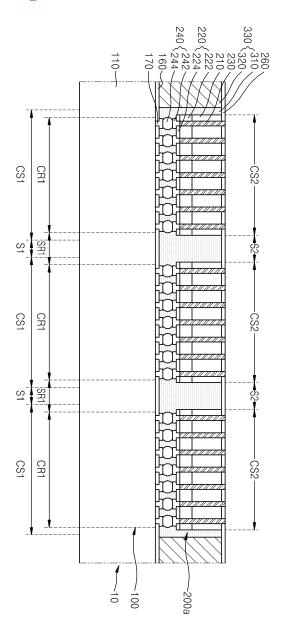

- [0172] 도 33 및 도 34는 본 발명의 기술적 사상의 일 실시예에 따른 칩 적충 반도체 패키지 제조 방법 및 그에 의해 제조된 칩 적충 반도체 패키지를 설명하기 위한 단면도들이다.

- [0173] 구체적으로, 도 33 내지 도 34의 실시예는 도 1 내지 도 13의 실시예 및 도 29 내지 32와 비교할 때 제2 칩 (200a)에 금속간 절연층(222) 및 제1 관통 실리콘 비아(230a)가 형성된 것을 제외하고는 동일하다. 도 33 내지 도 34의 실시예는 도 29 내지 도 32의 실시예외 비교할 때 제1 관통 실리콘 비아(230a)가 제2 바디층(210)의 후 면(B2)에서 전면(F2)까지 형성되지 않은 것을 제외하고는 동일하다.

- [0174] 도 33을 참조하면, 제1 관통 실리콘 비아(230a)가 형성된 다수의 제2 칩들(200b)을 준비한다. 제2 칩(200b)은 제1 관통 실리콘 비아(230a), 제2 바디층(210), 금속간 절연층(222) 및 패시베이션층(224)을 포함하는 절연층 (220), 및 제2 연결 부재(240)를 포함할 수 있다.

- [0175] 제1 관통 실리콘 비아(230a)는 금속간 절연층(222) 내의 배선들을 통하여 제2 연결 부재(240)와 전기적으로 연결될 수 있다. 제1 관통 실리콘 비아(230a)는 제2 바디층(210)의 후면(B2)에서 전면(F2)까지 형성되지 않을 수 있다. 제1 관통 실리콘 비아(230a)는 제2 바디층(210)의 후면(B2)에서 금속간 절연층(222)까지 형성될 수 있다. 제2 칩(200a)의 크기는 CS2로 표시할 수 있다. 제2 칩(200a)의 크기(CS2)는 폭 또는 길이일 수 있다. 제2 칩(200b)의 구체적인 제조 과정은 후에 보다더 자세하게 설명한다.

- [0176] 이어서, 도 3에서 설명한 바와 동일하게 제1 칩들(100) 각각의 상부에 제1 관통 실리콘 비아(230a)를 포함하는 제2 칩(200b)을 적충한다. 즉, 제1 칩(100)의 제1 전면(F1) 상에 제2 칩(200b)의 제2 전면(F2)을 대향하여 적충한다. 제2 연결 부재(240)는 제1 전면(F1) 및 제2 전면(F2) 상에서 상기 제1 연결 부재(170)와 전기적으로 연결된다. 적충은 제2 칩(200b)의 제2 연결 부재(240)를 제1 칩(100)의 제1 연결 부재(170) 상에 열 압착 방법을통해 접착함으로써 이루어질 수 있다.

- [0177] 도 34를 참조하면, 도 5 내지 도 7에 도시한 바와 동일하게 제2 칩(200b)을 밀봉하는 밀봉재(330)를 형성한다. 밀봉재(330)는 언더필(310) 및 몰딩재(320)로 이루어질 수 있다. 언더필(310)은 제1 칩(100)과 제2 칩(200a)의 연결 부분을 채우면서 제2 칩(200b)의 양측면을 밀봉할 수 있다. 몰딩재(320)는 언더필(310)의 외측에 형성되어 제2 칩(200b)의 측면들 및 후면을 밀봉할 수 있다.

- [0178] 도 9, 도 10, 32a 내지 도 32c에서 설명한 바와 같이 제2 칩(200b)의 후면, 즉 제2 바디층(210)의 후면 상에 보

호충(260) 및 제3 연결 부재(도 11의 274)를 구성하는 범프 패드(270)를 형성한다. 계속하여, 도 11 내지 도 13 의 제조 공정을 수행함으로써 후의 도 39에 설명하는 칩 적충 반도체 패키지를 완성할 수 있다.

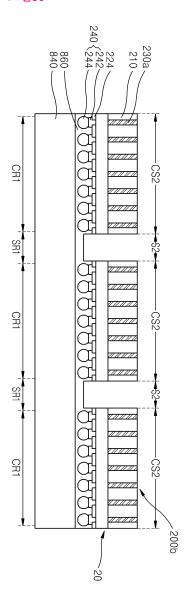

- [0179] 도 35 및 도 36은 본 발명의 기술적 사상의 일 실시예에 따른 칩 적충 반도체 패키지 제조 방법에 이용되는 제2 칩의 제조 방법을 설명하기 단면도들이다.

- [0180] 구체적으로, 도 35 및 도 36에 도시한 제2 칩(200b)은 도 33 및 도 34에 이용된 것을 설명하기 위한 것이다. 도 35 및 도 36에 도시한 제2 칩(200b)은 도 14 및 도 15와 비교할 때 금속간 절연층(222) 및 패시베이션층(224)을 포함하는 절연층(220)과 제1 관통 실리콘 비아(230a)가 더 형성된 것을 제외하고는 동일하다.

- [0181] 도 35를 참조하면, 제1 관통 실리콘 비아(230a), 제2 바디층(210), 금속간 절연층(222) 및 패시베이션층(224)을 갖는 절연층(220), 및 제2 연결 부재(240)를 포함하는 다수의 제2 칩들(200b)을 포함한 웨이퍼(20)를 준비한다. 웨이퍼(20)는 지지 기판(840) 상에 접착 부재(860)를 통해 접착되어 준비될 수 있다. 웨이퍼(20)의 구체적인 제조 공정은 도 37a 내지 도 37f후에 자세히 설명한다.

- [0182] 도 36을 참조하면, 웨이퍼(20)의 스크라이브 라인 영역을 따라 소잉(sawing, 절단)하여 각각의 제2 칩(200b)들로 분리한다. 웨이퍼(20)에서 절단에 의해 완성되는 제2 칩(200b)의 크기는 CS2로 표시할 수 있다. 제2 칩(200b)의 크기(CS2)는 폭 또는 길이일 수 있다. 스크라이브 라인 영역 내에서 블레이드(blade)에 의해 절단되는 크기는 S2로 도시되어 있다. 블레이드(blade)에 의해 절단되는 크기(S2)는 폭 또는 길이일 수 있다.

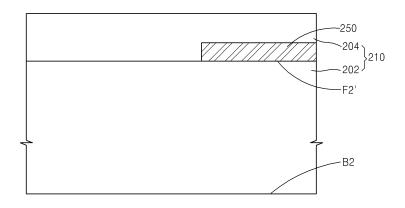

- [0183] 도 37a 내지 37f는 본 발명의 기술적 사상의 일 실시예에 따른 칩 적충 반도체 패키지 제조 방법에 이용되는 제 2 칩의 제조 방법을 설명하기 단면도들이다. 도 37a 내지 37f는 도 33 및 도 34의 실시예의 제2 칩(200b) 부분 만을 도시한 것이다.

- [0184] 도 37a를 참조하면, 먼저, 반도체 기판(202), 예컨대 실리콘 기판의 전면 (F2') 상에 집적 회로층(250)을 형성하고, 반도체 기판(202)의 전면(F2') 상에 집적 회로층(250)을 덮는 층간 절연층(204)을 형성한다. 반도체 기판(202)과 층간 절연층(204)이 제2 칩(200b)의 바디층(210)을 형성한다.

- [0185] 반도체 기판(202)은 단결정 웨이퍼, 예컨대 단결정 실리콘 웨이퍼로 형성될 수 있다. 집적 회로충(250)은 칩의 종류에 따라 다양한 회로 소자들, 예컨대, 트랜지스터들 및/또는 커패시터들을 포함할 수 있다.

- [0186] 충간 절연충(204)은 적절한 절연충 증착 방법, 예컨대 화학기상증착(CVD)을 이용하여 형성할 수 있다. 충간 절연충(204)은 집적 회로충(250)의 프로파일에 따라서 평탄하지 않게 형성될 수 있기 때문에, 증착 단계 후 평탄화될 수 있다. 평탄화는 화학적기계적연마(CMP) 또는 에치백(etch-back)을 이용하여 수행될 수 있다.

- [0187] 도 37b를 참조하면, 층간 절연층(204)과 반도체 기판(202)에 트랜치(h1)를 형성하여, 스페이서 절연층(235)과 제1 관통 실리콘 비아(230)를 형성한다. 좀더 구체적으로 설명하면, 층간 절연층(204) 상에 레지스트 패턴(미도시)을 형성하고, 레지스트 패턴을 이용하여 식각 공정을 통해 충간 절연층(204) 및 반도체 기판(202)을 연속적으로 제거하여 트랜치(h1)를 형성한다. 트랜치(h1) 형성은 레이저 드릴링을 이용할 수도 있다.

[0188]

[0189]

- 도시된 바와 같이, 반도체 기판(202)의 후면(B2)의 연마를 고려하여, 트랜치(h1)는 반도체 기판(202)을 관통하지 않도록 형성될 수 있다. 일 실시예에서, 트랜치(h1)는 반도체 기판(202)을 관통하여 형성할 수도 있다. 트랜치(h1)의 형상은 식각 조건 또는 드릴링 조건에 따라서 다양한 형상을 가질 수 있다. 예컨대, 비교적 균일한 원통 형상을 가질 수도 있고, 위에서 아래로 갈수록 그 폭이 점점 좁아지는 형상을 가질 수도 있다.

- 다음, 트랜치(h1) 내에 스페이서 절연층(235)을 형성한다. 예컨대, 스페이서 절연층(235)은 적절한 절연층, 예 컨대 산화층, 질화층, 폴리머 또는 파릴렌(parylene)을 포함할 수 있고, 저온 증착법 예컨대 저온 화학기상증착 (LTCVD), 폴리머 스프레잉(polymer spraying), 저온 물리기상증착(PVD) 방법을 이용하여 형성할 수 있다.

- [0190] 이어서, 스페이서 절연층(235) 상에 제1 관통 실리콘 비아(230a)를 형성한다. 예컨대, 제1 관통 실리콘 비아 (230a)는 트랜치(h1) 내의 스페이서 절연층(235) 상에 장벽 금속층(234)을 형성하고, 다시 장벽 금속층(234) 상에 배선 금속층(232)을 형성함으로써 구현할 수 있다. 장벽 금속층(234)은 Ti, Ta, TiN 및 TaN에서 선택된 하나 또는 둘 이상의 적층 구조를 포함할 수 있다. 배선 금속층(232)은 W, Al 및 Cu에서 선택된 하나 또는 둘 이상의 적층 구조를 포함할 수 있다. 장벽 금속층(234) 및 배선 금속층(232)은 화학기상 증착법(CVD), 플라즈마 강화 CVD(PECVD), 고밀도 플라즈마 CVD(HDP-CVD), 스퍼터링, 유기금속 화학기상 증착법(Metal Organic CVD: MOCVD), 또는 원자층 중착법(ALD)을 이용하여 형성할 수 있다. 한편, 배선 금속층(232)은 도금 방법을 이용하여 형성할 수 있고, 이 경우 씨드층(seed layer)을 먼저 형성한 후 도금층을 형성할 수 있다. 도금 방법으로 형성할 때,

Cu가 이용될 수 있다.

- [0191] 트랜치(h1) 매립 후, 평탄화될 수 있다. 예컨대, 화학적기계적연마(CMP) 또는 에치백(etch-back)을 이용하여 스페이서 절연층(235) 및 제1 관통 실리콘 비아(230a)가 트랜치(h1) 내부에만 남도록 평탄화될 수 있다. 한편, CMP에 의한 평탄화 후에 전열처리(preheat) 및 버퍼링 CMP 등이 수행될 수도 있다.

- [0192] 도 37c를 참조하면, 제1 관통 실리콘 비아(230a)와 연결된 다층 배선 패턴(280), 금속간 절연층(222), 및 패시 베이션층(224)을 포함하는 절연층(220)을 형성할 수 있다. 예컨대, 다층 배선 패턴(280)은 배선 라인들(281, 285, 289) 및 수직 플러그들(283, 287)의 적층 구조를 형성하는 단계를 반복하여 형성할 수 있다. 금속간 절연층(222)은 다층 배선 패턴(280)의 적층 구조에 따라 다층 구조로 형성될 수 있다. 다층 배선 패턴(280), 금속간 절연층(222), 및 패시베이션층(224)을 포함하는 절연층(220)이 형성될 경우, 제2 칩(200b)의 전면(F2)은 패시베이션층(224)의 표면일 수 있다.

- [0193] 다층 배선 패턴(280)은 물질막 증착 및 패터닝에 의해서 형성되거나 또는 다마신 공정에 의해서 형성될 수도 있다. 예컨대, 다층 배선 패턴(280)이 알루미늄(Al) 및/또는 텅스텐(W)을 포함하는 경우 전자의 방법으로 형성될수 있고, 구리(Cu)를 포함하는 경우 후자의 방법으로 형성될수 있다.

- [0194] 도 37d를 참조하면, 패시베이션층(224) 상에 다층 배선 패턴(280), 예컨대, 제3 배선 라인(289)에 연결되는 제2 연결 부재(240)를 형성할 수 있다. 제2 연결 부재(240)는 패시베이션층(224)에 트랜치를 형성하고, 트랜치를 채우도록 범프 패드(242)를 형성한 후, 범프 패드(242) 상으로 범프(244)를 형성함으로써 완성할 수 있다. 본 실시예에서의 제1 관통 실리콘 비아(230a)는 집적 회로층(250) 형성 후 다층 배선 패턴(280) 형성되기 전에 형성되는 비아-미들 구조로 형성될 수 있다.

- [0195] 도 37e를 참조하면, 반도체 기판(202)의 후면(B2)으로부터 반도체 기판(202)의 소정 두께를 제거하여, 스페이서 절연충(235) 및 제1 관통 실리콘 비아(230a)를 노출시킨다. 한편, 도시된 바와 같이 스페이서 절연충(235) 및 제1 관통 실리콘 비아(230)는 후면에서 돌출된 형태로 노출될 수 있다.

- [0196] 반도체 기판(202)의 제거는 그라인당, 화학적기계적연마(CMP), 등방성 식각 및 이방성 식각의 하나 또는 둘 이상을 결합하여 수행할 수 있다. 예를 들어, CMP를 이용하여 제거될 반도체 기판(202)의 상당 부분을 제거하고, 이어서 등방성 식각, 예컨대 습식 식각으로 반도체 기판(202)을 스페이서 절연충(235) 및 제1 관통 실리콘 비아(230a)의 바닥면 아래로 리세스시킬 수 있다.

- [0197] 도 37f를 참조하면, 반도체 기판(202)의 후면(B2) 및 돌출된 제1 관통 실리콘 비아(230a) 상에 보호층(260)을 형성한다. 일 실시예에서, 도 37e에서, 제1 관통 실리콘 비아(230a)의 표면을 노출시키지 않고 장벽 금속층 (234) 및 스페이서 절연층(235)을 남긴다. 그리고, 제1 관통 실리콘 비아층(230a) 및 반도체 기판(202) 상에 절연 물질층을 형성한 후 식각하여 보호층(260)을 형성할 때 제1 관통 실리콘 비아(230a)의 표면을 노출시킬 수 있다.

- [0198] 계속하여, 제1 관통 실리콘 비아(230a)에 연결되는 제3 연결 부재로 이용되는 범프 패드(270)를 형성한다. 앞서 설명한 바와 같이 제2 칩(200b)의 전면(F2)은 패시베이션층(224)의 표면일 수 있다. 범프 패드(270) 형성 후, 계속하여 도 11 내지 도 13의 제조 공정을 수행함으로써 칩 적층 반도체 패키지를 완성할 수 있다.

- [0199] 도 38은 본 발명의 기술적 사상의 일 실시예에 따른 칩 적충 반도체 패키지 제조 방법에 이용되는 제2 칩의 제조 방법을 설명하기 단면도이다. 도 38은 도 29 내지 도 32의 실시예의 제2 칩(200a) 부분만을 도시한 것이다.

- [0200] 구체적으로, 도 38의 실시예에 따른 제2 칩(200a)은 제1 관통 실리콘 비아(230) 부분만을 제외하고 도 37f의 제 2 칩(200b)과 유사한 구조를 가질 수 있다. 그에 따라, 설명의 편의를 위해 도 37a 내지 도 37f의 설명 부분에서 기술한 부분은 생략하거나 간략히 기술한다.

- [0201] 본 실시예의 제2 칩(200a)에서, 제1 관통 실리콘 비아(230)는 비아-라스트 구조로 형성될 수 있다. 그에 따라, 제1 관통 실리콘 비아(230)는 반도체 기판(202), 충간 절연충(204), 금속간 절연충(222), 및 패시베이션충(224)을 관통하여, 제2 연결 부재(240)의 범프 패드(242)에 바로 연결될 수 있다. 제1 관통 실리콘 비아(230)의 충상 구조나 측벽의 스페이서 절연충(235)은 도 37a 내지 도 37f에서 설명한 바와 같다.

- [0202] 도 39a 및 도 39b는 본 발명의 기술적 사상의 일 실시예에 의한 침 적층 반도체 패키지를 도시한 단면도들이다.

- [0203] 구체적으로, 도 39a는 도 29 내지 도 32의 실시예에 의해 제조된 칩 적층 반도체 패키지(1000-4)를 도시한 것이다. 도 39b는 도 33 및 34의 실시예에 의해 제조된 칩 적층 반도체 패키지(1000-5)를 도시한 것이다.

- [0204] 도 39a 및 도 39b의 칩 적충 반도체 패키지(1000-4, 100-5)는 도 13의 칩 적충 반도체 패키지(1000)와 비교할 때 아래에 설명하는 것을 제외하고는 동일하다. 그에 따라, 설명의 편의를 위해 도 13의 설명 부분에서 기술한 부분은 생략한다.

- [0205] 도 39a의 칩 적층 반도체 패키지(1000-4)는 도 13의 칩 적층 반도체 패키지(1000)과 비교할 때 제2 칩(200a)에 금속간 절연층(222)을 포함하는 절연층(220)이 형성된 것을 제외하고는 동일하다. 다시 말해, 도 39a의 칩 적층 반도체 패키지(1000-4)는 제2 칩(200a)의 전면(F2)측에 금속간 절연층(222) 및 패시베이션층(224)을 포함하는 절연층(220)이 형성될 수 있다. 그리고, 도 39a의 제2 칩(200a)의 제1 관통 실리콘 비아(230)는 금속간 절연층(222)을 관통하여 제2 연결 부재(240)와 연결될 수 있다.

- [0206] 도 39b의 칩 적충 반도체 패키지(1000-5)는 도 13의 칩 적충 반도체 패키지(1000)와 비교할 때 제2 칩(200b)에 금속간 절연충(222)을 포함하는 절연충(220)이 형성된 것을 제외하고는 동일하다. 다시 말해, 도 39b의 칩 적충 반도체 패키지(1000-4)는 제2 칩(200b)의 전면(F2)측에 금속간 절연충(222) 및 패시베이션충(224)을 포함하는 절연충(220)이 형성될 수 있다. 그리고, 도 39b의 제2 칩(200b)의 제1 관통 실리콘 비아(230a)는 금속간 절연충(222)을 관통하지 않고, 절연충(220)에 포함된 배선 패턴을 통하여 제2 연결 부재(240)와 연결될 수 있다.

- [0207] 도 40은 본 발명의 기술적 사상의 일 실시예에 따른 칩 적층 반도체 패키지의 단면도이다.

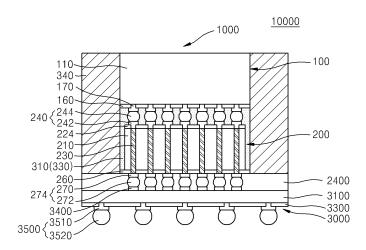

- [0208] 구체적으로, 본 실시예의 칩 적층 반도체 패키지(10000)는 보드 기판(3000) 및 상부 반도체 패키지(1000)를 포함할 수 있다. 상부 반도체 패키지(1000)는 도 13의 칩 적층 반도체 패키지(1000)와 동일할 수 있다. 그에따라, 상부 반도체 패키지(1000)의 각 구성부분에 대한 설명은 생략하거나 간략하게 기술한다. 도 40에서는 상부 반도체 패키지(1000)의 일예로 도 13의 칩 적층 반도체 패키지(1000)를 도시하지만, 앞서 다양하게 설명된 칩 적층 반도체 패키지도 상부 반도체 패키지에 적용될 수 있다.

- [0209] 보드 기판(3000) 상에 상부 반도체 패키지(1000)가 적흥되어 있고, 상부 반도체 패키지(1000)는 추가 밀봉재 (340)로 밀봉되어 있다. 상부 반도체 패키지(1000)는 접착 부재(2400)를 통해 보드 기판(3000)에 실장될 수 있다. 제2 칩(200)의 양측면은 언더필(310)로 이루어진 밀봉재(330)가 형성되어 있고, 밀봉재(330)의 양측벽으로 추가 밀봉재(340)에 의하여 상부 반도체 패키지(1000)를 밀봉한다. 추가 밀봉재(340)는 앞서 설명한 바와 같은 몰딩재로 형성할 수 있다.

- [0210] 보드 기판(3000)은 다양한 형태를 가질 수 있으며, 바디층(3100), 하부 보호층(3300), 상부 패드(3400) 및 연결부재(3500)를 포함할 수 있다. 연결 부재(3500)은 범프 패드(3510) 및 범프(3520)으로 구성될 수 있다. 바디층 (3100)에는 다수의 배선 패턴이 형성될 수 있다. 하부 보호층(3300)은 바디층(3100)을 보호하는 기능을 하는데, 예컨대, 솔더 레지스트일 수 있다.

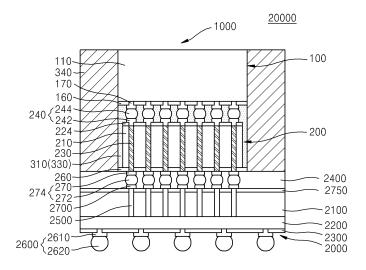

- [0211] 도 41은 본 발명의 기술적 사상의 일 실시예에 따른 칩 적층 반도체 패키지의 단면도이다.

- [0212] 구체적으로, 본 실시예의 칩 적충 반도체 패키지(20000)는 메인 칩(2000) 및 상부 반도체 패키지(1000)를 포함할 수 있다. 상부 반도체 패키지(1000)는 도 13의 칩 적충 반도체 패키지(1000)와 동일할 수 있다. 그에 따라, 상부 반도체 패키지(1000)의 각 구성부분에 대한 설명은 생략하거나 간략하게 기술한다. 도 41에서는 상부 반도체 패키지(1000)의 일예로 도 13의 칩 적충 반도체 패키지(1000)를 도시하지만, 앞서 다양하게 설명된 칩 적충 반도체 패키지도 상부 반도체 패키지에 적용될 수 있다.

- [0213] 메인 칩(2000) 상에 상부 반도체 패키지(1000)가 적층되어 있고, 상부 반도체 패키지(1000)는 추가 밀봉재(34 0)로 밀봉되어 있다. 제2 칩(200)의 양측면은 언더필(310)로 이루어진 밀봉재(330)가 형성되어 있고, 밀봉재(330)의 양측벽으로 추가 밀봉재(340)에 의하여 상부 반도체 패키지(1000)를 밀봉한다. 추가 밀봉재(340)는 앞서 설명한 바와 같은 몰딩재로 형성할 수 있다.

- [0214] 메인 칩(2000)은 상부 반도체 패키지(1000) 내에 포함된 제1 및 제2 칩(100, 200) 보다는 사이즈가 더 클 수 있다. 메인 칩(2000)의 수평 단면의 사이즈는 상부 반도체 패키지(1000)의 전체 수평 단면 사이즈, 즉 추가 밀봉 재(340)를 포함한 수평 단면의 사이즈와 동일할 수 있다. 상부 반도체 패키지(1000)는 접착 부재(2400)를 통해 메인 칩(2000)에 실장될 수 있다. 그에 따라, 상부 반도체 패키지(1000)의 추가 밀봉재(340)의 하면은 메인 칩(2000)의 외곽 부분에 접착 부재(2400)를 통해 접착될 수 있다.

- [0215] 메인 칩(2000)은 메모리 칩과 유사하게, 바디층(2100), 하부 절연층(2200), 패시베이션층(2300), 관통 실리콘 비아(2500), 연결 부재(2600, 2700), 및 보호층(2750)를 포함할 수 있다. 하부 절연층(2200) 및 패시베이션층 (2300) 내의 집적 회로층, 다층 배선 패턴은 메인 칩의 종류에 따라 다르게 형성될 수 있다. 메인 칩(2000)은

로직 칩, 예컨대, 중앙처리장치(central processing unit, CPU), 컨트롤러(controller), 또는 주문형 반도체 (application specific integrated circuit, ASIC) 등일 수 있다.

- [0216] 한편, 관통 실리콘 비아(2500) 및 그에 대응하는 연결 부재(2700)의 개수는 메인 칩(2000)으로 적충되는 상부 반도체 패키지(1000)의 제2 칩(200)의 제3 연결 부재(274)에 대응하는 개수로 형성될 수 있다. 경우에, 다른 개수 예컨대, 제3 연결 부재(274)보다 많은 개수의 관통 실리콘 비아(2500)가 형성될 수 있다.

- [0217] 메인 칩(2000)의 하면에 형성되는 연결 부재(2600)는 범프 패드(2610) 및 범프(2620)를 포함할 수 있고, 갯수가 관통 실리콘 비아(2500)보다 작을 수 있다. 그에 따라, 대응되는 연결 부재(2600)가 없는 관통 실리콘 비아 (2500)의 경우는 다층 배선 패턴을 통해 하나의 연결 부재(2600)에 합쳐 연결될 수 있다.

- [0218] 한편, 메인 칩(2000)에 형성된 연결 부재(2600)는 상부 반도체 패키지(1000)의 제3 연결 부재(274)보다는 사이 즈가 크다. 이는 메인 칩(2000)이 실장되는, 보드 기판(미도시)에 형성된 배선이 규격화되어 있거나 보드 기판 의 물질적 특성(예를 들어, 플라스틱)을 이유로 하여 조밀화하기 어려운 한계가 있기 때문이다. 이런 이유로, 앞서 관통 실리콘 비아(2500)의 모두가 연결 부재(2600) 각각으로 대응되지 않을 수 있다.

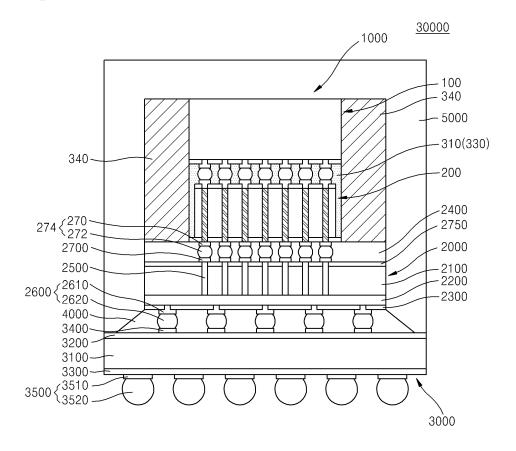

- [0219] 도 42는 본 발명의 기술적 사상의 일 실시예에 따른 칩 적층 반도체 패키지의 단면도이다.

- [0220] 구체적으로, 본 실시예의 칩 적층 반도체 패키지(30000)는 보드 기판(3000), 메인 칩(2000), 상부 반도체 패키지(1000), 언더필(4000) 및 외각 밀봉재(5000)를 포함할 수 있다. 상부 반도체 패키지(1000)와 메인 칩(2000)은 도 41에서 설명한 구조와 동일할 수 있다. 따라서, 상부 반도체 패키지(1000)와 메인 칩(2000)의 구성요소들에 대한 구체적인 설명은 생략한다.

- [0221] 상부 반도체 패키지(1000)와 메인 칩(2000)은 연결 부재(2600)를 통해 보드 기판(3000)에 실장될 수 있다. 보드 기판(3000)은 다양한 형태일 수 있고, 바디층(3100), 상부 보호층(3200), 하부 보호층(3300), 상부 패드(3400) 및 연결 부재(3500)를 포함할 수 있다. 바디층(3100)에는 다수의 배선 패턴이 형성될 수 있다. 연결 부재(3500)은 범프 패드(3510) 및 범프(3520)을 포함할 수 있다. 상부 보호층(3200) 및 하부 보호층(3300)은 바디층 (3100)을 보호하는 기능을 하는데, 예컨대, 솔더 레지스트일 수 있다.

- [0222] 외각 밀봉재(5000)는 상부 반도체 패키지(1000)와 메인 칩(2000)의 측면과 상면을 밀봉하고, 하면은 보드 기판 (3000)의 외곽 부분에 접착될 수 있다. 언더필(4000)은 메인 칩(2000)과 보드 기판(3000)의 연결부분을 채운다. 본 실시예에서 언더필(4000)이 메인 칩(2000)과 보드 기판(3000)의 연결부분에 형성되었으나, MUF 공정을 통해 외각 밀봉재(5000)가 형성되는 경우에 언더필(4000)은 생략될 수 있다.

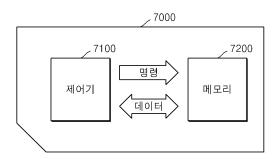

- [0223] 도 43은 본 발명의 기술적 사상의 칩 적충 반도체 패키지를 포함하는 메모리 카드를 개략적으로 보여주는 블럭구성도이다.

- [0224] 구체적으로, 메모리 카드(7000) 내에서 제어기(7100)와 메모리(7200)는 전기적인 신호를 교환하도록 배치될 수 있다. 예를 들어, 제어기(7100)에서 명령을 내리면, 메모리(7200)는 데이터를 전송할 수 있다. 제어기(7100) 및 /또는 메모리(7200)는 본 발명의 실시예들 중 어느 하나에 따른 칩 적층 반도체 패키지를 포함할 수 있다. 메모리(7200)는 메모리 어레이(미도시) 또는 메모리 어레이 뱅크(미도시)를 포함할 수 있다.

- [0225] 이러한 카드(7000)는 다양한 종류의 카드, 예를 들어 메모리 스틱 카드(memory stick card), 스마트 미디어 카드(smart media card; SM), 씨큐어 디지털 카드(secure digital; SD), 미니 씨큐어 디지털 카드(mini secure digital card; mini SD), 또는 멀티 미디어 카드(multi media card; MMC)와 같은 메모리 장치에 이용될 수 있다.

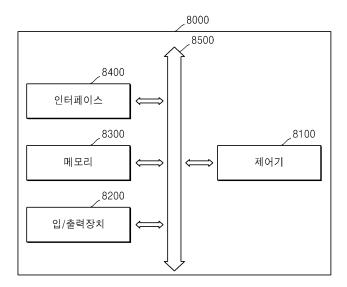

- [0226] 도 44는 본 발명의 기술적 사상의 칩 적층 반도체 패키지를 포함하는 전자시스템을 개략적으로 보여주는 블럭구성도이다.

- [0227] 구체적으로, 전자시스템(8000)은 제어기(8100), 입/출력 장치(8200), 메모리(8300) 및 인터페이스(8400)를 포함할 수 있다. 전자시스템(8000)은 모바일 시스템 또는 정보를 전송하거나 전송받는 시스템일 수 있다. 상기 모바일 시스템은 PDA, 휴대용 컴퓨터(portable computer), 웹 타블렛(web tablet), 무선 폰(wireless phone), 모바일 폰(mobile phone), 디지털 뮤직 플레이어(digital music player) 또는 메모리 카드(memory card)일 수 있다.

- [0228] 제어기(8100)는 프로그램을 실행하고, 전자시스템(8000)을 제어하는 역할을 할 수 있다. 제어기(8100)는, 예를 들어 마이크로프로세서(microprocessor), 디지털 신호 처리기(digital signal processor), 마이크로콘트롤러

(microcontroller) 또는 이와 유사한 장치일 수 있다. 입/출력 장치(8200)는 전자시스템(8000)의 데이터를 입력 또는 출력하는데 이용될 수 있다.

- [0229] 전자시스템(8000)은 입/출력 장치(8200)를 이용하여 외부 장치, 예컨대 개인용 컴퓨터 또는 네트워크에 연결되어, 외부 장치와 서로 데이터를 교환할 수 있다. 입/출력 장치(8200)는, 예를 들어 키패드(keypad), 키보드 (keyboard) 또는 표시장치(display)일 수 있다. 메모리(8300)는 제어기(8100)의 동작을 위한 코드 및/또는 데이터를 저장하거나, 및/또는 제어기(8100)에서 처리된 데이터를 저장할 수 있다. 제어기(8100) 및 메모리(8300)는 본 발명의 실시예들 중 어느 하나에 따른 칩 적층 반도체 패키지를 포함할 수 있다. 인터페이스(8400)는 상기시스템(8000)과 외부의 다른 장치 사이의 데이터 전송통로일 수 있다. 제어기(8100), 입/출력 장치(8200), 메모리(8300) 및 인터페이스(8400)는 버스(8500)를 통하여 서로 통신할 수 있다.

- [0230] 예를 들어, 이러한 전자시스템(8000)은 모바일 폰(mobile phone), MP3 플레이어, 네비게이션(navigation), 휴 대용 멀티미디어 재생기(portable multimedia player, PMP), 고상 디스크(solid state disk; SSD) 또는 가전 제품(household appliances)에 이용될 수 있다.

- [0231] 지금까지, 본 발명을 도면에 도시된 실시예를 참고로 설명하였으나 이는 예시적인 것에 불과하며, 본 기술 분야의 통상의 지식을 가진 자라면 이로부터 다양한 변형, 치환 및 균등한 타 실시예가 가능하다는 점을 이해할 것이다. 따라서 본 발명의 진정한 기술적 보호 범위는 첨부된 특허청구범위의 기술적 사상에 의해 정해져야 할 것이다.

## 부호의 설명

[0232] 10: 기저 웨이퍼, 20: 웨이퍼, 100, 200: 칩, 110: 바디층, 170, 240, 274: 연결 부재, 220: 절연층, 230: 관통 실리콘 비아, 310: 언더필, 312: 접착제, 320: 몰당재, 240: 330: 밀봉재, 110, 210: 바디층, 242: 범프 패드, 244: 펌프, 1000: 칩 적층 반도체 패키지,

# 도면10a

## 도면10b

## 도면10c

## 도면10d

## 도면32a

## 도면32b

## 도면32c

## 도면37a

## 도면37b

## 도면37c

## 도면37d

## 도면37e

#### 도면37f

#### 도면39a

#### 도면39b