# (19) 대한민국특허청(KR) (12) 공개특허공보(A)

| (51) Int. CI. <sup>6</sup><br>HO1L 21/306 | (11) 공개번호 특1998-033120<br>(43) 공개일자 1998년07월25일              |

|-------------------------------------------|--------------------------------------------------------------|

| (21) 출원번호<br>(22) 출원일자                    | 특 1997-054578<br>1997년 10월 24일                               |

| (30) 우선권주장<br>(71) 출원인                    | 8/740,124 1996년10월24일 미국(US)<br>어플라이드머티어리얼스,인코포레이티드 조셉제이.스위니 |

| (72) 발명자                                  | 미국 95054 캘리포니아 산타 클라라 바우어스 애브뉴 3050<br>콜린스,케네쓰               |

|                                           | 미국 95111 캘리포니아 산 호세 나이트쉐이븐 웨이 165                            |

|                                           | 라이스,마이클                                                      |

|                                           | 미국 94566 캘리포니아 플레산톤 클라넷 코우트 675                              |

|                                           | 트로우,존                                                        |

|                                           | 미국 95111 캘리포니아 산 호세 나이트쉐이븐 웨이 162                            |

|                                           | 버치버거,더글라스                                                    |

|                                           | 미국 95376 캘리포니아 트래시 체르니 스트리트 421                              |

|                                           | 아스카리남,에릭                                                     |

| (74) 대리인                                  | 미국 94087 캘리포니아 써니베일 폴라인 드라이브 1332<br>남상선                     |

| 심사청구 : 없음                                 |                                                              |

# (54) 유도 안테나를 가지고 플라즈마 이온 밀도의 방사 분포를조절할 수 있는 병렬 플레이트 전 <u>극 플라즈마 반응기</u>

#### 요약

반도체 제품, 이를테면 웨이퍼를 처리하기 위한 플라즈마 반응기가 개시되는데, 상기 플라즈마 반 응기는 반구형 또는 돔과 같은 3차원 형태를 갖는 오버헤드 시일링을 가지는 챔버를 포함한다. 상기 반응기는 상기 시일링 형태이거나 아닐 수 있는 시일링 상의 유도 안테나를 더 포함한다. 상기 시일링은 그것이 상기 안테나의 유도 필드를 위한 윈도우, 및 접지될 수 있거나 RF 전력이 인가되거나 전기적 부유가 허용될 수 있는 전극으로서 기능할 수 있도록 반도체 재료를 포함할 수 있다. 상기 반응기는 웨이퍼 표면에 걸친 플리즈마 이온 밀도가 웨이퍼 표면에 걸친 처리 균일성 을 위해 최적의 분포로 조절될 수 있도록 하는 여러 가지 형태를 포함한다.

# 대표도

### 도1

### 명세서

# 도면의 간단한 설명

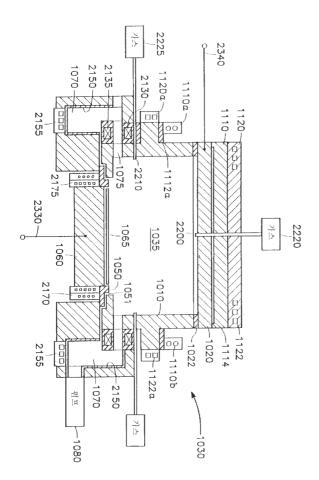

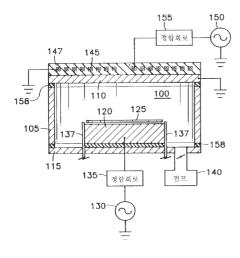

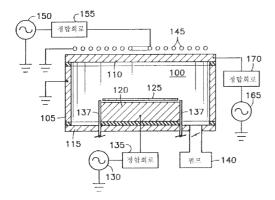

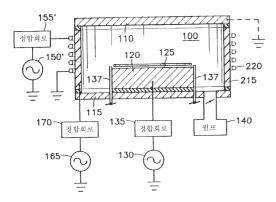

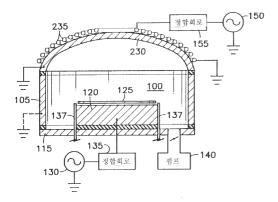

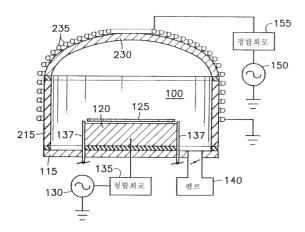

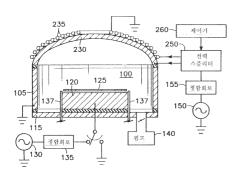

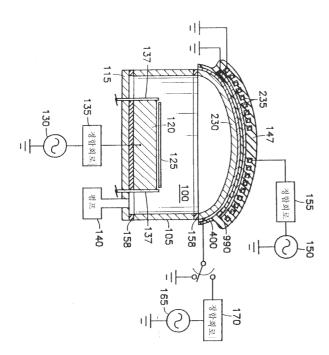

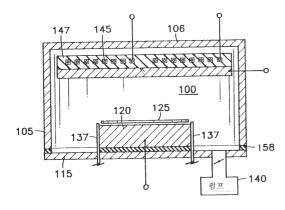

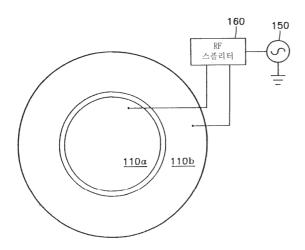

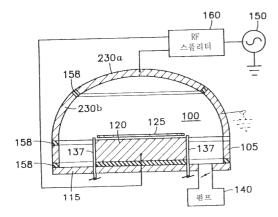

도 1은 평면 코일 안테나가 실리콘 시일링 위에 배치된 본 발명의 플라즈마 반응기의 제 1실시예 를 도시하는 도면.

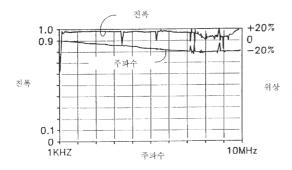

도 2는 전송 RF코일로부터 수신 RF코일로의 표준 순방향 전압 전송 계수를 도시하는 그래프이며, 도 1의 평면 실리콘 윈도우는 전송 RF코일과 수신 RF코일 사이에 배치됨.

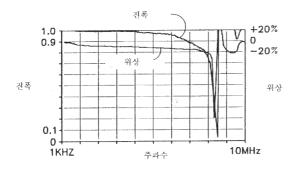

도 3은 전송 RF코일로부터 수신 RF코일로의 표준 순방향 전압 전송 계수를 도시하는 그래프이며, 실린더형 실리콘 윈도우는 전송 RF코일과 수신 RF코일 사이에 배치됨.

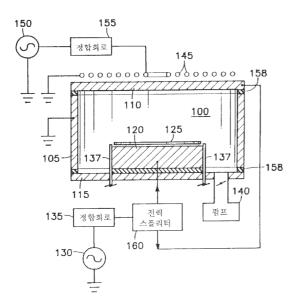

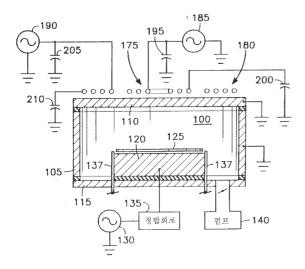

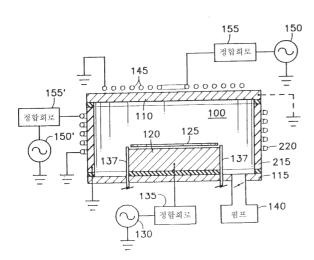

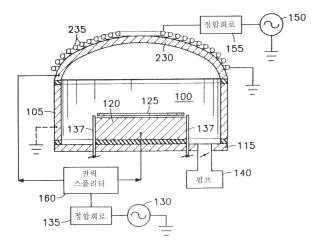

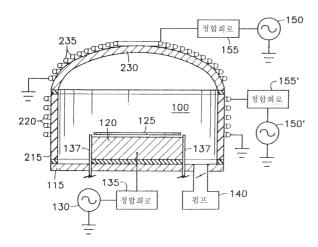

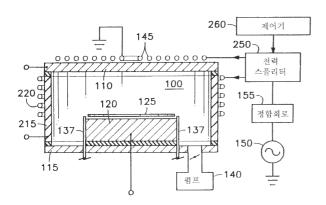

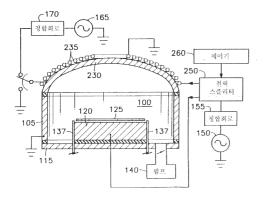

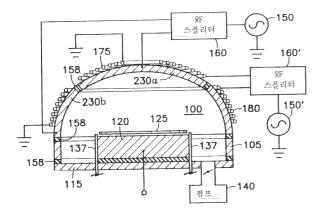

도 4는 실리콘 시일링 및 웨이퍼 페데스탈사이에서 출력을 분할하는 본 발명의 실시예를 도시하는 도면.

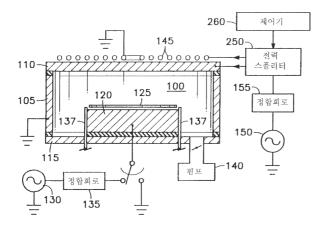

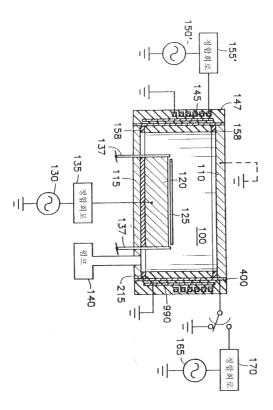

도 5는 웨이퍼 페데스탈, 오버헤드 유도성 코일 및 실리콘 시일링을 구동하기 위하여 별도 RF 전 력 소스를 이용하는 본 발명의 실시예를 도시하는 도면.

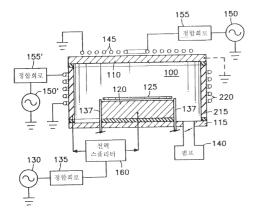

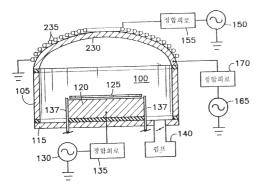

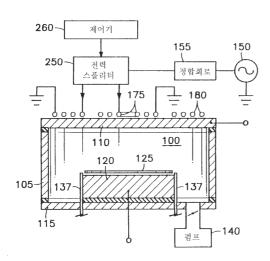

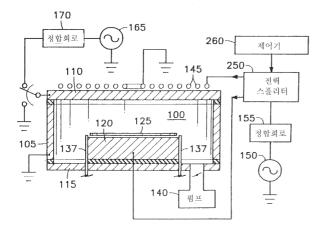

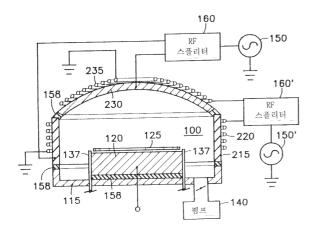

도 6은 오버헤드 유도성 코일이 별도로 전력이 공급되는 동심형 내부 및 외부 권선으로 분할되는 본 발명의 실시예를 도시하는 도면.

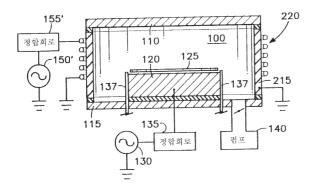

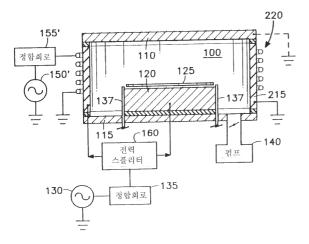

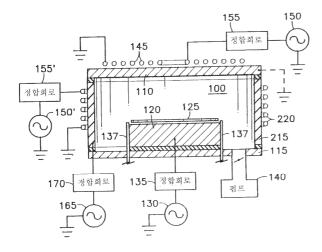

도 7은 실린더형 실리콘 측벽주위에 감긴 측면 유도 안테나를 이용하는 본 발명의 실시예를 도시

하는 도면.

도 8은 단일 RF 전력 소스로부터의 출력이 실리콘 측벽 및 웨이퍼 페데스탈사이에서 분할되는 도 7에 대응하는 실시예를 도시하는 도면.

도 9는 실리콘 측벽, 웨이퍼 페데스탈 및 유도성 측면 안테나를 구동하는 별도 RF 발생기를 이용하는 실시예를 도시하는 도면.

도 10은 실리콘 측벽 및 그 주위에 감긴 유도성 코일과 실리콘 시일링 및 오버헤드 유도 안테나를 결합시킨 실시예를 도시하는 도면.

도 11은 실리콘 측벽 및 웨이퍼 페데스탈사이의 전력 분할을 이용하는 도 10에 상응하는 실시예를 도시하는 도면.

도 12는 실리콘 시일링, 실리콘 측벽, 오버헤드 유도 안테나 및 측면 유도 안테나가 별도로 RF전력에 의하여 유도되는 실시예를 도시하는 도면.

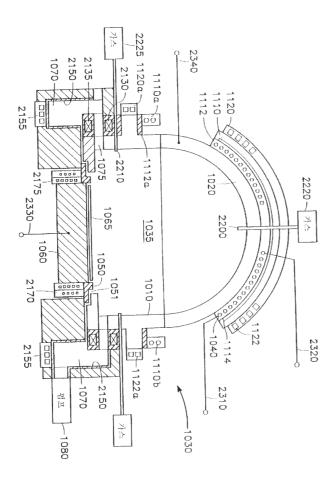

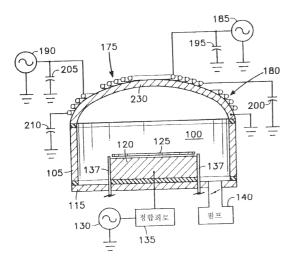

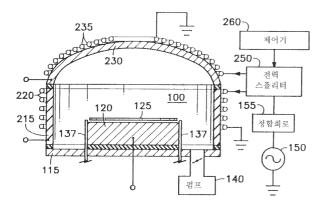

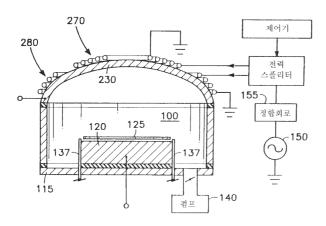

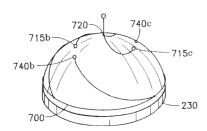

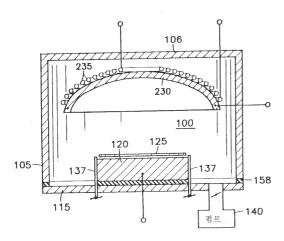

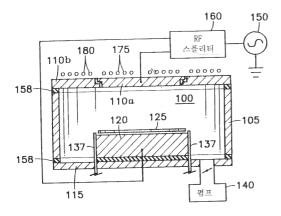

도 13a는 돔형 실리콘 시일링을 이용하는 도 1에 상응하는 실시예를 도시하는 도면.

도 13b는 돔형 실리콘 시일링을 이용하는 도 4에 상응하는 실시예를 도시하는 도면.

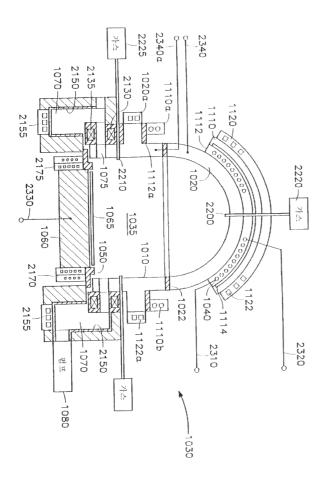

도 13c는 돔 형태의 실리콘 시일링을 채용한 도 5에 상응하는 실시예에 관한 예시도.

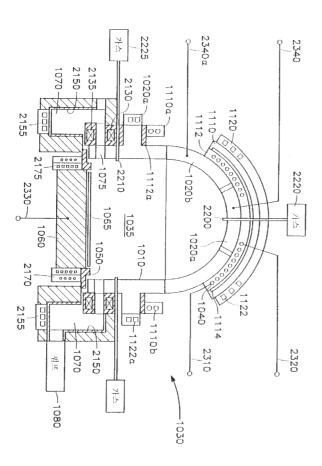

도 13d는 돔 형태의 실리콘 시일링을 채용한 도 6에 상응하는 실시예에 관한 예시도.

도 14는 돔 형태의 실리콘 시일링을 가지는 실시예 및 시일링을 덮고 실린더형 측벽 둘레를 에워싸는 실린더부로 이어지는 돔 형태를 가지는 유도 안테나에 관한 예시도.

도 15는 도 14에 상응하는 실시예에 관한 예시도, 다만 돔 형태 및 유도 안테나의 실린더부는 서로 이격되어 있으며 RF 전력으로 독립 구동됨.

도 16은 공통의 RF 전력이 유도 안테나의 내측 및 외측에서 분기하는, 도 6에 상응하는 실시예에 관한 예시도.

도 17a는 공통의 RF 전력이 돔 형태의 그리고 실린더형 형태의 유도 안테나부 사이에서 분기하는, 도 6에 상응하는 실시예에 관한 예시도.

도 17b는 별개의 내측 및 외측의 돔 형태의 유도 안테나들을 가지며, 그 사이에서 공통의 RF 발생기로부터의 전력이 분기하는, 실시예에 관한 예시도.

도 18은 공통의 RF 발생기로부터의 전력이 오버헤드의 유도 안테나 및 측면의 유도 안테나 사이에서 분기하는, 도 10에 상응하는 실시예에 관한 예시도.

도 19는 공통의 RF 발생기로부터의 전력이 오버헤드의 유도 안테나 및 실리콘 시일링 사이에서 분기하는, 도 1에 상응하는 실시예에 관한 예시도.

도 20은 공통의 RF 발생기로부터의 전력이 오버헤드의 유도 안테나 및 웨이퍼 페데스탈 사이에서 분기하는, 도 1에 상응하는 실시예에 관한 예시도.

도 21은 공통의 RF 발생기로부터의 전력이 오버헤드의 유도 안테나 및 돔 형태의 실리콘 시일링 사이에서 분기하는 돔 형태의 시일링을 가지는, 도 13a에 상응하는 실시예에 관한 예시도.

도 22는 공통의 RF 발생기로부터의 전력이 오버헤드의 유도 안테나 및 웨이퍼 페데스탈 사이에서 분기하는 돔 형태의 시일링을 가지는, 도 13a에 상응하는 실시예에 관한 예시도.

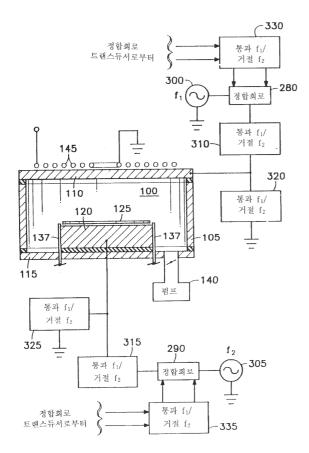

도 23은 웨이퍼 페데스탈 및 실리콘 시일링이 RF 전력으로 개별적으로 구동되며 각각은 다른 것에 대하여 카운터 전극으로서의 역할을 하는 실시예에 관한 예시도.

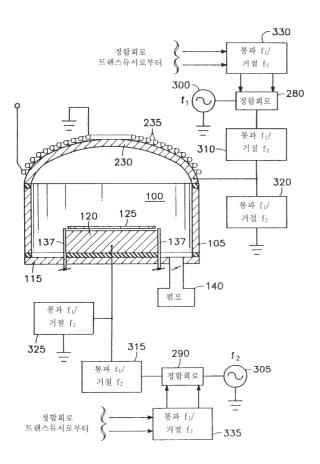

도 24는 실리콘 시일링이 돔 형태인 도 23에 상응하는 실시예에 관한 예시도.

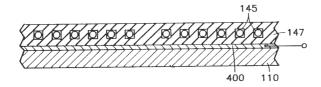

도 25a는 전도성 후면을 포함하는 실리콘 시일링의 실시예에 관한 측면도.

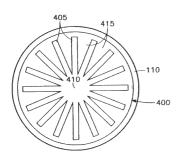

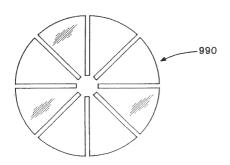

도 25b는 전도성 후면의 한 실시예에 관한 평면도.

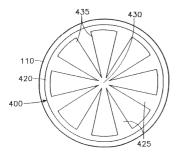

도 25c는 전도성 후면의 다른 실시예에 관한 평면도.

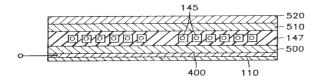

도 26은 지지 기판에 고정된 실리콘 시일링의 실시예에 관한 측면도.

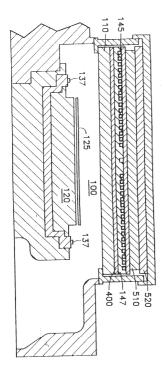

도 27은 지지 기판이 오버헤드 유도 안테나의 절연 홀더가 되는 도 26의지지 기판에 상응하는 실 시예의 측면도.

도 28은 안테나 홀더가 도전성인 본 발명에 따른 실시예의 측면도.

도 29는 도전성 안테나 홀더는 내측 및 외측의 오버헤드 유도 안테나들을 포함하는 환상의 개구부 쌍을 가지는 도 28에 상응하는 실시예의 측면도.

도 30a는 오버헤드 유도 안테나의 비동심 실시예에 관한 평면도.

도 30b 및 30c는 각각 평면 및 돔 형태를 가지는 도 30a의 유도 안테나에 관한 대안적 구현예에 관한 측면도.

도 31a는 오버헤드 유도 안테나의 또다른 비동심 실시예에 관한 평면도.

도 31b 및 31c는 각각 평면 및 돔 형태를 가지는 도 31a의 유도 안테나에 관한 대안적 구현예에

관한 측면도.

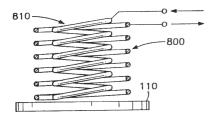

도 32는 오버헤드 유도 안테나의 이중 실린더 나선형 실시예에 관한 측단면도.

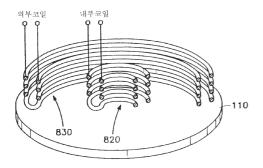

도 33은 도 16의 내측 및 외측 안테나에 관한 도 32에 도시된 유형의 동심 실린더 나선형 유도 안테나 쌍에 관한 측단면도.

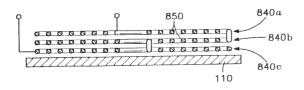

도 34는 유도 안테나의 층으로 구성된 오버헤드 유도 안테나의 실시예에 관한 측단면도.

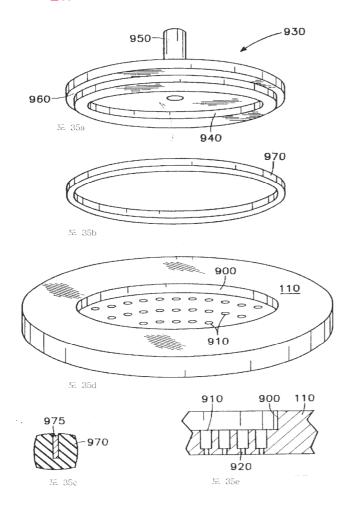

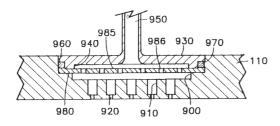

도 35a 내지 35e는 중앙 가스 공급식 실리콘 시일링의 한 실시예에 관한 예시도로써, 도 35a는 가스 공급 상부에 관한 밑면 투시도, 도 35b는 환상 시일의 밑면 투시도, 도 35c는 도 35b의 시일에 관한 단면도, 도 35d는 가스 공급 홀을 보여주는 실리콘 시일링에 관한 투시도, 그리고 도 35e는도 35d의 실리콘 시일링에 관한 부분 단면도.

도 36a는 실리콘 웨이퍼 배플에 의하여 격리된 한쌍의 가스 플레늄을 가지는 중앙 가스 공급식 실리콘 시일링의 다른 구현예에 관한 단면도.

도 36b는 도 36a에 따른 대안적 실시예에 관한 예시도.

도 37a는 페러데이 시일드가 어떻게 도 1의 실시예에 포함될 수 있는가를 보여주는 예시도.

도 37b는 도 37a의 페러데이 시일드에 관한 평면도.

도 38a는 페러데이 시일드가 어떻게 돔 형태의 시일링을 가지는 도 10의 실시예에 포함될 수 있는가를 보여주는 예시도.

도 38b는 페러데이 시일드가 어떻게 실린더형 반도체 윈도우 전극 및 유도 안테나를 가지는 도 7-9의 실시예에 포함될 수 있는가를 보여주는 예시도.

도 39a는 본 발명의 바람직한 실시예에 관한 상세한 측단면도.

도 39b는 오버헤드 유도 안테나에서 채용된 도체에 관한 축방향 단면도.

도 40은 반도체 윈도우 및 유도 안테나가 반응실 안에 있는 대안적 실시예에 관한 예시도.

도 41a는 반도체 윈도우가 돔 형태인, 도 40에 상응하는 실시예.

도 41b는 반도체 윈도우가 실린더형이며 유도성 코일도 실린더형인, 도 40에 따른 실시예에 관한 예시도.

도 42 및 43은 각각 반도체 윈도우 전극 단편의 측면도 및 평면도.

도 44는 반도체 윈도우가 돔 형태인, 도 42에 따른 실시예에 관한 예시도.

도 45는 RF 전력이 반도체 윈도우 전극 및 측벽 전극 사이에서 분기하고, 그 자체는 반도체 윈도 우 전극의 단편화된 부분일 수 있는, 실시예에 관한 예시도.

도 46 및 47은 반도체 윈도우 전극의 외측 부분이 접지되고 RF 전력은 반도체 윈도우 전극 및 웨이퍼 페데스탈의 중심 부분 사이에서 분기하는, 도 42 및 44의 실시예의 변형된 예시도.

도 48a는 웨이퍼에 대한 처리 영역 내에 플라즈마를 갖는 완전히 반도체로 된 수용체를 가지는 본 발명의 한 실시예의 플라즈마 반응기에 관한 측면 절취도.

도 48b는 플라즈마가 웨이퍼 페데스탈에 관하여 횡방향이 아닌 고립된 축방향을 하는 것을 제외하고는, 도 48a에 상응하는 플라즈마 반응기에 관한 측면 절취도.

도 48c는 시일링의 다른 부분이 다른 RF 주파수로 구동되는, 도 48a에 상응하는 실시예에 관한 예시도.

도 49는 완전히 반도체로 된 수용체가 단결정이라는 것을 제외하고, 도 48a에 상응하는 플라즈마 반응기에 관한 측면 절취도.

도 50은 반도체 수용체가 디스크 중심 부분 및 실린더형 스커트를 가지는 환상 부분으로 나뉘는 것을 제외하고, 도 48a에 상응하는 플라즈마 반응기에 관한 측면 절취도.

도 51은 반도체 수용체가 디스크 중심 부분, 환상 측면 부분, 그리고 분리된 실린더형 스커트를 가지는 환상 부분으로 나뉘는 것을 제외하고, 도 48a에 상응하는 플라즈마 반응기에 관한 측면 절 취도.

도 52는 분리된 내측 및 외측 유도 코일들을 가지는 도 50의 플라즈마 반응기에 관한 예시도.

도 53은 분리된 내측 및 외측 유도 코일들을 가지는 도 51의 플라즈마 반응기에 관한 예시도.

도 54는 반도체 수용체의 실린더형 스커트 둘레에 감은 실린더형 유도 코일을 가지는, 도 48a의 플라즈마 반응기에 관한 예시도.

도 55는 반도체 수용체의 실린더형 스커트 둘레에 감은 실린더형 유도 코일을 가지는, 도 49의 플라즈마 반응기에 관한 예시도.

도 56은 반도체 수용체의 실린더형 스커트 둘레에 감은 실린더형 유도 코일을 가지는, 도 50의 플라즈마 반응기에 관한 예시도.

도 57은 반도체 수용체의 실린더형 스커트 둘레에 감은 실린더형 유도 코일을 가지는, 도 51의 플라즈마 반응기에 관한 예시도.

- 도 58은 반도체 수용체의 시일링 부분이 돔 형태라는 것을 제외하고 도 48a에 상응하는 플라즈마 반응기의 측면 절취도.

- 도 59는 반도체 수용체의 시일링 부분이 돔 형태가라는 것을 제외하고 도 49에 상응하는 플라즈마 반응기의 측면 절취도.

- 도 60은 반도체 수용체의 시일링 부분이 돔 형태라는 것을 제외하고 도 50에 상응하는 플라즈마 반응기의 측면 절취도.

- 도 61은 반도체 수용체의 시일링 부분이 돔 형태라는 것을 제외하고 도 51에 상응하는 플라즈마 반응기의 측면 절취도.

- 도 62는 반도체 수용체의 시일링 부분이 돔 형태라는 것을 제외하고 도 52에 상응하는 플라즈마 반응기의 측면 절취도.

- 도 63은 반도체 수용체의 시일링 부분이 돔 형태라는 것을 제외하고 도 53에 상응하는 플라즈마 반응기의 측면 절취도.

- 도 64는 반도체 수용체의 시일링 부분이 돔 형태라는 것을 제외하고 도 54에 상응하는 플라즈마 반응기의 측면 절취도.

- 도 65는 반도체 수용체의 시일링 부분이 돔 형태라는 것을 제외하고 도 55에 상응하는 플라즈마 반응기의 측면 절취도.

- 도 66은 반도체 수용체의 시일링 부분이 돔 형태라는 것을 제외하고 도 56에 상응하는 플라즈마 반응기의 측면 절취도.

- 도 67은 반도체 수용체의 시일링 부분이 돔 형태라는 것을 제외하고 도 57에 상응하는 플라즈마 반응기의 측면 절취도.

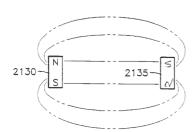

- 도 68a는 도 48-67의 실시예에서 선택적으로 채용된 플라즈마 보유 자석의 제 1 버전에 관한 다이 어그램.

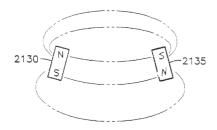

- 도 68b는 도 48-67의 실시예에서 선택적으로 채용된 플라즈마 보유 자석의 제 2 버전에 관한 다이 어그램.

- 도 68c는 도 48-67의 실시예에서 선택적으로 채용된 플라즈마 보유 자석의 제 3 버전에 관한 다이 어그램.

- 도 68d는 도 48-67의 실시예에서 선택적으로 채용된 플라즈마 보유 자석의 제 4 버전에 관한 다이 어그램.

- 도 68e는 도 48-67의 실시예에서 선택적으로 채용된 플라즈마 보유 자석의 제 5 버전에 관한 다이 어그램.

- 도 69는 용량성 결합을 채용한, 도 48a에 상응하는 본 발명의 대안적 실시예의 플라즈마 반응기에 관한 측면 절취도.

- 도 70은 반도체 수용체의 시일링 부분이 반구형인 것을 제외하고 도 48a에 상응하는 플라즈마의 측면 절취도.

- 도 71은 반도체 수용체의 시일링 부분이 반구형인 것을 제외하고 도 49에 상응하는 플라즈마의 측 면 절취도.

- 도 72는 반도체 수용체의 시일링 부분이 반구형인 것을 제외하고 도 50에 상응하는 플라즈마의 측 면 절취도.

- 도 73은 반도체 수용체의 시일링 부분이 반구형인 것을 제외하고 도 51에 상응하는 플라즈마의 측 면 절취도.

- 도 74는 반도체 수용체의 시일링 부분이 반구형인 것을 제외하고 도 52에 상응하는 플라즈마의 측면 절취도.

- 도 75는 반도체 수용체의 시일링 부분이 반구형인 것을 제외하고 도 53에 상응하는 플라즈마의 측 면 절취도.

- 도 76은 반도체 수용체의 시일링 부분이 반구형인 것을 제외하고 도 54에 상응하는 플라즈마의 측 면 절취도.

- 도 77은 반도체 수용체의 시일링 부분이 반구형인 것을 제외하고 도 55에 상응하는 플라즈마의 측 면 절취도.

- 도 78은 반도체 수용체의 시일링 부분이 반구형인 것을 제외하고 도 56에 상응하는 플라즈마의 측 면 절취도.

- 도 79는 반도체 수용체의 시일링 부분이 반구형인 것을 제외하고 도 57에 상응하는 플라즈마의 측 면 절취도.

- 도 80은 다수의 방사상으로 그룹 지어진 온도 제어 지역들, 다수의 방사상 대칭인 유도성 코일, 시일링 형태와 일치하지않는 유도성 코일을 가지는 돔형 또는 반구형 반도체 윈도우 전극을 가지 는 플라즈마 반응기에 관한 예시도.

\*도면의 주요부분에 대한 부호의 설명\*

100 : 챔버 105 : 측벽

110 : 시일링 120 : 웨이퍼 페데스탈 125 : 제품 145 : 유도 코일 안테나

#### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 반도체 웨이퍼와 같은 처리될 제품의 삽입을 위한 병렬 플레이트, 및 상기 병렬 플레이트 중 하나를 통해 상기 반응기의 내부에 RF 전력을 결합하는 유도성 코일 안테나를 가지는 플라즈마 반응기에 관한 것이다.

마이크로일렉트로닉 반도체 웨이퍼를 처리하기 위한 오글레의 미국특허 제 4,948,458호에 개시된 종류의 유도 결합된 플라즈마 반응기는 병렬 플레이트 용량성 결합 플라즈마 반응기보다 이점을 가진다. 예를 들어, 유도 결합 플라즈마 반응기는 높은 이온 밀도(예를 들어, 약 10<sup>11</sup> 이온/cm³)를 얻는다. 또한, 플라즈마 이온 밀도 및 플라즈마 이온 에너지는 제품 또는 웨이퍼에 바이어스전력을 인가함으로써 유도 결합 플라즈마 반응기에서 독립적으로 제어될 수 있다. 이에 반하여, 용량성 결합 플라즈마 반응기는 상대적으로 낮은 플라즈마 이온 밀도(예를 들어, 약 10<sup>10</sup> 이온/cm³)를 제공하며, 이온 밀도 및 이온 에너지를 독립적으로 제어할 수 없다. 실리콘 이산화물을 에칭하기 위하여 이용된 유도 결합 플라즈마 반응기에 의하여 제공된 우수한 이온 대 중립자 밀도비는 예를 들어 작은 에칭 부분(예를 들어, 0.5미크론 크기)에서 유수한 성능을 제공하며, 또한 양호한 에칭 비등방성, 양호한 에칭 형상 및 양호한 에칭 선택성을 제공한다. 이에 반하여, 병렬 플레이트 용량성 결합 플라즈마 반응기는 양호하지 못한 이온 대 중립자 밀도비 때문에 약 0.25미크론의 크기에서 에칭을 중지하거나, 양호하지 못한 에칭 선택성 및 에칭 프로파일을 나타 낸다.

상기 미국특허 4,948,458호에 개시된 유도 결합 플라즈마 반응기는 챔버 시일링 위에 배치되고 처리될 반도체 웨이퍼와 접하는 평면 코일을 가지며, 따라서 웨이퍼 표면 위에 최적의 균일한 RF 유도성 필드를 제공한다. 이를 위하여, 반응기 챔버를 밀봉하여 챔버가 진공화되도록 하는 시일링은 상기 코일로부터 RF 유도성 필드에 대하여 투과성을 가져야하며, 따라서 석영과 같은 유전체이다. 상기 시일링은 석영이외에 알루미늄 산화물과 같은 유전체 재료로 만들어질 수 있다. 그러나 알루미늄 산화물과 같은 다른 재료는 스퍼터링 때문에 석영보다 오염물을 더 많이 발생시키는경향이 있다.

용량성 결합 플라즈마 반응기는 병렬 플레이트 전국사이의 공간을 감소시킴으로써 챔버 부피가 감소하여 제품 위에 플라즈마를 양호하게 한정하거나 집중시키는 한편 반응기가 상대적으로 높은 챔버 압력(예를 들어, 200밀리토르)에서 동작될 수 있도록 하는 장점을 가진다. 이에 반하여, 유도결합 플라즈마 반응기는 FF 유도성 필드의 큰 표피 깊이 때문에 큰 부피를 가지며, 재결합에 의한 플라즈마 이온의 손실을 방지하기 위하여 낮은 압력(예를 들어, 10밀리토르)에서 작동되어야 한다. 상기 미국특허 제 4,948,458호의 유도 결합 플라즈마 반응기의 상업적 실시예에서, 큰 챔버부피의 요구는 상당히 큰 영역의 측벽에 의하여 충족된다. 웨이퍼 바이어스의 다른 FF 접지 복귀부족은 챔버 측벽이 유도성이고 접지 또는 FF 복귀면으로 작용하는 수단을 에칭(오버헤드 코일로부터의 FF 유도성 필드를 허용하도록 유전체 윈도우를 요구하기 때문에)하기 위하여 사용된다. 그러나, 측벽은 양호하지 못한 접지면을 가지는데, 이는 상기 접지면이 웨이퍼 입출구용 슬릿 밸브, 가스 분배 포트 또는 장치와 같은 많은 불연속부분을 가지기 때문이다. 상기 불연속부분은 균일하지 못한 전류 분배를 야기하며, 이는 웨이퍼 표면에 대하여 플라즈마 이온의 분포를 왜곡시킨다. 이로 인한 측벽으로의 유출 전류 흐름은 웨이퍼 표면에 대하여 균일하지 못한 플라즈마 분배를 야기한다.

용량성 및 유도성 결합을 연합하기 위한 한 방법은 콜린스등의 유럽특허출원 제 0 520 519 a1호에 기술된 바와 같이 병렬 플레이트 플라즈마 반응기의 측벽에 감긴 측면 코일을 제공하는 것이다. 이를 위하여, 실린더형 챔버 측벽은 챔버로의 측면 코일의 RF 유도성 필드를 허용하기 위하여 석영과 같은 부도체이여야 한다. 이러한 종류의 플라즈마 반응기의 주요 문제점은 웨이퍼 표면사이에 처리 비균일성이 나타날 수 있다는 것이다. 예를 들어, 에칭율은 웨이퍼 주변에서 상당히 높고, 웨이퍼 중심에서는 상당히 낮아, 처리 윈도우를 제한한다. 사실, 에칭 공정은 웨이퍼 주변에서 계속되는 동안 웨이퍼 중심 근처에서는 정지할 수 있다. 반응기 챔버의 측벽을 따라 형성된 유도 코일 안테나의 배치, 챔버 중심쪽으로의 상대적으로 짧은(예를 들어, 2cm) 외피 깊이(또는 대부분의 RF 전력이 흡수되는 깊이) 및 상기 측면으로부터 반응기 챔버로의 에칭 선구물질 가스의유입은 대부분의 에천트 가스 및 라디컬 생성을 챔버 측벽 근처 또는 웨이퍼 주변으로 한정시킨다. 여기서 사용된 용어 에천트 가스 라디컬은 에칭 반응을 수행하는 플루오르 카본 이온 및 라디컬, 그리고 플루오르 하이드로카본 이온 및 라디컬을 포함하는 여러 가지 화학 물질을 말한다. 자유 플루오르 이온 및 라디컬의 수는 선택된 에칭 공정이 요구된다면 공지된 기술에 의하여 바람직하게 최소화된다. 플라즈마 소스 전력에 의하여 생성된 에너지 전자는 공정 선구물질 가스와 상호작용 하여 요구되는 에천트 이온과 라디컬을 발생시키고, 또한 정교한 에칭 공정에 이용되는 중합반응에 필요한 분자 또는 원자 카본을 생성한다. 웨이퍼 중심 근처의 에칭 공정은 챔버 측벽 근처로부터 이동하고 중립자 또는 이온과 충돌함으로써 상기 이동로를 따라 재결합하기 전에 웨이

퍼 중심에 도달하는 에너지 전자에 의존하며, 따라서 에칭 공정은 웨이퍼 표면 전체에 걸쳐 균일 하지 않다. 이들 문제점은 에칭 공정에서 중합 반응 역할 측면에서 더 잘 이해된다.

플루오르 카본(cxfx) 또는 플루오르 하이드로카본 화학물질을 이용하는 중합 반응은 일반적인 실리 콘 이산화물 에칭 공정에 이용되어, 예를 들어 비등방성 또는 프로파일 및 에칭 선택성을 향상시 키며, 이는 전기화학 학회 논문 제 137권 제 8호(1990년 8월) 베리야등의 플라즈마 에칭에 이용되 는 플라즈마 중합 반응을 위한 표면 운동 모델페이지 2575-2581중 제 1페이지에 기술되어 있다. 반응기 챔버로 유입된  $\mathbf{c}_2\mathbf{f}_6$ 과 같은 플루오르 카본 또는 플루오르 하이드로카본과 같은 에칭 선구물 질 가스는 카본과 마찬가지로 플라즈마의 에너지 전자와 탄성 없이 충동하여 에천트 이온 및 라디 컬로 한다. 전술한 바와 같이, 상기 에천트 이온과 라디컬은 예를 들어 자유 플루오르 이온과 라 디컬과 같은 플루오르 카본 또는 플루오르 하이드로카본 이온과 라디컬을 포함한다. 상기 자유 플루오르 이온 및 라디컬은 예를 들어 에칭 공정이 폴리실리콘과 같은 비산소 함유 재료에 대하여 선택된다면 바람직하게 세정을 통하여 최소화된다. 카본 및 적어도 일부의 플루오르 카본 또는 플루오르 하이드로카본 이온 및 라디컬은 중합체 형성이다. 또한 플라즈마에는 여기된 중립자 또 는 분리되지 않은 물질 및 에칭 부산물이 존재한다. 중합체 형성 라디컬 및 카본은 에칭 프로파 일을 다음과 같이 향상시키는바, 즉 에칭 부분의 측벽 위에만 형성함으로써(수평면상의 형성은 플라즈마로부터의 하방향 에너지 흐름에 의하여 방지됨) 중합체는 측방향 에칭을 방지하고 따라서비등방성(좁고 깊은) 프로파일을 형성한다. 중합체 형성 이온 및 라디컬은 또한 실리콘 산화물에칭 선택성을 향상시키는데, 이는 중합체가 바람직한 조건하에서 일반적으로 실리콘 산화물위에 형성되지 않으며 에칭되는 실리콘 산화물층 하부에 놓이지만 에칭되지 않는 실리콘 또는 다른 물 질 위에 형성되지 않는다. 따라서, 상부의 실리콘 산화물층이 하부의 폴리실리콘층을 노출시킴 으로써 완전하게 에칭되자마자, 노출된 폴리실리콘층과 접하는 플라즈마내의 중합체 형성 이온 및 라디컬은 즉시 중합체층을 형성하기 시작하여 추가의 에칭을 방지한다.

에칭 공정중의 상기와 같은 중합반응은 에천트와 중합체의 주의 깊은 균형을 요구하며, 에천트 밀도는 일반적으로 적합한 중합체 형성의 방해를 방지하기 위하여 공핍 레벨에서 있다. 그 결과, 웨이퍼 주변에 형성된 에천트 가스와 라디컬의 중요한 균형은 웨이퍼 중심에 도달하기 전에 소모되며, 또한 웨이퍼 중심상의 에칭 이온 밀도를 감소시킨다. 이는 웨이퍼 중심에서 근처에서 낮은 에칭율 또는 에칭 중지를 야기한다.

웨이퍼 주변에 더 많은 이온이 존재하는 한 이유는 측벽에서의 유도성 코일의 위치가 측벽 근처에서 발생되는 이온 생성 전자를 보다 더 가열하기 때문이며, 상기 전자는 에천트 이온과 라디컬의 발생이 웨이퍼 중심에서 덜 발생하도록 중심에 도달하기 전에 재결합에 의하여 냉각 및/또는 소모된다. 또한, 측면으로부터의 에천트 선구물질 가스의 유입 및 측면으로부터의 플라즈마 소스 전력의 결합은 상기 측면에 적합한 불균일한 에천트 이온/라디컬 분포를 형성한다. 측면 근처(웨이퍼 주변 상의)에 형성된 많은 이온과 라디컬은 석영 측벽을 에칭함으로써 소모되며 웨이퍼 중심을 에칭하기 위하여 이용되지 않으며, 한편 측면 근처에서 발생된 이온/라디컬 형태 에너지 전자는웨이퍼 중심에 도달하기 전에 다른 물질과 충돌하여 손실되어 웨이퍼 중심에서 에천트 이온 밀도가 감소한다. (석영 측벽의 에칭은 반응기를 동작시키는 비용을 상당히 증가시키는데, 이는 매우비싼 부재— 석영 측벽—를 소모하기 때문이며, 이는 주기적으로 교환되어야 한다.) 웨이퍼 중심에서 에천트 가스의 상대적 부족에 의하여 웨이퍼 중심에서 중합체가 빠르게 형성되며, 일부 경우에는 중합체 형성은 특히 0.5미크론 이하의 크기에서 에칭 공정을 위협하고 이를 중지시킨다. 상기와 같은 에칭 중지는 좁은 에칭 깊이에서 큰 에칭 크기 또는 짧은 에칭 시간을 발생시킨다.

전술한 설명은 웨이퍼 주변 근처의 풍부한 에천트 이온과 라디컬이 선택된 공정 조건하에서 중합 반응을 방해할 수 있어 에칭 선택성을 방해하고, 따라서 웨이퍼 주변에서 상당히 높은 에칭율을 발생시키는 것 이외에 웨이퍼 주변에서 하부층의 구멍을 발생시킨다는 것이다. 관련된 문제점은 상기 석영 측벽의 에칭에 의하여 방출되는 산호와 결합되며 웨이퍼 주변에 제공되는 챔버 측벽/웨 이퍼 주변 근처의 가열된 전자는 웨이퍼 주변 근처의 포토레지스트 마스크를 마모시킨다는 것이 다. 상기 마모는 깍인부분을 발생하고, 여기서 포토레지스트 마스크에 의하여 형성된 코너는 에 칭되고, 따라서 원하지 않는 점점 가늘어지는 에칭 프로파일을 야기한다.

전술한 설명으로부터, 웨이퍼 에지에서 구멍과 깍인부분의 방지와 웨이퍼 중심에서 에칭 중지의 방지는 모두 얻을 수 없으며, 이는 성공적인 에칭 공정이 전체 웨이퍼 표면에서 구현될 수 있는 공정 파라미터를 가지는 것이 매우 어렵다는 것을 나타낸다. 웨이퍼 주변의 과도한 에칭을 방지 하기 위하여, 다른 입자(예를 들어, 중합체 형성 이온 또는 라디컬 및 카본)에 대하여 플라즈마내 의 에천트 이온과 라디컬의 밀도가 감소될 수 있지만, 이는 웨이퍼 중심에서 에칭 중지를 발생시 킬 수 있다. 반대로, 웨이퍼 중심에서 에칭 중지를 방지하기 위하여, 플라즈마의 에천트 이온 밀 도가 증가될 수 있지만, 이는 웨이퍼 주변 근처에 구멍 또는 깍인부분을 발생시킬 수 있다. 따라 서, 성공적으로 전체 웨이퍼를 에칭하기 위한 공정 윈도우는 매우 좁다.

병렬 플레이트 플라즈마 반응기에서, 플라즈마의 자유 플루오르의 밀도는 반응기 챔버 상부 또는 그 근처에서 실리콘과 같은 소기 물품(scavenging article)을 도입함으로써 제어될 수 있다. 소기 물품으로부터 물리적으로 에칭되고(스퍼터링되고), 화학적으로 에칭되거나 반응성 이온 에칭되는 실리콘 원자는 플루오르 이온과 라디컬과 결합되어 플라즈마에서 플루오르 이온과 라디컬 밀도를 감소시킨다. 실리콘 원자가 소기 물품으로부터 물리적 또는 화학적 에칭되는 에칭율을 제어함으로써, 플라즈마에서 자유 플루오르 이온과 라디컬의 양이 전술한 좁은 공정 윈도우를 만족시키는데 요구되는 만큼 조절(예를 들어, 감소)될 수 있다. 물리적 또는 화학적 에칭율은 소기 물품의 온도를 제어함으로서 그리고/또는 소기 물품상의 이온 충돌 비율을 제어함으로써 제어될 수 있다. 소기 물품의 표면은 RF 전력 또는 가열에 의하여(플라즈마로 실리콘 원자를 방출하기 위하여) 활성화될 수 있다. 소기 물품의 온도를 중합반응이 발생하는 온도이하로 유지함으로써, 중합체는 소기 물품 표면 위에 축적되고 이로부터 실리콘 원자가 방출되는 것을 차단한다. 소기 물품의 온도를 농축 온도이상으로 상승시킴으로써, 표면에는 중합체가 존재하지 않으며, 따라서 플라

조마로 실리콘 원자가 방출하도록 한다. 온도를 더 증가시키면 실리콘 원자가 소기 물품 표면으로부터 플라즈마로 방출하는 속도가 증가한다. RF 전력에 의하여 소기 물품을 활성화시키는 것과 관련하여, 소기 물품의 이온 충돌 비율은 소기 물품 근처의 상부 병렬 플레이트 전극에 (직접 또는 간접으로) 인가된 RF 전위 또는 바이어스에 의하여 영향을 받는다. 이러한 방식으로의 자유플루오르 밀도 감소는 에칭율을 감소시킬 뿐만 아니라 중합체의 카본 함유량을 풍부하게 하여, 웨이퍼 중심에서 구멍을 방지하기 위하여 에칭 공정상의 중합체의 영향을 증가시키지만, 웨이퍼 중심에서 에칭 중지의 위험성을 증가시킨다. 반대로, 자유 플루오르 밀도의 증가는 에칭율을 증가시킬 뿐만 아니라 중합체의 카본 함유량을 감소시키고, 웨이퍼 중심에서 에칭 중지 위험을 방지하지만, 웨이퍼 주변에서 구멍으로부터의 보호를 감소시키고, 웨이퍼 중심에서 에칭 중지 위험을 방지하지만, 웨이퍼 주변에서 구멍으로부터의 보호를 감소시키다.

좁은 공정 윈도우는 또는 플라즈마에서 중합체 형성 이온과 라디컬을 조절함으로써 만족된다. 이는 중합체 형성 라디컬과 이온이 챔버 시일링 또는 측벽(또는 소기 물품)으로 중합 반응에 의하여 플라즈마로부터 손실 비율 또는 중합체 증착물이 시일링 또는 측벽(또는 소기 물품)으로부터 스퍼터링 비율을 조절함으로써 이루어진다. 시일링에서 중합반응 비율은 중합반응 온도 이상 또는 이하로 시일링 온도를 조정함으로써 이루어진다. 시일링에서 중합반응 비율은 중합반응 온도 이상 또는 이하로 시일링 온도를 조정함으로써 이루어진다. 시일링 위의 상기 중합체 증착물이 에칭되고 플라즈마로 방출되는 비율은 다음 요인에 의하여 영향을 받는바, 즉 시일링 전국에 (직접 또는 간접으로) 인가된 RF 전력, 온도, 챔버 압력, 가스흐름 속도, 유도성 소스 전력 및 다른 파라미터에 의하여 영향을 받는다.

따라서, 좁은 공정 윈도우를 만족하기 위하여, 플라즈마내의 자유 플루오르 및 중합체 형성 이온과 라디컬의 상대 밀도는 챔버 시일링 또는 측벽 또는 소기 물품(만약 있다면)의 온도를 조정함으로써 그리고/또는 오버헤드/시일링 병렬 플레이트 전극에 인가된 RF 전력을 조정함으로써 제어될수 있다.

따라서, 그 실린더형 측벽주위에 유도성 코일이 감긴 병렬 플레이트 플라즈마 반응기는 전체 웨이퍼 표면상의 균일한 접지면으로서 시일링 전국을 제공하는 장점을 가지지만, 챔버 측벽 근처로 이온 발생을 한정하여 플라즈마 처리가 웨이퍼 중심에서는 약하고 웨이퍼 주변에서는 강하게 한다. 오버헤드 평면 코일 플라즈마 반응기는 웨이퍼 표면에 대하여 보다 균일한 RF 유도성 필드를 발생 시키는 장점을 가져 이온 발생이 웨이퍼 주변에 한정되지 않도록 하지만, 웨이퍼 전체에 균일한 접지면이 형성되지 않도록 하여 측벽에 대한 플라즈마 이온 전류 흐름이 플라즈마를 왜곡되게 한다.

#### 발명이 이루고자하는 기술적 과제

본 발명의 목적은 전술한 단점 또는 문제점을 가지지 않고 하나의 반응기에 병렬 플레이트 전극 용량성 결합 플라즈마 반응기의 이점과 오버헤드 평면 유도 안테나를 가진 유도 결합 플라즈마 반 응기의 이점을 결합하는 것이다. 특히, 플라즈마 공정 윈도우를 확장시키도록 전체 웨이퍼 표면 을 균일하게 플라즈마 처리하는 유도 결합 병렬 플레이트 전극 플라즈마 반응기를 제공하여, 예를 들어 챔버압력과 같은 공정 파라미터의 범위를 확장하도록 하는 것이 본 발명의 목적이다.

본 발명의 목적은 플라즈마 이온이 챔버 측벽 근처에서 주도적으로 발생하지 않도록 전체 웨이퍼 표면에 대하여 물리적 배치 및/또는 전력 분배 패턴이 상대적으로 균일한 유도성 코일 안테나를 제공하고, 동시에 챔버 측벽으로의 플라즈마 전류 흐름을 방지하도록 전체 웨이퍼 표면 근처에 균 일한 접지면을 제공하는 것이다. 본 발명의 또 다른 목적은 챔버 측벽과의 상호작용을 최소화하 도록 웨이퍼 표면 상부에 인접하게 플라즈마를 유효하게 한정하는 방식으로 접지면을 이용하는 것 이다.

본 발명의 다른 목적은 챔버벽의 석영 또는 세라믹과 같은 소모성 재료를 제거하거나 또는 감소시켜 상기 재료의 에칭에 의한 챔버벽 근처의 플라즈마 소모 및 비싼 반응기 부품의 소모를 방지하는 것이다.

본 발명의 다른 목적은 균일하게 에칭 가스 및 중합체 전구 가스를 분배함으로써 반응기의 웨이퍼 주변에 대하여 웨이퍼 중심에서의 처리 균일성을 향상시키는 것이다. 특히, 본 발명의 목적은 웨 이퍼 표면사이의 공정 균일성을 최적화하도록 챔버 중심 및/또는 챔버 주변과 같은 챔버의 최적 방사 위치로부터 가스를 유입시키는 것이다. 예를 들어, 에칭율이 웨이퍼 중심에서 낮고, 웨이퍼 주변에서 높은 경우, 가스는 바람직하게 시일링 주변 근처로부터가 아닌 시일링 중심으로부터 유 입된다.

본 발명의 다른 목적은 웨이퍼 주변상의 RF 유도성 필드에 대하여 웨이퍼 중심상의 RF 유도성 필드를 향상시킴으로써(또는 필요하다면, 감소시킴으로써) 반응기에서 웨이퍼 주변에 대하여 웨이퍼 중심에서의 공정 균일성을 향상시키는 것이다. 특히, 본 발명의 목적은 웨이퍼 중심상의 RF 유도성 필드의 세기에 대한 독립적인 제어 및 웨이퍼 주변상의 RF 유도성 필드의 세기에 대한 독립적인 제어 및 웨이퍼 주변상의 RF 유도성 필드의 세기에 대한 독립적인 제어를 제공하여, 웨이퍼 표면 전체에 대한 RF 유도성 필드의 방사방향 분배가 웨이퍼 표면 전체에 대한 플라즈마 공정 균일성을 최적화하도록 조정할 수 있도록 하는 것이다.

반도체 웨이퍼 상에 박막을 선택적으로 에칭하기 위하여 이용된 일반적인 플라즈마 가공 챔버에서, 에칭 및 증착 공정의 결합이 동시에 이용된다. 중합체는 표면 위에 형성되는데, 상기 표면은 충분하게 냉각(중합반응의 온도 임계치 이하)되거나 또는 상기 표면상에서 이온 충돌은 임계 에너지(상기 표면 위에 중합체 증착율을 오프셋하기에 충분한 임계 이온 에너지)이하이다. 상기 온도임계치 및 임계 이온 에너지는 표면 재료에 의존한다. 증착은 웨이퍼 및 공정 챔버 표면상에 발생할 수 있다. 웨이퍼와 공정 챔버 표면상의 증착 제어는 선택적인 에칭 공정을 제어하는데 있어서 중요하다. 반응기 챔버벽의 내부면상의 중합체 증착은 챔버벽 재료가 웨이퍼 상에서 수행되는 공정과 양립할 수 없을 경우 요구된다. 이와 같은 경우의 한 예는 챔버벽이 알루미늄이고 수행될 공정이 실리콘 이산화물의 플라즈마 에칭일 경우이다. 웨이퍼벽 표면상의 중합체 증착은 챔버벽

의 플라즈마 이온 스퍼터링을 방지함으로써 공정으로 알루미늄이 유입되는 것을 방지한다.

중합체 증착을 제어하기 위한 종래 기술에서는 사용자가 다음 두 조건중에서 하나를 선택할 것을 요구한다.

- (1) 표면상에 중합체 증착을 발생시키기 위하여 임계온도이하로 공정 챔버 표면을 유지하거나 또는 임계 이온 에너지이하로 이온 에너지를 유지함;

- (2) 표면상의 중합체 증착을 방지하기 위하여 임계온도이상으로 공정 챔버 표면을 유지하거나 또는 임계 이온 에너지이상으로 이온 에너지를 유지함.

조건(1)의 문제는 표면상에 축적된 중합체는 수동(습식)세정, 플라즈마(건)세정 또는 오염된 부분의 교환에 의하여 주기적으로 제거되어야 한다는 것이다. 그렇지 않으면, 중합체가 파손되어, 챔버를 오염시킬 것이다. 반응 챔버를 세정하는 것은 전체 세정 공정 중에 반응기 동작이 방해를 받는 것을 의미하며, 이는 생산율 감소 및 반응기 동작 비용의 증가를 의미한다. 플라즈마 세정공정과 관련된 문제는 생산율 감소뿐만 아니라 챔버내의 소모 물질의 손실과 오염을 포함한다.

조건(2)과 관련된 문제는 표면이 노출되기 때문에 챔버 표면에 에칭이 발생한다는 것이다. 일반적으로, 이들 표면은 알루미늄 또는 석영이다. 알루미늄 표면에 대하여, 에칭은 오염된 부산물을 생성하고, 이는 전술한 바와 같이 웨이퍼의 플라즈마 처리 품질을 손상시킬 수 있다. 석영 표면에 대하여, 에칭은 높은 속도로 발생할 수 있어, 석영이 주기적으로 교환되어야 하며, 이는 부품비용이 소모되고 제조 시간을 손실하게 한다. 또한, 펌핑 환형부와 같은 챔버상의 다른 부분에서더 차가운 표면으로의 일부 전이가 제공되어야 한다.

따라서, 본 발명의 추가 목적은 반응 챔버 내부를 주기적으로 세정할 필요가 없게 하는 것이다. 본 발명의 다른 목적은 챔버의 공정 영역에서 챔버 표면에 중합체가 모이는 것을 방지하는 것이다. 또한 상기 챔버 표면의 에칭율을 제어하는 것 역시 목적이다. 본 발명의 다른 목적은 공정 영역에 플라즈마를 한정함으로써 챔버의 공정 영역으로부터의 적합한 전이를 제공하는 것이다. 본 발명의 또다른 목적은 펌핑 환형부와 같은 챔버의 공정 영역의 외부 영역에 나머지 중합체 형 성 물질을 모으는 것이다.

#### 발명의 구성 및 작용

웨이퍼와 같은 반도체 제품을 가공하는 플라즈마 반응기는 반구체 또는 돔과 같은 3차원 형상의 오버헤드 시일링을 가진다. 반응기는 또한 시일링 형상과 일치하거나 일치하지 않을 수 있는 유도 안테나를 시일링 위에 포함한다. 시일링은 반도체 재료일 수 있으며, 따라서 안테나의 유도성 필드용 윈도우로서 작용할 수 있으며 마찬가지로 접지 될 수 있거나 또는 RF 전력이 인가되거나전기적으로 분리될 수 있는 전극으로서 동작할 수 있다. 반응기는 웨이퍼 표면 전체에 플라즈마이온 밀도의 방사방향 분배를 허용하는 여러 가지 모양을 가지고 있어 웨이퍼 표면을 균일하게 처리하기 위한 최적의 분배로 조정될 수 있도록 한다. 예를 들어, 오버헤드 코일 안테나는 요구되는 여러 RF 전력 레벨로 구동될 수 있는 별도 보조 대칭 안테나로 분할될 수 있다. 챔버로의 공정 가스 유입구는 여러 가지 방사방향 위치로 배치될 수 있으며 여기서의 가스흐름 속도는 적정 플라즈마 이온 밀도 분배를 얻기 위하여 독립적으로 제어될 수 있다. 시일링 자체는 전기적으로 별도인 방사 대칭 부분으로 분할될 수 있으며, 상기 대칭 부분은 플라즈마 이온 밀도 분배의 적정 조절을 위하여 여러 가지 RF 바이어스 전력 레벨로 구동된다. 동일형태가 아닌 코일 안테나는 시일링 상부면으로부터 멀리 연장하는 나전형 권선을 가진 솔레노이드 형태일 수 있다. 또한, 시일링 온도는 웨이퍼 표면 사이의 플라즈마 가공 균일성을 최적화하기에 적정한 온도 특성에 따라 시일은 오도는 웨이퍼 표면 사이의 플라즈마 가공 균일성을 최적화하기에 적정한 온도 특성에 따라 시외된 여러 방사 구역이 다른 온도로 유지될 수 있도록 제어될 수 있다. 이를 위하여, 다수의 가열 소스(예를 들어, 가열 램프)가 시일링 전체의 여러 방사 위치에 배치되며, 상기 여러 방사위치에서의 가열 소스는 독립적으로 제어된다. 이렇게 하여, 시일링은 여러 가지 환형 온도 제어부로 분할된다. 각각의 그리고 모든 이들 특성은 서로 모두 또는 일부 결합되어 챔버에서 플라즈마 이온 밀도의 방사방향 분배를 조정하기 위하여 플라즈마 반응기의 성능을 향상시킨다.

### 본 발명의 기본 개념

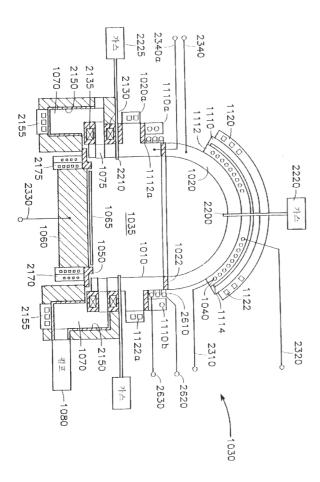

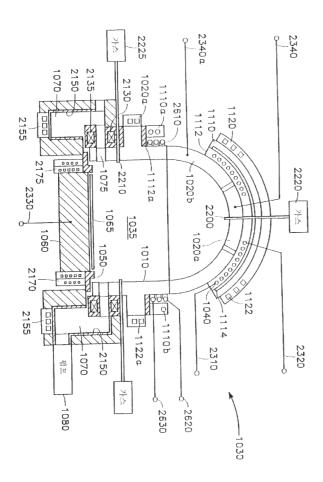

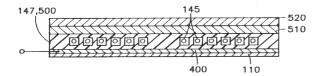

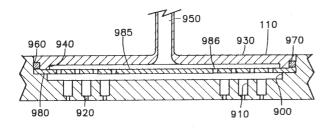

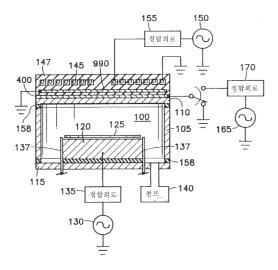

도 1과 관련하여, 플라즈마 반응기는 실린더형 측벽(105), 디스크형 시일링(100) 및 베이스(115)에 의하여 싸여지는 시일된 실린더형 챔버(100)를 포함한다. 웨이퍼 페데스탈(120)은 반응기에 의하여 처리되도록 반도체 웨이퍼 또는 가공품(125)을 지지한다. 웨이퍼 페데스탈(120)은 용량성 장치일 수 있고, 이는 Kenneth S. collins 등에 의하여 1995년 7월 26일 출원되어 출원 계속중인 제08/ , 호인 용량성 가변 밀도 프로파일을 갖는 플라즈마 소스와 같고 본 출원의 양수인에게양도되었고 그 개시된 사항은 여기에서 참조문헌에 의하여 일체화되어 있다. 바이어스 RF 전력 발생기(130)는 선행기술에 의하여 공지된 임피던스 정합회로(135)를 통하여 웨이퍼 페데스탈(120)에바이어스 전위를 가한다. 임피던스 정합회로는 예를 들어 collins 등의 미국특허 제 5,329,018호및 collins 등의 미국특허 제 5,187,454호에 개시되어 있다. 페데스탈(120)에 인접한 가스입구(137)는  $c_xf_x$  가스와 같은 에천트 선구물질 가스와 같은 처리 가스를 수용한다. 절연 안테나홀더(147) 내의 시일링(110) 상에 위치한 오버헤드 유도 안테나(145)는 다른 종래의 임피던스 정합 회로(155)을 통하여 플라즈마 소스 RF 전력 생성기(15)와 연결되고 RF 전력을 시일링(110)을 통하여 챔버로 유도적으로 연결시킨다.

웨이퍼(125)의 전체 표면에 걸쳐 바이어스 RF 전력에 대한 균일한 접지 리턴을 제공하기 위하여 또한 측벽(105)으로의 전류 흐름을 최소화하기 위하여, 시일링(110)은 접지된다. 그러나, 이 성 질은 시일링이 다음과 같은 두 개의 기능을 수행할 것을 요구한다. 즉, (a) 접지될 수 있는 도체 로서의 기능 및 (b) 오버헤드 코일 안테나(145)로부터의 RF 유도 전계가 거기를 통과할 수 있도록 하는 부도체로서의 역할이 그것이다. 이 이중 기능의 역할을 수행하기 위하여, 시일링(110)은 실 리콘과 같은 반도체이다. 실리콘 시일링(110)은 절연체(158)에 의하여 챔버의 도전성 부재로부터 절연된다. 반도체인 실리콘 시일링(110)은 전극 또는 접지면으로써 사용될 수 있는 충분한 전도성이 있는 것을 보인다. 플라즈마 전류가 측벽(105)으로 비스듬히 흐르는 것을 최소화하기 위하여 균일한 오버헤드 접지면을 웨이퍼(125)에 근접하게 위치시키며(예를 들어, 측벽(105)보다 더가까이) 또한 플라즈마를 웨이퍼(125)에 가깝게 수직으로 한정시키기 위하여, 실리콘 시일링(110)은 웨이퍼로부터 웨이퍼 직경보다 더 작게 위치시키며 웨이퍼 직경의 오직 일부만큼의 거리로(예를 들어, 20cm 직경의 웨이퍼에 대하여 수 센티미터로) 위치시키는 것이 바람직하다. 이 거리는 크게는 20 cm, 작게는 1 cm일 수 있고 바람직하게는 2 - 10 cm이다.

시일링(110)은 바람직하게는 실리콘인 반도체 재료의 반도체 윈도우이다. 그러나, 다른 공지된 반도체 재료들이 사용될 수 있는데, 실리콘 카바이드, 게르마늄, 갈륨 아세나이드 또는 인화인듐과 같은 III-V 화합물 반도체, 그리고 수은 카드뮴 텔루르 화합물과 같은 II-III-V 화합물 반도체 등이 그것이다. 실리콘 윈도우 전극의 소요 저항치가 주어진 실내온도에서 필요한 도펀트 불순물 함유량은 Grove, Physics of Semiconductors, p 113의 도 4.14 그래프로부터 얻을 수 있다. 실리콘 윈도우(110)의 온도는 절연체로 되지 아니하는 이상의 그리고 도체로 되지 아니하는 이하의 범위 내에 유지되어야 한다. 소요의 온도 범위는 온도의 함수로써 n-형 실리콘에서의 전극 농도를 보여주는 Grove, Physics of Semiconductors의 도 4.8 그래프로부터 얻을 수 있다. 이 그래프는약 100。K 이하에서 실리콘이 절연체가 되기 시작하고 약 600。K 이상에서 도체가 되기 시작하는 것을 보여준다. 그러므로 실리콘 시일링(110)의 온도를 캐리어 전극 농도가 온도에 대하여 상당히 안정적인 범위로 유지하는 것이 바람직하며, 그것은 약 100。K 및 600。K 사이의 범위이다.

도 1의 플라즈마 반응로를 사용하는 이점 중의 하나는 측벽 둘레에 권선 코일을 가지는 종래의 반 응로 유형에 비하여 오버헤드 코일 안테나(145)에 의하여 전체의 웨이퍼 표면에 걸쳐 생성된 플라 즈마 소스 전력의 균일한 분포이다. 그러므로, 플라즈마 이온 발생은 측벽의 근처에 한정되지 아 니하며 전체의 웨이퍼 표면에 걸쳐 균일하게 분포된다. 플라즈마 이온의 균일성은 증가되는데 이는 접지된 시일링 전국(110)이 측벽(105)으로의 플라즈마 전류의 흐름을 줄이거나 제거하기 때문 이며, 상기에서 언급한 미국 특허 제 4,948,458호에서 개시되었듯이 절연 시일링에 걸쳐 오버헤드 코일 안테나를 가지는 플라즈마 반응기에서의 비스듬히 흐르는 전류와 대비된다. 또한, 웨이퍼와 시일링 사이는 수직적으로 아주 근접하기 때문에 웨이퍼와 플라즈마 이온들이 생성되는 영역 사이 의 거리는 감소하고, 그것에 의하여 재결합 손실을 감소시키고 챔버 압력이 증가되도록 한다(예를 들어, 50 - 200 Torr의 범위로). 이러한 챔버 압력의 증가는 에칭 선택도와 같은 어떤 처리 수행 인자들을 위하여 바람직한 것이다. 챔버 측벽(웨이퍼(125)에 매우 근접한 접지 실리콘 시일링(110)을 가지고 얻어지는)으로의 전류 흐름의 감소와 결합된 (오버헤드 코일 안테나(145)에 의하여 얻어지는) 도 1의 실시예에서의 플라즈마 이온 생성의 균일성은 웨이퍼 중심에서 처리(예, 에칭)할 때 그리고 웨이퍼 주변에서 처리할 때의 차이를 감소시키거나 제거하며, 따라서 처리 윈 도우를 넓힌다. 특히, 웨이퍼 주변을 통하여 오버에치 또는 펀치하는 경향은 감소하는데 동시에 웨이퍼 중심에서의 작은 진폭를 가지는 경우의 에치 스톱 경향도 감소한다. 또한, 웨이퍼 주변에서 포토레지스트 마스크 에지의 면을 만드는 경향 및 일반적으로 불량한 에치 프로파일을 야기하는 포토레지스트를 에치하는 경향은 감소되거나 제거된다. 따라서, 도 1의 플라즈마 반응로는 매 우 작은 규모의 진폭에서 마이크로로딩을 매우 적게 또는 전혀 가지지 아니하고 좋은 에치 선택성 및 좋은 에치 프로파일을 가지고 전체 웨이퍼 표면에 대한 적극적인 에치 성능을 제공한다. 측벽(105)의 개입이 전혀 없거나 아주 적으므로, 반응로 부품의 소비 및 관련 동작 비용은 현격히 감소한다. 따라서, 본 발명은 관련 분야에서 혁신적인 진보를 하게 된 것이다.

그러나, 잠재적인 문제점들이 잔존하고 있어서, 이들이 해결되지 아니하면 도 1의 반응로가 실용적이지 못하게 한다. 우선, 실리콘 시일링(110)이 오버혜드 코일 안테나(145)의 RF 유도 전계가 챔버(110)에 접근하는 것을 차단할 것인지에 관한 문제이다. 예를 들어, RF 유도 전계에 대한 실리콘 시일링(110)의 임피던스는 너무 진폭 때문에 거기를 통하여 전송하게 하는 것은 불가능하다. 이것은 실리콘 시일링(110)에서 도펀트 불순물 농도에 의하여 또는 실리콘 시일링(110)의 온도에 의하여 영향을 받을 수 있다. 대안적으로, 실리콘 시일링(110)에 대한 RF 유도 전계 표피 깊이는 시일링 두께를 초과하지 않을 수 있고, 따라서 거기를 통하여 전송하는 것을 방지할 수 있다. 또한, 챔버(100) 내의 플라즈마를 통과하는 RF 유도 전계 표피 깊이는 시일링 두께는 챔버 높이(즉,웨이퍼-상부 전극 캡) 보다 클 수 있어서, RF 유도 전력은 플라즈마에 효율적으로 결합되지 않을 수 있다. 또 다른 문제는 시일링(110)이 웨이퍼(125)에 매우 가깝기 때문에 시일링(110) 근처의 플라즈마 외장을 웨이퍼(125) 바로 밑 부근의 플라즈마 외장으로부터 분리시키기, 따라서 플라즈마를 상부로부터 하부까지 분류하기에 불충분할 수 있다. 또한, 시일링(110)의 실리콘 재료를 바이어스 RF 전력 발생기(130)의 RF 리턴 경로에 삽입하는 것은 심각한 RF 바이어스 전력 손실을 야기할 수 있다. 마지막으로, RF 유도 전계가 과도한 손실 또는 감쇠없이 결합될 수 있는 범위 내의 반도체 윈도우에 대한 저항치의 적절한 또는 실용적인 범위가 존재하지 않을 수 있다. 이 문제들은 바로 아래에서 설명되는 것에 의하여 해결되거나 처치된다.

<u>유도 전계의 플라즈마에 대한 표피 깊이는 전력이 플라즈마에 효율적으로 흡수되도록 충분히 짧</u>다.

오버헤드 코일 안테나(145)로부터의 RF 유도 전계의 표피 깊이는 시일링에서 웨이퍼까지의 높이보다 작기 때문에(예를 들어,웨이퍼 직경만큼 또는 그 이하),코일 안테나(145)로부터의 전력은 플라즈마와 효율적으로 유도성 결합을 한다.이것은 두 가지의 경우에서 볼 수 있는데,즉,플라즈마 소스 RF 각주파수가 플라즈마 운동량 전송 비탄성충돌 주파수보다 훨씬 적은 충돌 표피 깊이,그리고 플라즈마 소스 RF 각주파수가 플라즈마 운동량 전송 비탄성충돌 주파수보다 훨씬 큰충돌없는 표피 깊이가 그것이다.

플라즈마에 대한 RF 유도 전계의 충돌 표피 깊이 δc는 다음 식에 의하여 계산된다.

여기에서,  $\gamma_m = 1.4 * 10^7 \ sec^{-1}$ 은 온도 300。K 그리고 챔버 압력 5mTorr에서 아르곤 플라즈마에 대한 중성 전자 운동량 전송 충돌 주파수이고,  $\omega = 12.57 * 10^7 \ radians/sec$ 는 코일 안테나에 가해진 유도 전계 RF 전력 소스의 각주파수이고,  $c = 3 * 10^8 \ meters/sec$ 는 광속이고,  $e = 1.6022 * 10^{-19} \ coulomb$ 는 전자 전하이고,  $n_e = 5 * 10^{17} \ meters^{-3}$ 은 적용 가능한 전자밀도이고,  $\epsilon_0 = 8.85 * 10^{-12} \ farads/meter$ 는 자유공간의 전기적 유전율이며,  $m_e = 9.1095 * 10^{-31} \ kg$ 은 전자질량이다.

앞의 값들을 수학식 1에 대입하면 충돌 표피 깊이에 대하여 다음을 얻는다.

$$\delta_c = 1.1 \ cm$$

RF 유도 전계의 플라즈마에 대한 충돌없는 표피 깊이 δ,는 다음에 식에 의하여 계산된다.

$$\delta_n = c[(e^2 n_e)/(\epsilon_0 m_e)]^{-1/2}$$

앞의 값들을 수학식 3에 대입하면 충돌없는 표피 깊이에 대하여 다음을 얻는다.

$$\delta_n = 0.8$$

cm

따라서, 어떠한 경우에서나 RF 유도 전계의 표피 깊이는 웨이퍼-시일링 높이보다 훨씬 작으며, 이는 RF 소스 전력이 플라즈마에 의하여 충분히 흡수되도록 한다.

<u>유도 전계의 실리콘 시일링에 대한 표피 깊이는 시일링을 통하여 확장할 수 있도록 시일링 두께보</u>다 더 크다.

코일 안테나 (145)의 RF 유도 전계는 실리콘 시일링의 1 인치 두께(2.54 cm)를 훨씬 초과한다. 그러므로, 만약 저항손실이 충분히 작다면, RF 유도 전계는 실리콘 시일링(110)을 관통할 수 있을 만큼 충분히 깊다. 이것은 무한 평면 실리콘 슬랩(slab) 상에 입사하는 균일 평면파의 표피 깊이  $\delta$ 를 계산함으로써 근사하게 계산될 수 있다.

$$\delta = [\pi f \sigma \mu]^{-1/2}$$

상기에서 기호는 다음과 같다.

f = 2 MHz는 코일 안테나(145)에 연결된 RF 전력 소스 (130)의 주파수이다.

$\mu = 4\pi * 10^{-7}$  Henries/meter는 실리콘 슬랩의 자기 투자율이다.

$\sigma$  = 3.33  $\Omega$ -1meters-1은 30  $\Omega$ -cm 고유저항을 가지는 실리콘 슬랩의 컨덕턴스이다.

상기의 값을 상기 식에 대입하면 다음의 값이 얻어진다.

$\delta = 0.195 \text{ m}$

그래서 표피 깊이는 실리콘 시일링(110) 두께의 약 여덟 배이며 따라서 RF 유도 전계는, 만약 실리콘 시일링(110)이 RF 유도 전계에 대하여 고임피던스를 취하지 않는다면, 챔버(10)로 좋은 관통 깊이를 가진다.

<u>실리콘 시일링은 RF 유도 전계에 대하여 저임피던스를 취한다.</u>

13.5 인치 직경 및 1인치의 두께를 측정하는 실내온도에서 30 Ω-cm 고유저항의 원반형 실리콘 슬랩으로 구성된 실리콘 시일링(110)의 실시예를 통한 RF 유도 전계의 전도는 유도 코일을 슬랩의반대쪽에 위치시키고, 슬랩 한 쪽의 코일을 가변 주파수 RF 소스에 대하여 연결하고, 그리고 다른쪽의 코일을 복수채널 분석기에 연결하며 그리고 RF 소스의 주파수를 1 kHz로부터 10 MHz까지 소인함으로써 실내온도에서 테스트된다. 복수 채널 분석기의 결과 출력은 도 2에 도시되어 있다. 진폭라고 이름 붙여진 곡선에 대하여, 수직축은 수신 및 전송 신호의 진폭비이며 스케일의 상부에서의 1에서 0.1씩 떨어지며, 수평축은 주파수이며 좌측 1 kHz에서 우측 10 MHz로 확장한다. 위상이라고 이름 붙여진 곡선에 대하여는, 수신과 전송 신호 사이의 차이이며 스케일의 상부에서의 0°로부터 연장되고 20°씩 떨어진다. 도 2의 그래프는 실리콘 슬랩을 통하여 RF 전력이 실질적으로 2MHz 까지는 손실이 없으며 2MHz 이상에서는 상대적으로 아주 적은 양의 손실이 있다는 것을 명백히 보여준다.

도 2가 실린더형의 실리콘 슬랩을 가지고 얻어진 결과를 나타내고 있다면, 도 3은 12.3 인치의 외경 및 1 cm의 두께를 가지는 실린더형 실리콘 슬랩을 가지고 실내온도에서 얻어진 결과를 보여준다. 5회 감은 전송 코일은 RF 전력을 실린더형 실리콘 슬랩에 의하여 둘러싸여진 내부 체적 안으로 전송하기 위하여 실린더형 슬랩의 외측에 감겨있다. 측정은 2.3 인치의 외경 및 3 인치 길이를가지는 8회 감은 수신기 코일로부터 내부 체적의 중간에서 취해진다. 진폭라고 이름 붙여진 곡선에 대하여, 수직축은 수신 및 전송 신호의 진폭비이며 스케일의 상부에서의 1에서 0.1씩 떨어지며, 수평축은 주파수이며 좌측 1 kHz에서 우측 10 MHz로 확장한다. 위상이라고 이름 붙여진 곡선에 대하여는, 수직축은 수신과 전송 신호 사이의 차이이며 스케일의 상부에서의 0°로부터 연장되고 20°씩 떨어진다. 도 2의 그래프는 2 써 이상으로 실리콘 슬랩을 통한 RF 전력의 손실이 실질적으로 없고 2 써 이상의 비교적 작은 손실이 있는 것을 가리킨다. 그래서, 실리콘 시일링(110)

은 RF 유도 필드에 거의 투명하다.

### 실리콘 시일링은 넓은 온도 범위상에서 RF 유도 필드에 낮은 임피던스를 가진다.

도 2 및 도 3을 참조하여 상기된 검사는 200° 및 250°의 실리콘 온도에서 반복되고 유사한 결과가 얻어지며, 실리콘 시일링(110)의 온도가 중합반응을 조절하기 위하여 넓은 범위상에 변화되고질소 배기 처리가 목표되는 것을 나타낸다. 그러나, 300℃ 이상의 온도에서, 실리콘 시일링(110)은 본질적이되고 그러므로 오버헤드 코일 안테나(145)의 RF 유도 필드가 챔버(100)에 도달하는 것을 막는다. 시일링(110)에서 높은 저항 실리콘(예를들어, 실온에서 30 Ω-㎝)을 사용하는 것이바람직하다. 그렇지 않다면, 예를들어 시일링(110)에 0.01 Ω-㎝ 저항 실리콘을 사용하는 것은실리콘 시일링을 통하여 결합하기 위하여 灺 범위 및 그 이하로 RF 유도 필드 주파수를 줄이는 것을 요구한다. 다른 선택 사항은 시일링 두께를 줄이는 것이다.

# 실리콘 시일링은 바이어스 RF 전력원의 리턴 경로의 손실이 없다.

바이어스 전력 발생기(130)에 대한 RF 리턴 경로에 실리콘 시일링(110)을 삽입함으로써 야기된 RF 전력 손실은 슬랩 두께보다 큰 표피 깊이 및 실리콘 슬랩의 후면상 완전한 전도체 그라운드 평면의 존재를 가정하여 편평한 슬랩 표면에 수직인 전류 플럭스에 대한 실리콘 슬랩의 저항을 계산함으로써 도시될 수 있다. 이런 저항은 웨이퍼 페데스탈(120)에서 측정된 구동 포인트 RF 임피던스보다 매우 작게도시되어, 실리콘 시일링의 삽입은 전체 바이어스 RF 전력 손실의 부분 증가만을 유도한다.

표면에 수직인 전류 플럭스에 대한 실리콘 슬랩의 저항(R<sub>slab</sub>)은 아래와 같이계산된다:

$$R_{slab} = t(d/2)^{-2}/$$

여기서, t = 0.0254 m은 슬랩 두께,

d = 0.318 m은 전류 플럭스에 노출된 효과적인 슬랩 직경,

$\Gamma$  = 0.30  $\Omega$ -m는 실온에서 30  $\Omega$ -cm 저항 실리콘의 저항이다.

선행값을 R<sub>slab</sub>에 대한 방정식에 대체한 것은 슬랩에 대한 저항을 생성한다:

$R_{slab} = 0.096 \Omega$ .

웨이퍼 페데스탈(120)에서 구동 포인트 임피던스(Z)는 50.1°의 각에서 38.7Ω으로서 도 1(코일 안테나로부터 2.0 № 플라즈마 전력 소스 RF 유도 필드 및 1.8 №의 페데스탈상에 인가된 RF 바이 어스)에 도시된 형태의 통상적인 병렬 전극 플라즈마 반응로에서 측정된다. 이런 구동 포인트 임 피던스의 실수 부분은 아래와 같다.

Re(Z) = 38.7 Ω cos(50.1°(180/ $\pi$ ))  $\approx$  24 Ω.

실리콘 시일링의 삽입에 의해 유발된 RF 전력 손실의 부분 증가는 아래와 같다.

$R_{slab}/Re(z) = 0.096/24 = 0.004,$

이것은 매우 작은 부분이다. 그래서, RF 바이어스 전력 발생기(130)의 RF 리턴 경로에 실리콘 슬랩의 삽입은 무시할 수 있는 저항양만을 첨가한다.

# 플라즈마 DC 외장 두께는 시일링 및 웨이퍼 사이의 단락을 피하기 위하기 위하여 충분히 짧다.

플라즈마 이온 밀도 값으로부터 영으로 이온 밀도를 떨어뜨리는 플라즈마 가장자리 외장이 있다. 만약 웨이퍼 표면에서의 외장이 챔버 시일링 외장과 일치하지 않으면, 챔버에 플라즈마가 없다. 고전압 플라즈마 DC 외장 두께(S)는 다음과 같이 계산된다:

$$S=(2^{1/2}/3)[(_{O}T_{e})/(en_{e})]^{1/2}(2V_{0}/T_{e})^{3/4}$$

여기서, <sub>0</sub>=8.8510<sup>-14</sup> 패러드/cm는 자유 공간의 전기 투과율,

$T_e^{=5eV}$ 는 맥스웰 분포를 가정하는 평균 전자 온도,

e=1.602210<sup>-19</sup>는 전자 전하,

$n_e = 510^{11} cm^{-3}$ 은 외장에 인접한 벌크 플라즈마의 평균 전자 밀도, 및

$\overline{V}_0$  = 300 볼트는 플라즈마 외장을 가로지르는 DC 전압이다.

선행값을 S에 대한 방정식에 대입하는 것은 아래와 같다:

S = 0.04 cm,

그러므로 플라즈마 외장 두께는 웨이퍼 대 시일링 거리의 작은 부분만이고 상부 및 하부 외장이 교차하지 않는다.

RF 전력이 낮은 감쇠 손실과 결합되는 반도체 윈도우 전극에 대한 넓은 범위의 저항값이 있다.

유도 RF 필드가 낮은 감쇠 손실로 결합되거나 전송될 반도체 윈도의 저항 값 범위를 확실히 하기 위하여. RF 유도 필드의 주파수는 선택되고 RF 표피 깊이 대 윈도우 두께의 최소 비율(r)은 지정

되어야 한다. 제 1 실시예에서, 윈도우 두께는 T = 0.0254 미터이고, RF 주파수(f)는  $210^6 S^{-1}$  이고 RF 표피 깊이 대 윈도우 두께의 최소 비율은 r = 5이다. 이런 제 1 실싱예에 대하여, 반도체윈도우에 대한 최소 저항은 다음과 같이 계산된다:

$=410^{-7}$  헨리/미터는 반도체 윈도우의 자기 투과율이고, S = r·T는 반도체 윈도우에서 RF 유도 필드의 표피 깊이이다. 최소 저항( $_{\min}$ )은 다음 방정식에 의해 계산된다:

$_{min}=S^2\pi f \mu$

상기 주어진 값을 이 방정식에 대입하면, 상기 제 1 실시예에 대한 최소 저항은  $_{\min}$  = 12.735  $\Omega$ -cm이다.

다음, 최대 저항은 이 제 1 실시예에 대하여 계산되어야 한다. 다음 분석을 위하여, 반도체 윈도우 후방 RF 유도 필드로 투과하는 그라운드 평면이 있다는 것이 가정된다. RF 바이어스 플라즈마로드 임피던스의 실제 부분이 형성되고, 허용가능한 손실(L)은 한정되고 반도체 윈도우의 효과적인 플라즈마 상호작용 직경은 형성되어야 한다. 이런 제 1 실시예에서, RF 바이어스 플라즈마 이 피던스의 실제 부분(R)은 R =  $25\Omega$ 이고, 허용 가능한 손실(100% = 1에서 표준화된)은 L = 0.010다. 반도체 윈도우의 효과적인

플라즈마 상호작용 영역(a)이  $A=\pi(d/2)^2$ 로서 계산된다.

최대 저항(max)은 다음 방정식에 의해 주어진다:

$_{\text{max}} = L \cdot R \cdot a/T$ .

선행값을 이 방정식에 대입하면: max = 78.172 Ω-cm이다.

그러므로, 이 제 1 실시예에서, 반도체 저항은 12.735  $\Omega$ -cm 및 78.172  $\Omega$ -cm 사이의 임의의 범위 내에 놓인다.

제 2 실시예에서, 반도체 윈도우 두께는 T = 0.00254 미터이도록 10 인자만큼 감소된다. 이런 경우에,  $\Gamma_{\min}$ 은  $\Gamma_{\max}$ 가 781.719  $\Omega$ -cm로 증가하는 동안, 0.127  $\Omega$ -cm로 감소된다.

제 3 실시예에서, 제 2 실시예의 파라미터는 RF 유도 필드의 주파수가  $100 \text{ kb}(f=0.1 \cdot 10^5 \text{ s}^{-1})$ 로 감소되는 것을 제외하고 반복된다. 이런 경우,  $\Gamma_{\text{max}}$ 가  $781.719\Omega$ -cm로 감소되는 동안,  $\Gamma_{\text{min}}$ 은  $63.675 \Omega$ -cm로 증가되어, 다른 실시예와 관련하여 범위를 다소 좁게한다.

그래서, 저항 값의 유용한 범위는 넓다. 만약 반도체 윈도우가  $2.54\Omega$ -cm 두께 실리콘 슬랩이고 유도 필드의 RF 주파수가 2~Mid이며, 바람직한 저항은  $30\Omega$ -cm이다.

### 본 발명의 다른 바람직한 실시예

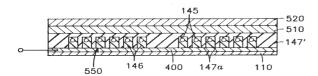

실리콘 시일링(110)이 도 1의 바람직한 실시예에서 접지되는 동안, 도 4의 실시예에서 RF발생기(130)으로부터의 전력은 페데스탈(120) 및 실리콘 시일링(110) 사이의 전력 스플리터(110)에 의해 분할된다. 그라운드 리턴 경로를 제공하기 위하여, 촉벽(105)은 그라운드 전도체이다.도 5에서, 실리콘 시일링(110)은 종래 임피던스 매칭 회로(170)를 통하여 각각의 RF 전력발생기(165)에 의해 웨이퍼 페데스탈(120)로부터 독립적으로 구동된다. 도 1의 실시예가 인덕터안테나(145)로서 단일 코일을 사용하는 동안, 도 6의 실시예에서, 인덕터안테나(145)는 다수의(이런 경우, 2개) 독립적 구동 코일, 즉 웨이퍼 주변에 놓여있는 웨이퍼 중앙 및 외부 코일(180)에놓인 내부 코일로 구성된다. 도 6의 실시예에서, 내부 및 외부 코일(175, 180)은 플라즈마 소스전력발생기(185, 190)에 의해 구동되는 2차원 동심 코일이다. 캠버(100)의 반경을 따르는 플라즈마 변화가 2개의 RF 발생기(185, 190)로부터 다른 전력 레벨을 선택함으로써 보상될 수 있다는 장점이 있다. 도 6 실시예의 원형에서, 내부 및 외부 코일은 9회전 감겨진다. 고정된 임피던스매칭은 내부 코일(175)의 각각 입력 및 리턴 단부에 접속된 병렬 및 직렬 캐패시터(195, 200)와외부 코일(180)의 각각 입력 및 리턴 단부에 접속된 병렬 및 직렬 캐패시터(205, 210)를 사용하여실현된다. 작업 실시예에서, 플라즈마 소스 RF 전력 발생기(155)는 2.0 № 세서 2600 와트를 생성하고, c₂f6 가스는 100 cc의 아르곤이 30 sccm의 비율로 캠버(100)에 펌핑되고, 캠버 압력은 6.5 ™ 주 전체 용지되고 실리콘 시일링(110)의 온도는 200°C에서 유지되고, 캠버 압력은 6.5 ™ 주 제외 및 직렬 캐패시터(195, 200)는 외부 코일(180)의 병렬 및 직렬 캐패시터(205, 210)가 4.45572 나노패러드 및 1.09085 나노패러드의 캐패시턴스를 가지는 동안 각각 8.19699 나노패러드 및 2.12631 나노패러드의 캐패시턴스를 가진다. 내부 및 외부 코일(175, 180)중 하나를단락함으로써, 다른 입력 임피던스가 측정된다. 선행 캐패시턴스가 측정되고나서, 내부코일(175)의 복합 임피던스는 -8.6°의 복합 평면 각에서 5.18요으로서 측정되고 외부 코일(180)의 복합 임피던스는 -8.6°의 복합 평면 각에서 5.18요으로서 측정되고. 그래서, 임피던스는 RF발생기(185 및 190)의 표준 50요 출력과 거의 매칭된다.

도 7의 실시예에서, 측벽(105)은 실리콘 측벽(215)에 의해 대체되고 유도 결합은 실리콘 측벽(215)의 외부 주위에 감겨진 코일 인덕터(220)에 의해 제공되고 임피던스 매칭 회로(155´)를 통하여 플라즈마 소스 전력 발생기(150´)에 접속된다. 도 4의 실시예에서 처럼, 도 8은 전력 스 플리터(160)가 페데스탈(120) 및 실리콘 측벽(215) 사이 바이어스 발생기(130)로부터 RF 전력을 분할할 수 있는 것을 도시한다. 도 5의 실시예에서 처럼, 도 9는 실리콘 측벽(215)이 어떻게 매칭 회로(170)를 통하여 분리된 RF 발생기(165)에 의해 독립적으로 전력이 인가될 수 있는 가를 도시한다. 도 10은 도 1의 실리콘 시일링(110) 및 오버헤드 코일 안테나(145)가 어떻게 도 7의 실리콘 측벽(215) 및 측면 코일 안테나(220)과 결합될 수 있는 가를 도시한다. 도 11은 도 8의 전력 스플리터(160)가 어떻게 측벽(215) 및 페데스탈(120) 사이의 바이어스 발생기(130)로부터 전력을 분할하기 위하여 도 10의 실시예에서 사용될 수 있는 가를 도시한다. 도 12는 도 1의 오버헤드 코일 안테나(145) 및 실리콘 시일링(110)을 가지는 도 9의 실시예의 결합을 도시한다.

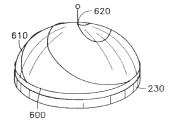

도 13a, 13b, 13c 및 13d는 각각 도 1, 4, 5 및 6 실시예의 변형을 도시하는데, 여기에서 편평한 실리콘 시일링(110) 및 편평한 유도 코일 안테나(145)는 각각 돔 모양 실리콘 시일링(230) 및 돔 모양 코일 안테나(235)에 의해 데체된다. 일실시예에서, 돔 모양 코일 안테나(235)는 나선형으로 감겨진다. 도 14는 돔 모양 코일 안테나(235)가 돔 모양 시일링(230)의 상부 근처로부터 연장하고 측벽(105) 주위르 감기 위하여 돔 모양 시일링(230)의 하부를 통과하는 것을 도시한다. 이런 경우에, 코일 안테나(235)의 하부에 의해 둘러싸진 측벽(105)의 적어도 일부는 실리콘같은 석영 또는 반도체로 비전도체이다. 도 15는 납작한 실리콘 시일링(110) 및 납작한 코일 안테나(145)가도 13a의 돔 모양 실리콘 시일링(230) 및 돔 모양 코일 안테나(235)에 의해 대치되는 도 10과 대응하는 실시예를 도시한다.

도 16은 전력 스플리터(250)가 어떻게 도 6의 실리콘 시일링(110)에 놓여잇는 내부 및 외부 코일 안테나(175) 사이 플라즈마 소스 RF 전력 발생기(150)로부터 전력을 분할하기 위하여 사용되는 가를 도시한다. RF 전력 스플리터는 콜린즈등에 의해 미국특허 제 5,349,313 호에 개시된다. 상기에서 참조된 특허 출원인 공동 계류중인 콜린즈등에 의해 개시된 바와같이, 제어기(260)는 웨이퍼중심상의 플라즈마 이온 밀도 및 웨이퍼 주변상의 플라즈마 이온 밀도 사이의 어떤 차이를 보상하기 위하여 내부 및 외부 코일 안테나(175, 180) 사이 전력 비율을 변화시킬 수 있다. 도 17a는 전력 스플리터(250)가 측면 코일(220) 및 돔 모양 오버헤드 코일(235) 사이의 플라즈마 소스 전력발생기(150)로부터 RF 전력을 분할하는 도 15와 같은 실시예를 도시한다. 도 17b는 내부(상부)돔 모양 코일(270) 및 외부(하부)돔 모양 코일(280)을 가지는 돔 모양 실리콘 시일링(230)을 가지는 실시예를 도시한다. 전력 스플리터(250)는 내부 및 외부 돔 모양 코일(270, 280) 사이의 플라즈마 소스 전력 발생기(150)로부터 RF 전력을 분할한다. 도 17b의 실리콘 시일링(230) 및 웨이퍼 페데스탈(120)은 도 13a, 도 13b 또는 도 13c 실시예중 임의의 하나에 따라 접속될 수 있다.도 18은 전력 스플리터(250)가 어떻게 도 10의 오버헤드 코일 안테나(145) 및 측면 코일안테나(220) 사이의 플라즈마 소스 RF 전력 발생기(150)으로부터 전력을 분할수있는가를 도시한다.

도 19는 전력 스플리터(250)가 어떻게 오버헤드 코일 안테나(145) 및 실리콘 시일링(110) 사이의 플라즈마 소스 RF 발생기(150)로부터 전력을 분할할수있는가를 도시한다. 도 19의 실시예에서, 웨이퍼 페데스탈(120)은 임피던스 매칭 호로(135)를 통하여 바이어스 RF 전력 발생기(130)에 접지되거나 접속될 수 있다. 도 20은 전력 스플리터(250)가 어떻게 오버헤드 코일 안테나(145) 및 웨이퍼 페데스탈(120) 사이의 RF 발생기(150)로부터 전력을 분할할수있는가를 도시한다. 도 20의실시예에서, 실리콘 시일링(110)은 매칭 회로(170)를 통하여 각각의 RF 전력 발생기(165)에 접지되거나 접속될 수 있다. 도 21은 도 19에 대응하는 실시예이지만 도 19의 편평한 실리콘시일링(110) 및 편평한 코일 안테나(145) 대신에 돔 모양 실리콘 시일링(230) 및 돔 모양 코일 안테나(235)를 사용한다. 도 22는 도 20에 대응하는 실시예지만 도 20의 편평한 실리콘시일링(110) 및 편평한 코일 안테나(145) 대신에 돔 모양 실리콘 시일링(230) 및 돔 모양 코일 안테나(235)를 사용한다.

도 23은 실리콘 시일링(110) 및 웨이퍼 페데스탈(120)이 서로에 대한 RF 접지 리턴인 실시예를 도 시일링 및 페데스탈(110, 120)은 각각의 RF 절연 필터(310, 315)ff 통하여 각각의 RF 주 파수 $(f_1$  및  $f_2$ )의 각각의 독립적인 RF 전력 발생기(300, 305)에 의해 각각의 임피던스 매칭 회로(280, 290)를 통하여 구동되고 각각의 그라운드 RF 필터(320, 325)를 통하여 접지하기 위하여 각각 접속된다. 절연 필터(310, 315)는 RF 전력 발생기(300, 305)중 어느 하나로부터의 RF 에너 지가 서로에게 도달하는 것을 막는다. 그라운드 RF 필터(320, 325)는 시일링 및 페데스탈(110, 120)중 각각 하나가 서로에 의해 챔버(100)를 가로질러 방사된 RF 전력을 접지하도록 리턴되게한 동시에, 그라운드 RF 필터(320, 325)는 시일링 및 페데스탈(110, 120)중 어느 하나에 인가된 RF 전력이 직접적으로 접하도록 단락되지 않게한다. 특히, 실리콘 시일링(110) 및 주파수(f<sub>1</sub>)의 RF 전력 발생기(300) 사이에 접속된 절연 필터(310)는 주파수 $(f_1)$ 에서 RF 전력을 통과시키고 주파 수(f<sub>2</sub>)에서 RF 전력을 막는다. 웨이퍼 페데스탈(120) 및 주파수(f2)의 RF 전력 발생기(305) 사이 에 접속된 절연 필터(315)는 주파수 $(f_2)$ 에서 RF 전력을 통과시키고 주파수 $(f_1)$ 에서 RF 전력을 막는 실리콘 시일링(110) 및 그라운드 사이에 접속된 그라운드 필터(320)는 주파수(f₂)에서 RF 전 력을 통과시키고 주파수 $(\mathfrak{f}_1)$ 에서 RF 전력을 막는다. 웨이퍼 페데스탈(120) 및 그라운드 사이에 접 속된 그라운드 필터(325)는 주파수 $(f_1)$ 에서 RF 전력을 통과시키고 주파수 $(f_2)$ 에서 RF 전력을 막는

임피던스 매칭 회로(280, 290)는 여기에서 이미 논의된 종래 형태이고 실제 입력 이피던슬르 측정하기 위하여 종래 방식으로 전압 및 전류 센서 또는 임피던스 매칭 트랜듀서(도시되지 않음)를 사용한다. 두 개의 RF 발생기(300, 305)중 어느 하나로부터의 RF 전력이 다른 임피던스 매칭 회로의 동작과 간섭하지 않도록 하기 위하여, 각각의 매칭 절연 필터(330, 335)는 임피던스 매칭 트랜듀서 및 임피던스 매칭 회로(280 290)에 대한 트랜듀서 입력부 사이에 접속된다.  $f_1$  매칭 회로(280)에 대한 입력에서 매칭 절연 필터(330)는 주파수( $f_1$ )에서 RF 전력을 통과시키고 주파수( $f_2$ )에서 RF 전력을 막는다.  $f_2$  매칭 회로(290)에 대한 입력에서 매칭 절연 필터(335)는 주

파수(f<sub>2</sub>)에서 RF 전력을 통과시키고 주파수(f<sub>1</sub>)에서 RF 전력을 막는다.

다양한 RF 필터(310, 315, 320, 325, 330, 335)는 종래 기술을 사용하여 양의 반응 구성요소(캐패시터 및 인덕터)로 구성된다. 만약 두 개의 주파수( $f_1$ ,  $f_2$ )가 폭넓게 분리되면(예를들어, 옥타브에 의해), 다양한 RF 필터(310, 315, 320, 325, 330, 335)는 적당하게 선택된 컷 오프 주파수를 가지는 적당한 하이 패스 필터 및 로우 패스 필터일 수 있다. 그렇지 않다면, 만약 두 개의 주파수( $f_1$ ,  $f_2$ )가 충분히 분리되지 않으면, 다양한 RF 필터(310, 315, 320, 325, 330, 335)는 적당한 주파수에 집중된 대역 여파기 또는 대역 반사기이어야 한다.

도 24는 도 23과 대응하는 실시예를 도시하지만, 도 23의 편평한 실리콘 시일링(110) 및 편평한 코일 안테나(145) 대신 도 13a의 돔 모양 실리콘 시일링(230) 및 돔 모양 코일 안테나(235)를 사용한다.

도 25a는 실리콘 시일링(110)의 상부측 또는 후면측 표면상에 전도 후면(400)의 사용을 도시한다. 실리콘 시일링(110)에 인가될 전위(예를들어, 그라운드 또는 선택적으로 RF 발생기의 출력)는 시일링(110)의 후면 표면을 가로질러 균일한 분포에 대한 전도 후면(400)에 직접적으로 인가된다. 후면(400)은 예를들얼 알루미늄 또는 구리같은 어떤 높은 전도 재료이다. 더욱이, 후면(400)은 후면(400)을 통하여 RF 유도 필드의 전송을 막는 오버헤드 코일 안테나(145)의 유도 RF 필드에 의해 역류 전류의 형성을 방지하기 위하여 충분한 개구부 또는 구명을 가져야 한다. 예를들어, 도 25b의 평면도는 전도 후면(400)이 별 모양이다는 것을 도시하고, 다수의 전도 아암(405)은 전도 중심부(410)로부터 방사적으로 연장한다. 바람직하게, 전도 아암(405) 사이의 공간 또는 구멍(415)은 실리콘 시일링(110)의 두께 정도의 특정 넓이이다. 이런 특징은 실리콘 시일링(110)을 통하여 균일한 전류 분배 및 수직 전류 흐름을 제공한다. 도 25b의 실시예의 중앙 접속 아암은 각각의 제조동안 세라믹상에 적층된 실리콘의 경우 바람직하다. 도 25c는 전도 고리(420)로부터 가공의 중심점(430)으로 방사적으로 안쪽으로 연장하는 다수의 전도 아암(425)을 가지는 외부전도 고리(420)로 구성된 전도 후면(400)의 다른 실시예를 도시한다. 전도 아암(425) 사이의 구 멍은 도 25c에 도시된 바와같이 실리콘 시일링(110)의 두께 정도 특성 넓이다. 바람직하게, 전기접촉부는 전체 고리(420)를 따라 이루어진다. 바람직하게, 외부 전도 고리(420)는 RF 유도 필드의 효과적인 방사 범위 이상이다.

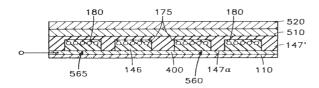

바람직하게, 실리콘 시일링은 구조적 안정성 및 10 초과시 반내파 안정성 인자를 제공하기 위하여 13 인치(32 cm) 직경 시일링에 대해 약 1 인치(2.54 cm) 두께이다. 그러나, 실리콘 시일링의 두께(예를들어, 인치에 대한 분수)를 상당히 감소시키기 위하여, 도 26은 실리콘 시일링(110) 및 그것의 후면(400)이 어떻게 세라믹 디스크 같은 강한 기판 지지 기판(500)에 접착될수 있는가를 도시한다. 오버헤드 유도 코일 안테나 홀더(147)는 기판(500)상에 배치된다. 실리콘 시일링(110)의 온도를 제어하기 위하여, 가열기 층(510)은 안테나 홀더(147)의 상부에 배치되고 냉각 플레이트(520)는 가열기 층(510)의 상부에 배치된다. 도 27은 기판(500)의 역할 및 안테나 홀더(147)의 역할이 안테나 홀더(147)의 세라믹같은 강한 재료를 사용하고 안테나 홀더(147)에 직접적으로 전도 후면(400)을 가지는 실리콘 시일링(110)을 접착함으로써 단일 부재로 통합된다.

도 28은 알루미늄 또는 구리같은 전도체로 구성된 다른 안테나 홀더(147´)를 사용하는 본 발명의실시예를 도시한다. 이런 실시예에서, 절연 재료(146)는 전도 코일 안테나(145) 및 전도 안테나홀더(147´)의 권선 사이에 제공된다. 전도 안테나홀더(147´)가 코일 안테나(145)의 RF 유도필드를 막기 위하여, 안테나(145)의 각각의 권선수는 안테나홀더(147´)의 그루브 모양구멍(550)내에 자리하고, 각각의 구멍(550)은 전도 안테나홀더(147´)의 하부 표면(147a)을 개구한다. 도 28의 전도 안테나홀더(147´)는 시일링(110)에 대한 강한 지지 기판뿐 아니라 실리콘시일링(110)에 대한 전도 후면으로서 작용하는데, 상기 경우 실리콘 시일링(110)은 도 28의 전도안테나홀더(147´)에 직접적으로 접착된다. 그러나, 바람직한 선택사항은 도 28의 실리콘 시일링(110) 및 전도후면(147´) 사이 별 모양 전도후면(400)을 삽입하는 것이다. 도 29는 한쌍의넓은 동심원 환형 구멍(560, 565)을 가지는 전도안테나홀더(147´)의 다른 실시예를 도시하는데,여기에서도 6 또는도 16의 각각의 내부및 외부코일 안테나(175, 180)중하나가 자리한다.환형구멍(560, 565)은 RF유도필드의 차단부가 없도록 안테나홀더의 하부 표면(147a)에서 개구한다.이런 실시예에서,도 28로서,전도안테나홀더는 실리콘 안테나에 대한 전도후면(별모양전도후면 400 대신)으로서 사용하고 실리콘 시일링(110)에 대한 강한 지지 기판(지지 기판 500대신)으로서 사용하고 그러므로 실리콘 시일링(110)에 직접적으로 결합될 수 있다. 바람직하게,별모양전도후면은 전도안테나홀더(147´)및실리콘 시일링(110) 사이에 삽입되고안테나홀더(147´)에 실리콘 시일링(110)이 접착된다.

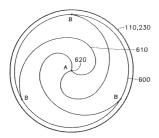

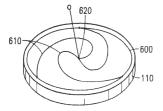

오버헤드 코일 안테나(145)는 단일 동심원 나선 권선 또는 외부 동심원 나선 권선(175, 180)으로 구성된 바와같이 상기되었다. 도 30a, 30b 및 30c는 비동심원 권선을 가지는 오버헤드 코일 안테나(145)의 다른 설계를 도시한다. 특히, 도 30a에 전체 원주 주변을 따라 적어도 거의 등전위이도록 매우 낮은 인덕턴스 및 낮은 저항으로 구성된 외부 원형 컨덕터(600)가 있다. 다수의 나선형 컨덕터(610)는 외부 전도체(600)로부터 나선형 컨덕터(610) 모두를 결합하는 중심점(620)으로 나선형 경로로 안쪽으로 방사한다. 플라즈마 소스 RF 전력(RF 발생기 150로부터)은 외부전도체(600) 및 중심점(620) 사이에 인가된다. 도 30b에 도시된 바와같이, 나선형 전도체(610)는 명면내에 놓이고, 도 30c는 나선형 전도체(610)가 돔을 형성하는 돔 모양 시일링(230)으로 사용하기 위한 다른 실시예를 도시한다. 명세서에 개시된 다양한 실시예에 사용된 돔 모양은 비선형 또는 반구형 또는 원뿔형 또는 원뿔형 단면 또는 두 개의 다른 반경의 결합같은 몇몇 아치형 곡선의회전형(본 명세서에서 개시된)이다.

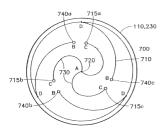

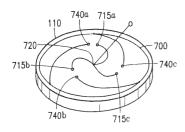

도 31a, 31b 및 31c는 오버헤드 코일 안테나의 다른 비동심원 실시예를 나타낸다. 도 31b는 도 31c가 돔 모양 경우에 해당하는 동안 편평한 경우에 해당한다. 외부 원형 전도체(700)는 단부(715a, 715b, 715c)에서 끝나는 안쪽으로 바사하는 다수의 아치형 전도 아암(710)을 가진다.

중심점(720)은 바깥쪽으로 방사하고 단부(740a, 740b, 740c)에서 끝나는 다수의 아치형 전도 아암(730)을 가진다. 도 16의 실시예에 사용된 바와같이, 도 16의 전력 스플리터(250)의 한 출력 으로부터의 RF 전력은 외부 원형 전도체(700) 및 단부(715) 사이에 인가되고, 전력 스플리터(250) 의 다른 출력으로부터의 RF 전력은 중심점(720) 및 단부(740) 사이에 인가된다.

유도 안테나 전도체는 어떤 적당한 3차원 경로를 뒤따른다. 예를들어, 도 32는 모두 동일 전도체로 형성된 이중 동심원 원통 나선형 권선, 즉, 외부 원통형 나선형(800) 및 내부 원통형 나선형(810)으로 구성된 코일 안테나(145)의 비평면 또는 3차원 실시예를 도시한다. 도 33은 도 32에 도시된 형태의 한쌍의 이중 동심원 원통형 나선형 권선이, 즉 내부 이중 동심원 원통형 나선형 권선(820) 및 외부 이중 동심원 원통형 나선형 권선(830)이 어떻게 도 16의 내부 및 외부 편평한 권선(175, 180) 대신, 도 16의 실시예의 오버헤드 안테나의 내부 및 외부 권선으로서 사용되는 가를 도시한다.

도 34는 나선형 권선(850)의 적층된 층(840a, 840b, 840c)으로 구성된 도 1의 유도 안테나(145)의 다른 편평하지 않은 실시예를 도시한다.

여기에서 상기 언급된 바와같이, 웨이퍼 중심 및 웨이퍼 주변 사이의 플라즈마 에칭 처리 차이를 유발할 수 있는 인자는 선구물질 가스 분배를 비균일하게 에칭할 수 있다. 상기 가스 분배시 불 균일성은 가스 주입구(137)를 통하여 웨이퍼의 페데스탈 측면으로부터 가스를 유입시킴으로써 발 생하여, 웨이퍼 주변 근처에 비교적 많은 에칭 선구물질 가스가 있고 웨이퍼 중심 근처에 비교적 적은 에칭 선구물질 가스가 있다. 이런 문제는 웨이퍼 중심과 고나련하여 대칭 방식으로 웨이퍼 상에 직접적으로 에칭 선구물질 가슬르 유입하기 위하여 실리콘 시일링(110)에 만들어진 중심 가 스 공급 시스템을 포함하는 도 35a, 35b, 35c, 35d 및 35e의 실리콘 시일링(110)의 실시예에 제기 된다.

도 35d를 참조하여, 1인치 두꺼운 실리콘 시일링(110)은 그것의 상부 표면에 대략적으로 0.33 인치 깊은 3.5 인치 직경의 카운터보어 개구부(900)를 가진다. 바람직하게, 도 35e에 도시된 바와같이, 약 22개의 대칭적으로 배치된 0.20 인치 직경 홀(910)은 카운터보어 개구부(900)의 상부 표면으로부터 시일링(110)의 두께 약 80%까지 드릴링된다. 보다 긴 홀(910)과 중심이 같은 작은 0.30 인치 직경 홀(920)은 실리콘 시일링(110)의 하부 표면으로부터 레이저 드릴링된다. 도 35a 및 도 35b에 도시된 바와같이, 디스크 모양 가스 공급 상부(930)는 실리콘 시일링(110)의 상부 표면 카운터보어 개구부(900)내에 설치된다. 가스 공급 상부(930)의 하부 표면은 가스 분배 분기관을 형성하는 대략 0.01 인치 깊은 3.3 인치 직경 카운터보어 개구부(940)를 가진다. 중앙 가스공급 파이프(950)는 가스 공급 상부(930)의 중심을 통하여 통과하고 카운터보어 개구부(940)으로 개방한다. 가스 공급 상부의 하부 주변 모서리는 잘려진 게단(960)을 가지며, 상기 계단(960)은 0.143 인치 깊고 방사적 내부로 0.075 인치 연장한다. 상기 계단(960)은 계단(960)과 매칭하는 크기를 가지는 환형 테플론 밀봉부(970)가 설치된 주변 포켓을 형성한다. 바람직하게, 테플론 밀봉부(970)는 도 35c에 도시된 바와같은 U 모양 단면을 가진다. 테플론 밀봉부(970)내의 환형 강철 권선 스티프너(975)는 밀봉부(970)에 대한 강도를 제공한다.

도 35a-e의 중심 가스 공급 실리콘 시일링은 전기 제어기(260)에 의해 전력 스플리터(250)를 통하여 제어된 독립적으로 조절 가능한 내부 및 외부 유도 코일 안테나(175, 180)와 결합하여 도 16의실시예에 실리콘 시일링(110)으로서 사용될 수 있다. 장점은 반응로의 중심 대 가장자리 에칭 균일성이 도 35a-e의 중심 가스 공급 실리콘 시일링(110)으로 달성된 웨이퍼 표면을 가로지르는 균일한 에칭 선구물질 가스 분배에 의해 향상되고 어떤 잔류 중심 대 가장자리 에칭 비균일성은 제어기를 사용하여 분명하게 조절함으로써 정밀하게 보상되는 것이고, 전력 레벨의 상대적 비율은상기된 콜린즈등의 공동 출원으로 개시된 방식으로 내부 및 외부 코일 안테나(175, 180)에 인가된다. 결과적으로,웨이퍼 중심 대 가장자리 에칭 균일성은 희생 에칭 프로파일, 에칭 선택성 및매우 작은 특성 크기에서 에칭 비율없이 종래 기술에서 달성할 수 없는 정도로 최적화된다.

도 36a는 플라즈마로부터 가스 공급 상부를 보다 잘 보호하는 중심 가스 공급 실리콘 시일링의 다른 바람직한 실시예를 도시한다. 이런 실시예에서, 어깨(980)는 실리콘 시일링(110)에서 카운터보어 개구부(900)의 주변 가장자리를 따라 제공된다. 실리콘 웨이퍼(985)는 어깨(980)상에 자리하고 실리콘 시일링(110) 상부의 카운터보어 개구부(900) 및 가스 공급 상부(930)의 하부 카운터보어 개구부(940)를 두 개의 분리 챔버로 분리한다. 실리콘 웨이퍼(985)는 실리콘 시일링(110)의가스 공급 홀(910)로부터 측면으로 대치되어 드릴링된 다수의 가스 공급 홀(986)을 가진다. 이런방식으로 실리콘 웨이퍼(985)의 삽입은 홀(920)을 통하여 챔버로부터 위쪽으로 확산하는 플라즈마이온에 대한 가스 공급 상부(930)에 어떤 직접적인 라인 경로를 제거한다. 이런 특징은 플라즈마에 의한 공격으로부터 상부(930)를 보호한다. 상부(930)는 RF 유도 필드를 적당하게 감쇠시키지않는 반도체 또는 유전같은 재료이거나 만약, 직경이 유도 안테나의 중심 널(null) 직경보다 작으면, 스테인레스 스틸같은 전도체일 수 있다.

도 35a-e 및 36a의 실시예에서, 가스 공급 홀(910, 920)은 시일링(110)의 중심 주변에 그룹지어진다. 그러나, 홀(910, 920)은 중심으로부터 주변으로 분산되고, 만약 목표되면, 중심 대신 주변근처에 그룹지어진다. 이것은 도 36b에 도시되고, 여기에서 가스 공급 홀(910, 920)은 시일링(110)의 주변 주변에 분산된다.

도 37a는 편평 실리콘 시일링(110)을 채용하는 임의의 실시예 예를들어, 절연 접지된 패러데이 시일드(990)가 상부 유도 안테나(145)와 실리콘 시일링(110)사이에 삽입되는 도 1의 실시예에 응용될 수 있는 변형예를 예시한다. 패러데이 시일드는 그 형태가 도 37b의 최상부도에 가장 장 나타나 있는 종래 형태의 시일드이며 유도 안테나(145)로부터 플라즈마로의 용량성 결합을 감소시키는데 사용된다. 도 38a는 돔-형태 실리콘 시일링(230)을 채용하는 임의의 실시예 예를들어, 절연 접지된 패러데이 시일드(990)가 상부 유도 안테나(145)와 실리콘 시일링(230)사이에 개재되는 도 1의 실시예에 응용될 수 있는 변형예를 예시한다. 도 38b는 실린더 측 유도 안테나(220)와 실린더형 반도체 윈도우 전극(215) 사이에 개재된 실린더형 패러데이 시일드(990')인 추가의 구조적 특

징과 함께, 실린더 축 반도체 윈도우 전극(215)과 실린더 축 유도 안테나(220)를 갖는 도 7 내지도 9의 실시예에 대응하는 실시예를 예시한다.

도 39a는 상기에서 설명한 플라즈마 에칭 반응기의 엘리먼트에 대한 바람직한 배열을 예시하는 비례도이다. 도 39b는 상부 유도 안테나를 구현하는 데 채용된 튜브-형태 컨덕터의 단면도이고, 이튜브의 내부 체적은 물과 같은 냉각재를 펌핑시키는 데 사용된다.

상기한 실시예의 각각은 반도체 윈도우의의 전기적 접속부를 RF 전력 소스 또는 접지와 같은 전기적 전위에 채용하므로써 전극과 같은 반도체 윈도우를 채용하는 것으로 설명되어 있다. 그러나, 전극으로서 반도체 윈도우의 사용과 이러한 전기적 접속부는 반드시 필요한 것은 아니다. 사실상, 반도체 윈도우는 전극으로서 채용되기 보단, 전기적으로 플로팅시키도록 허용될 수 있고 좌측으로 접속되지 않을 수 있다. 그럼에도 불구하고 반드시 전극으로 기능하지 않는 다해도 어떤 이점을 제공할 수 있다. 하나의 이점은 반도체 윈도우의 반도체 재료(예를들어, 실리콘)는,전형적인 플라즈마 반응기의 시일링내에 또는 가까이에 채용된 다른 재료(예를들어, 석영 또는 알루미늄)에 비교할 때 소스로서 덜 오염될 수 있는 소스이다. 반도체 윈도우의 또다른 이점은 플루오르에 대한 스카빈저(scavenger)이다. 따라서, 반도체 윈도우는 플루오르에 대한 스카빈저 및 유도 안테나에 대한 시일드로서 동시에 기능할 수 있다.

상기한 임의의 실시예는 챔버 내부의 가로놓임 코일 인덕터 및 반도체 윈도우 전극 모두를 위치시키므로써 변형될 수 있다. 이 변형예에서, 반도체 윈도우 전극은 챔버 밀봉체의 일부라기 보단 이밀봉체의 시일링 하부에 놓인다. 도 1.4-12,16,18-20,23 및 37a의 실시예에 채용된 유형의 평면형반도체 윈도우 전극에 대해, 도 40은 챔버 시일링(106)으로부터 분리되고 하부에 있는 챔버(100)내부의 평면형 유도 안테나(145)와 평면형 반도체 윈도우 전극(110)을 예시한다.도 13a-15,17a,17b,21,22,24 및 38의 실시예에 채용된 유형의 만곡 또는 돔-형태 반도체 윈도우 전극에대해, 도 41은 돔-형태 반도체 윈도우 전극(230) 및 챔버 시일링(106)하부의 챔버(100)내부에 있는 동일 형태의 유도 안테나(235)를 예시한다. 도 7-9의 실시예에 채용된 실린더형 반도체 윈도우에 대해, 도 41b는 챔버(100) 내부의 실린더형 유도 안테나(235')와 실린더형 반도체 윈도우(230')를 예시한다.

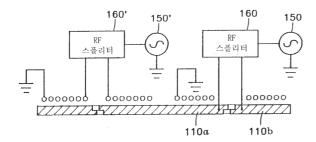

상기 실시예의 각각에 대한 반도체 윈도우가 모노리딕 구조로서 예시되었을 지라도, 일 변형 실시 예에 따라 반도체 윈도우는 복수 부재로 세그먼트화 돨 수 있다. 상세히는, 도 42 및 43에서 평면형 반도체 윈도우(110')(예를들어, 도 1 또는 도 40의 평면형 반도체 윈도우 전극(110)에 해당)는디스크(110a)와 동심을 이루고 포위하는 주변 환형부(110b)와 중앙 디스크(110a)를 포함하여 이루어진다. 바람직하게, 디스크(110a)와 환형부(110b)는 실리콘과 같은 반도체 재료 또는 상기 제안된 기타 반도체 재료중의 하나로 이루어진다. 일 실시예에서, 상대적인 중앙부로부터에지로(center-to-edge)의 에칭 성능은 요구된하는 바와 같이 상이한 레벨의 RF 전력를디스크(110a)와 환형부(110b)에 인가하므로써 조정된다. 이것은 디스크(110a)와 환형부(110b)에인가된 각각의 RF 전력 출력을 갖는 RF 전력 스플리터(160)를 공급하는 단일 RF 소스(150)를 채용하므로써 가장 양호하게 성취된다. 이것은 RF 접지(도 42에 도시되지 않음)에 접속된 유도성 측역과 같은 제 3 단자(예를들어, 접지 전극)를 필요로 한다. 만일, 예를들어, 웨이퍼의 중앙 근처의 애칭율이웨이퍼의 주반부 근처의 애칭율 보다 크다면, RF 전력 스플리터(160)는 더욱 많은 RF 전력를 디스크(110a)에 인가하고 반도체 윈도우의 주변 환형부(110b)에 비교적 적은 RF 전력를 인가하므로써 조정될 수 있다. 더욱이, 중앙부로부터에지로의 애칭 성능에 대한 더욱 양호한 제어 윈도우 전극(110a,110b)과 결합될 수 있다. 상세히는, 도 16의 내부 및 외부 유도 안테나(175,180)는 반도체 윈도우 전극의 내부 디스크(110a)와 외부환형부(110b)와 결합될 수 있다. 도 16에서와 같이, 전력 스플리터(250)는 내부 및 외부 유도 안테나(175,180)의 각각에 연결되는 별개의 RF 전력 출력을 갖는다.

도 44는 스플릿 반도체 윈도우 전극이 활 형태 또는 돔-형태인 도 42의 실시예에 대응한다. 도 44에서, 반도체 윈도우 전극 중앙 디스크(110a)는 돔의 중앙부에 대응하고 반도체 윈도우 전극 주변환형부(11b)는 돔이 원주 베이스에서 연속하는 실린더와 돔의 외부에 대응한다. 도 45는 중앙 디스크(110a)가 거의 평면형태이고 환형부(110b)가 거의 실린더 측벽이도록 돔의 만곡부가 거의 사라지는 도 44의 실시예에 대한 변형 예를 나타낸다.

도 42-45의 스플리팅을 위해 필요한 제 3 단자가 접지된 측벽으로서 설명되러진 반면에, 또다른 변형예에 따라 제 3 단자는 반도체 윈도우 주변 환형부(110 b)일 수 있지만 RF 전력은 웨이퍼 페데스탈(120)과 같은 기타 실체와 반도체 윈도우 중앙 디스크(110a)사이에 스플리팅된다. 도 46 및 47은 후자의 변형예가 각각 도 42 및 44의 실시예를 변경하는 방법을 나타낸다.도 45의 실시예에서 수행된 변형은 도 13b의 실시예에 대응하는 실시예가 된다. 도 46 및 47의 실시예에서, RF 전력 스플리터(250)는 반도체 윈도우 중앙 디스크(110a)에 접속된 자신의 RF 전력 출력과 웨이퍼 페데스탈(120)에 접속된 자신의 또다른 RF 전력 출력을 갖는 반면에, 반도체 윈도우 주변 환형부(110b)는 접지된다.

반도체 윈도우의 유효 플라즈마 상호작용 영역은 웨이퍼, 웨이퍼 페데스탈 및 반도체 윈도우의 유효 플라즈마 상호작용 영역의 비율을 변경하기 위해 변경될 수 있다. 이러한 상호작용 영역의 비율에 대한 3 체제가 있다.

- (1) 대칭형: 유효 플라즈마 상호작용 영역은 거의 동일(영역비율은 거의 1)이므로, 웨이퍼와 반도체 윈도우 전극은 동일 RF 플라즈마 전류 밀도 및 동일 RF 및 DC 시스(sheath) 전압 크기를 갖는다.

- (2) 부분 비대칭형 : 이 영역비율은 1 로부터 2 내지 4 사이의 인수이므로, 소 영역 전극에서의 상기 전류 밀도 및 RF 및 DC 시스 전압 크기는 대 영역전극에서의 상기 전류 밀도 및 RF 및 DC 시 스 전압 크기 보다 크고 영역비율이 더 증가함에 따라 현저하게 변한다.

(3) 완전 비대칭형 : 이 영역비율은 2 내지 4 사이의 인수이므로, 기 전류 밀도 및 RF 및 DC 시스 전압 크기는 영역비율이 더욱 증가함에 따라 현저히 변화하지 않으며, 포화상태에 도달된다

최종 사례(즉 사례(3))에서, 시스전압은 더욱 크게 강하하며 RF 전류 밀도는 반도체 윈도우 전극 또는 웨이퍼/웨이퍼 대(pedestal)중의 하나에 나타나며, 이들중 어는 하나도 더욱 작은 유효 플라 즈마 상호작용 영역을 갖는다. 이러한 방식에서 RF 전류 밀도의 상승과 시스전압 강하는 상호작용 이 감소되는 일 엘리먼트(반도체 윈도우 또는 웨이퍼/웨이퍼 페데스탈)에 대한 RF 바이어스 인가 의 증가와 동일 효과를 갖는다. 반도체 윈도우에 대해, 이러한 변화는 스카빈저 재료를 플라즈마 내부로의 스패터링 비율에 영향을 미치며 반도체 전극의 표면상에서의 중합반응률에 영향을 미친 다. 웨이퍼/웨이퍼 페데스탈에 대해, 이러한 변화는 일반적으로 인가된 바이어스 RF 전력의 변화 에 의해 영향을 받는 파라미터 예를들어, 에칭율, 에칭 프로파일 및 에칭 선택도와 같은 처리에 영향을 미친다.

2 개 보다 많은 전극을 갖는 반응기에서 유효 플라즈마 상호작용 영역의 비율을 조정할 때 동일원리가 적용된다. 예를들어, 도 23 및 24에서, 4 개의 전극을 사실상 하나의 주파수에서 구동하고 또다른 주파수에서 접지하는 전극을 사용하여 2 개의 전극으로 감소시킨다. 구동/접지 전극 쌍의각각은 이전 단락에서 개관된 것과 동일 효과를 갖는 변화 영역 비율로, 별개로 분석된다. 또다른 예로서, 실린더형 측벽과 같은 제 3 전극이 접지 또는 또다른 RF 소스와 같은 전위에 접속되는 도 4-12의 예에서, 접지된 전극(예를들어, 실린더형 측벽)과 RF 전력 소스에 접속된 다른 단자 사이에서 전류를 리턴하는 접지 할당부가 유효 플라즈마 상호작용 영역 비율 뿐만 아니라 2 개의 구동단자 사이의 위상 차와 같은 동적 인자에 의해 판정되는 것을 제외하곤, 동일한 분석을 적용한다. 2개의 RF-구동 전극사이에 일정한 소정 위상차를 유지하기 위해, Kenneth S. collins 씨에 의한미합중국 특허 제 5,439,313 호에 개시된 발명이 채용될 수 있다.

항 쌍의 RF-구동 엘리먼트(전극 또는 유도 안테나)사이의 요구된 위상 관계를 수립하기 위한 능력이 RF 전력 할당부에 채용될 수 있다. 예를들어, 세그먼트된 유도 안테나 부를 채용하는 도 16,17a,17b 및 18과 같은 실시예에서, 상기한 두 개의 세그먼트된 유도 안테나 부 사이의 전력 할당부는 각각의 안테나부에 인가된 RF전압의 크기를 변화시키므로써 달성된다. 그러나, 전력 할당부는 상이한 안테나부에 인가된 RF 전압간의 위상각을 변화시키므로써 변경될 수 있다. 마찬가지로, 세그먼트된 반도체 윈도우 부를 채용하는 도 42-47과 같은 실시예에서, 상기한 바와 같은 두개의 세그먼트된 반도체 윈도우 부 사이의 전력 할당은 각각의 반도체 윈도우 부에 인가된 RF 전압의 크기를 변화시키므로써 성취된다. 그러나, 전력 할당은 상이한 반도체 윈도우 부에 인가된 RF 전압간의 위상각을 변경시키므로써도 변화될 수 있다.

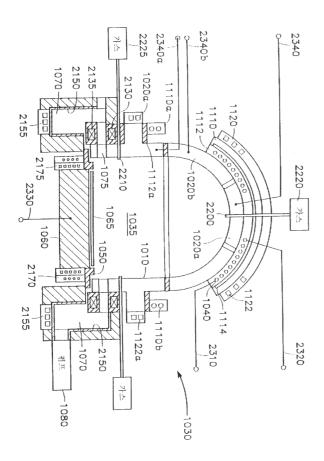

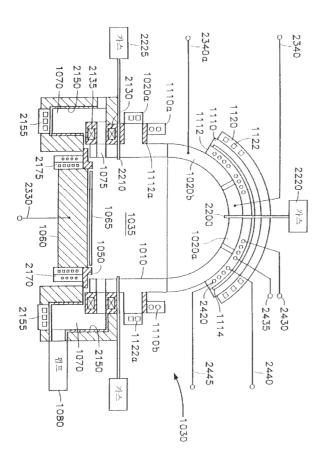

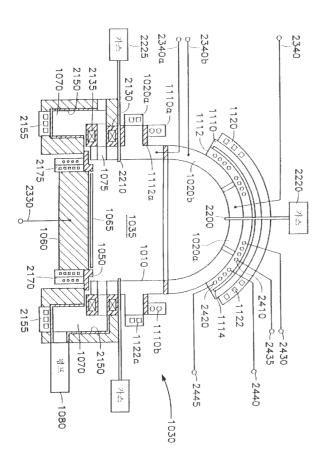

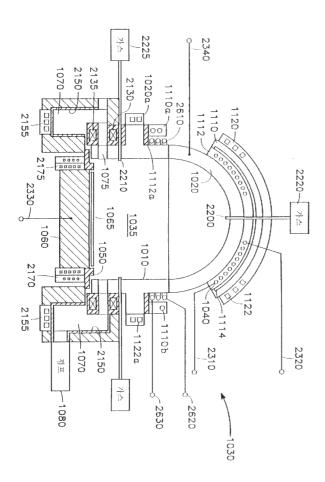

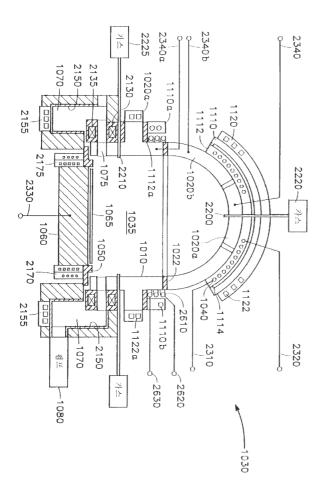

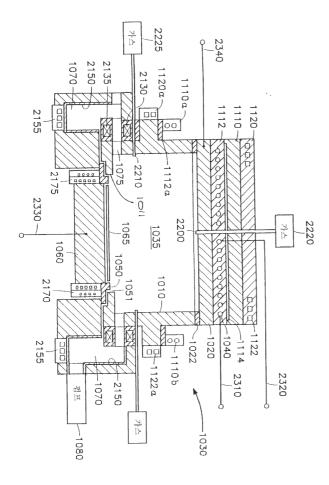

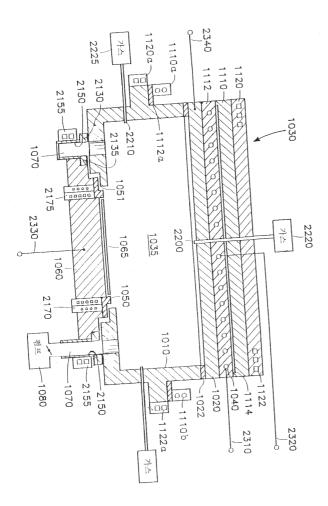

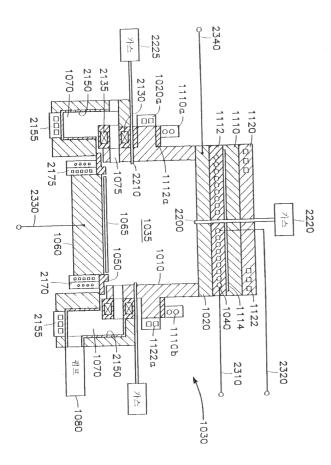

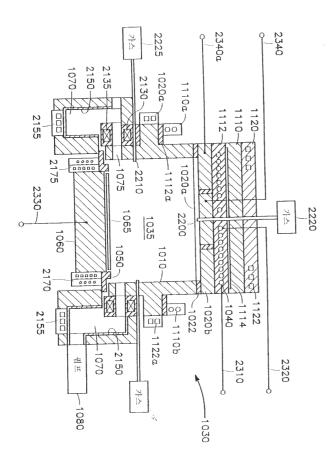

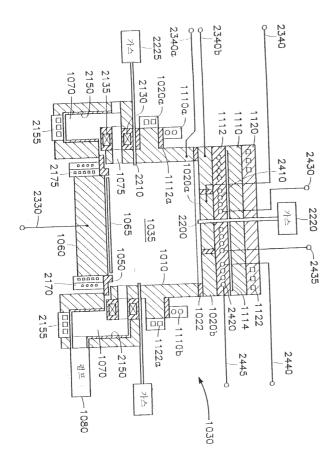

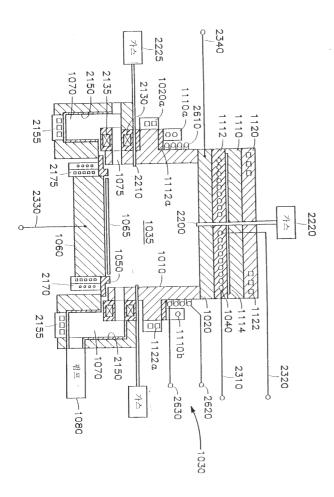

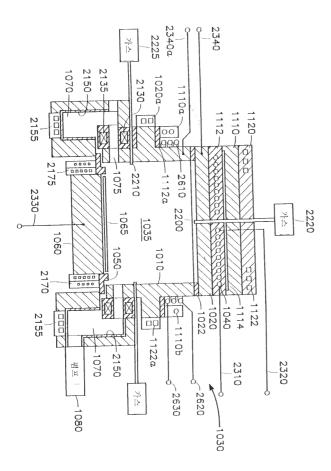

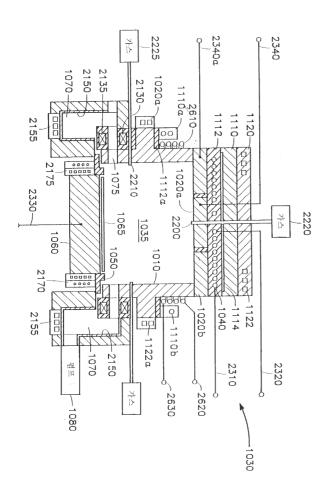

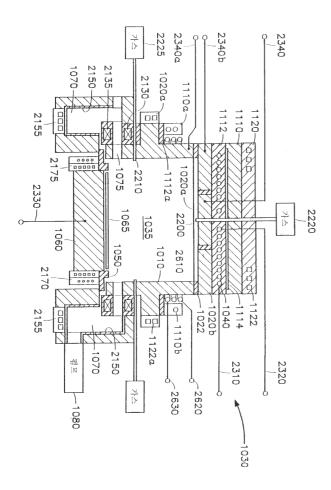

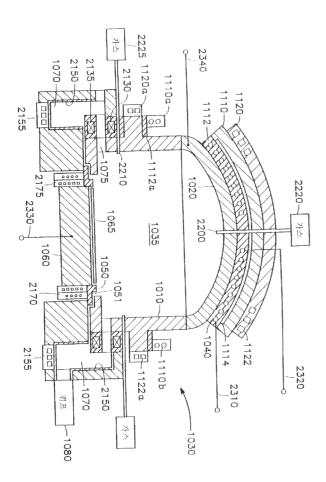

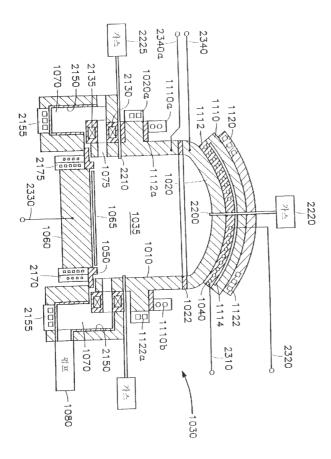

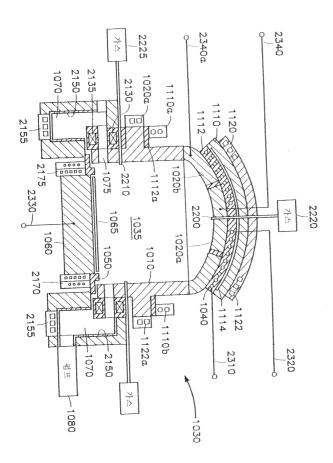

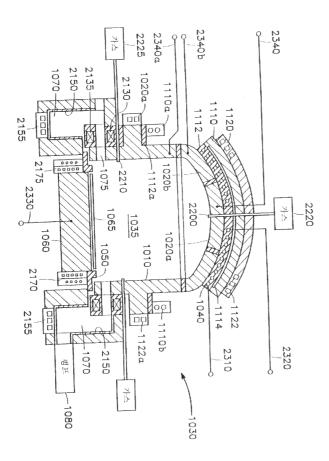

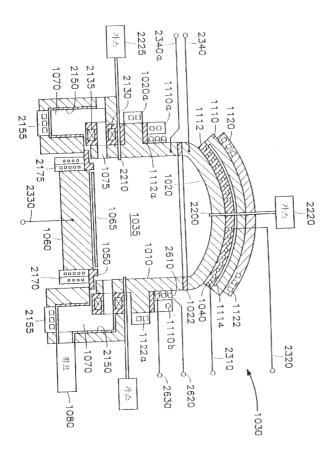

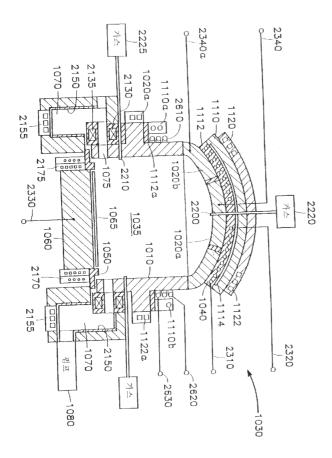

도 48a는 상부 반도체 윈도우 전극이 디스크\_형태 반도체 시일링(1020)으로부터 하향 수직으로 신장하는 반도체 스커트(1010) 까지 확대되고, 스커트(1010)와 시일링(1020)은 유전 절연 링(1022)에 의해 서로 절연되고 반응기 챔버의 처리 영역(1035)내의 플라즈마를 가두는 모든-반도체 밀봉체를 구성한다는 개념을 제외하곤 도 1의 실시예와 매우 유사하다. 도 1의 실시예에서와 같이, 코일 인덕터(1040)는 반도체 시일링(1020) 상부에 가로놓인다. 스커트(1010)는 실린더형일 수 있다. 스커트(1010)와 일체로 형성된 선택적인 환형 반도체 푸트(1011)는 실린더형 스커트(1010)의 최하부로부터 방사상 내부 방향으로 뻗을 수 있다. 칼라(collar)(1050)는 푸트(1011)의 방사상 내부 방향 에지의 근처로부터 가공되는 웨이퍼(1065)를 지지하는 웨이퍼 페데스탈(1060) 가까이로 뻗으며, 이들 사이에 굴곡을 이루는 고종횡비 갭(1051)을 남긴다. 바람직한 실시예에서, 웨이퍼 페데스탈(1060)은 정전 척을 포함한다. 칼라(1050)의 일 용도는 처리영역(1035)으로부터 펌핑환형부(1070)까지의 대(1060)주위로 탈출하는 플라즈마를 좁은(고종횡비) 갭 또는 통로(1051)에 가뭄으로써, 탈출 이온은 펌핑 환형부(1070)에 도달하기 이전에 통로를 따라 벽 표면에서 재결합된다. 또다른 특징 구성은 칼라(1050)가 갭(1051)이 구불구불한 경로를 제공하고 펌핑환형부(1070)로 탈출하는 플라즈마 이온이 구불구불한 경로를 반드시 따르도록 하기 위해 중복 배플 구조를 제공한다. 이러한 특징 구성은 겝(1051) 내부에 탈출 플라즈마 이온의 재결합을 향상시킨다.

펌핑 환형부(1070)는 웨이퍼 슬릿 밸브(1075)를 통하여 처리영역에 결합되고 펌프(1080)에 의해소개된다. 슬릿 밸브(1075)를 통한 플라즈마 누설의 방지 또는 감소를 위해, 슬릿 밸브(1075)의 내부 표면상의 플라즈마 이온의 재결합을 향상시키기 위해, 슬릿 밸브(1075)는 가능할 수 있는 가장 좁은 개구를 제공할 수 있는 고종횡비를 갖는다. 도 48a의 바람직한 실시예에서, 반도체 밀봉체(1030)는 챔버의 진공 경계이다. 대안으로, 이러한 반도체 밀봉체는 반도체 밀봉체 자체가 진공경계가 아니도록 금소성 진공 밀봉체내에 구비될 수 있다. 후자의 대안은 종래 기술의 반응기 챔버에 존재하는 레트로-피팅에 의해 구현된 본 발명의 실시예에 유용하다.

도 48a의 모든 반도체 가공 챔버 밀봉체에 의해 여러 이점이 제공된다. 일 이점은 처리영역(1035)을 둘러싸는 모든 반도체 표면은 축적된 중합체에 의해 패시베이팅될 필요가 없는 대신 플라즈마처리 동안 패시베이팅되지 않은 맨 상태에 있을 수 있다. 이것은 플라즈마와 반도체 표면간의 상호작용에 의한 것이기 때문이고 웨이퍼의 플라즈마 가공에 악영향을 끼치지 않는다. 반면에, 처리 영역(1035)을 둘러싸는 반도체 표면과 플라즈마간의 상호작용에 의한 부산물은 소멸성이 있고 펌프(1080)로부터 용이하게 펌핑되어 제거될 수 있다. 처리영역(1035)을 둘러싸는 표면을 패시베이팅시킬 필요가 없기 때문에, 중요한 이점으로서 이러한 표면을 세정시키기 위해 반응기 작동을 중단시킬 필요가 없다.

처리영역(1035)을 둘러싸는 표면상에서 중합체의 축적을 방지하기 위한 두 방법이 있다. 하나의 방법은 중합체 응축 온도 위에서 이러한 표면을 유지하는 것이다. 이러한 목적을 위해, 시일링(1020) 및 스커트(1010)는 반도체와 같은 고 열 도전재로 형성된다. 대안으로, 이 재료는 반도체일 필요가 없이 예를들어, 실리콘 질화물, 알루미늄 질화물, 석영 또는 알루미늄일 수 있 다. 반도체 재료를 채용하는 바람직한 실시예에서, 이 재료는 실리콘이지만 실리콘 카바이드와 같 은 기타 반도체 재료가 채용될 수 있다.실리콘은 실리콘 화합물을 함유하는 플라즈마 처리(예를들 어, 실리콘 이산화물 에칭)에 바람직하다.이것은 실리콘 윈도우(1030)가 웨이퍼상에서의 에칭율에 비해 이러한 프로세스에서 매우 느리게 에칭하기 때문이다.(웨이퍼로부터 에칭된 1 μ 실리콘 이산화물마다 실리콘 밀봉체 표면으로부터 약 3Å). 따라서, 약 35,000 웨이퍼는 실리콘 밀봉체(1030)로부터 에칭된 상당 량의 재료(1mm)가 에칭되기 전에 가공될 수 있다. 실리콘 밀봉체(1030)의 에칭 두께에 기인한 허용가능 손실은, (a)구조 무결성을 위해 필요한 밀봉체(1030)의 두께, (b) 코일 안테나로부터 챔버 내부로의 RF 결합을 뚜렷히 변화시키는 두께의 변화에 의해 제한된다. 만일 상기한 바와 같이 반도체 재료에 대한 지침이 주어진다면 10% 미만의 두께 변화는 웨이퍼 가공에 영향을 주기에 충분한 RF 결합에서의 뚜렷한 변화를 나타내지 않을 것이다.

클로라인 화합물을 포함하는, 알루미늄 또는 폴리실리콘 플라즈마 에칭 처리에 대해, 실리콘 벽은 지나치게 신속하게 에칭될 수 있고(기본적인 플라즈마 파라미터가 어떻게 제어되는 가에 기초하여)따라서 실리콘 또는 반도체 재료는 이러한 응용에 적합하지 않다. 그러나, 반도체 재료는 본 발명을 수행하는 데 반드시 필요한 것은 아니며(전기적 또는 RF 전위가 반도체 재료에 인가되지 않는 다면), 실리콘 질화물과 같은 임의의 적절한 내구성을 갖는 비-반도체가 처리 영역 밀봉체(1030)를 위해 채용될 수 있다.

선택 온도(예를들어, 중합체 증착을 방지 하기 위한)에서, 반도체 시일링(1020)의 온도를 유지하기 위해, 직접적 열 접촉 또는 간접적 열 접촉을 채용하는 온도 제어 시스템이 채용될 수 있다. 도면에서, 간접적 열 접촉을 채용하는 온도 제어 시스템이 예시되어 있으며 이 시스템은 시일링(1020) 상부에 걸치는 코일 인덕터(1040)을 둘러싸는 절연층(1112)의 최상부에 있는 가열층(1110)과 열 저항 에어 갭(1114)에 의해 가열층(1110)으로부터 분리되고 가열층(1110) 상부에 걸친 냉각 플레이트(1120)를 포함한다. 가열층(1110)은 종래의 가열 엘리먼트(도 48a에 도시되지 않음)를 포함하지만, 냉각 플레이트(1120)는 내부 수냉 재킷(1122)을 갖는다. 냉각플레이트(1120)에 의해 제공된 냉각량은 시일링(1020)에 대한 임의의 플라즈마 가열을 충분히 오프셋팅시키기는 것보다 많으며, 가열층(1110)이 제공할 수 있는 가열량은 냉각 플레이트(1120)로부터의 냉각을 충분히 오프셋팅시키기는 것보다 많다. 종래의 온도 센서/제어기(도 48a에 도시되지 않음)는 가열층(1110)의 저항성 엘리먼트에서의 전류 흐름의 양을 지배한다.

선택온도(예를들어, 중합체 증착을 방지하기 위한)에서 반도체 스커트(1010)의 온도를 유지하기 위해, 직접적 열 접촉 또는 간접적 열 접촉을 채용하는 온도 제어 시스템이 채용될 수 있다. 도면 에서, 직접적 열 접촉을 채용하는 온도 제어 시스템이 예시되어 있으며 이 시스템은 반드시 필요 한 것은 아닌 선택적 절연층(1112a)를 통하여 스커트(1010)와 접촉하며 포위하는 가열 링(1110a)을 포함한다. 냉각 링(1120a)은 스커트(1010)와 접촉한다. 선택적 절연층이 냉각 링(1120a)과 스 커트(1010) 사이에 위치될 수 있다. 가열 링(1110a)이 종래의 전기적 가열 엘리먼트(1110b)를 포함하는 반면에, 냉각 링(1120a)은 내부 수냉 재킷(1122a)을 포함한다. 냉각 링(1120a)에 의해 제 공되는 냉각량은 스커트(1010)의 임의의 플라즈마 가열을 충분히 오프셋트시키는 것 보다 많으며 가열 링(1110a)이 제공할 수 있는 가열량은 냉각 링(1120a)으로 부터의 냉각을 충분히 오프셋트시 키는 것 보다 많다. 종래의 온도 센서/제어기(도 48a에 도시되지 않음)는 가열링(1110a)의 저항성 엘리먼트에서의 전류 흐름의 양을 지배한다.

처리 영역(1035)을 둘러싸는 표면상에서의 중합체 증착을 방지하는 제 2 방법은 플라즈마로 부터의 이온에 의한 이러한 표면에 대한 이온 충격을 증대시키기 위해 충분한 강도로 이러한 표면에 따 전위를 인가하는 것이다. 이온 충격 전력은 중합체가 증착되는 것보다 빠르게 표면으로부터 중합체를 제거하기에 충분해야 한다. 이러한 목적으로, 디스크-형태 시일링(1020)과 실린더형 스커트(1010)는 인가된 RF 전력를 위해 전극으로 작용하기에 충분한 도전성이어야 한다. 시일링(1020)과 스커트(1010)는 바람직하게 반도체이다. 그러나, 이것들은 바람직하게 금속성이지 않아야 하는데 이는 처리 영역(1035)에서 플라즈마에 노출된 금속은 챔버 및 웨이퍼를 오염시키는 부산물을 공급하기 때문이다.시일링(1020)및 스커트(1010)를 위한 도전 (금속성) 재료에 걸쳐 반도체 재료가 바람직한 또다른 이유는 시일링(1020)의 도전재료가 코일 인덕터(1040)로 부터의 RF 플라즈마소스 전력의 시일링(1020)을 통하여 방지될 것이라는 점이다.

바람직한 실시예에서, 중합체 증착을 방지하기 위한 두 방법(온도 제어 및 윈도우 전극상에 인가된 RF 전위를 스퍼터링-촉진시킴)이 조합된다. 이온 충격 또는 표면의 스퍼터링을 촉진시키는 반도체 밀봉체(1030)로의 RF 전위 인가는

표면상에서의 중합체 축적을 방지 하기 위해 필요한 표면온도를 감소시킨다. 예를들어, 이 온도는

전형적으로 종래 기술에서 필요한 약 265 c로부터 중합체 축적을 방지하기 위해 충분히 높은 바이

어스전압에서 약 100 c로 감소될 수 있으므로, 본 발명은 반응기가 냉가기를 동작시키면서 처리 영역(1035) 내부에서 표면상의 중합체 축적을 방지한다. 역으로, 반도체 밀봉부(1030)의 표면 온도의 상승은 표면상에서의 중합체 축적을 방지하기에 필요한 스퍼터링 또는 이농 충격 전력를 유익하게 감소시킨다. 일 예에서, 반도체 시일링(1020)에 인가된 RF 전력은 0.1MHz에서 500와트이고, 웨이퍼 페데스탈(1060)에 인가된 바이어스 전력은 1.8MHz에서 1400와트이고, 코일 안테나(1040)

에 인가된 소스 전력은 2.0MHz에서 3000와트인 반면에 반도체 밀봉체(1030)의 온도가 200 c로 유지된다. 코일 안테나(1040) 형태의 유도 안테나가 본 발명의 실시예에서 수행되도록 채용되었지만, 기타 안테나가 채용될 수 있고, 본 발명은 코일 안테나의 사용에 한정되지 않는다.

상기한 바와 같이, 웨이퍼 페데스탈(1060)에서 플라즈마 누설은 칼라(1050), 고종횡비의 개구 및/또는 구불구불한 통로 재공에 의해 방지된다. 또한, 상기한 바와 같이, 슬릿 밸브(1075)는 동일목적으로 고종횡비의 개구이다. 이러한 고종횡비의 개구는 칼라(1050)에 의해 덮인 측벽 대 갭 뿐만 아니라 처리 가스 주입 구멍과 같은 기타 통로 유형을 포함하며 플라즈마 이온의 누설을 자연적으로 봉쇄한다. 그러나 스릿 밸브(1075)는 반도체 웨이퍼(1065)를 수용할 만큼 충분하므로 그것을 관통하는 플라즈마 이온 누설에 훨씬 취약하다.처리 영역(1035)으로부터 슬릿 밸브(1075)와 같

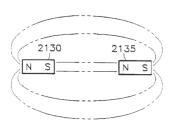

은 큰 구멍을 통하는 플라즈마의 누설을 방지하기 위해, 본 발명의 선택적 특징구조는 슬릿 밸브 개구를 가로지르는 자솟 라인을 수립하기 위해 슬릿 밸브(1075)의 대향 경계상에 자석 링(2130,2135)과 같은 플라즈마 가둠 자석을 포함한다. 슬릿 밸브(1075)에 접근시 플라즈마 이온, 전자 또는 전하 입자는 슬릿 밸브(1075)를 통하는 경로로부터 전환되도록 자신의 속도와 자솟 라인에 직각인 가소을 받으며 대신에 펌핑 환형부(1070)에 도달하기 전에 재결합에 의해 제거되도록 슬릿 밸브의 측벽에 충돌한다. 이것은 자석(2130,2135)의 자속 밀도, 이온 및 입자상의 전하, 이들의 질량 및 속도에 의거하여 슬릿 밸브(1075)를 통한 이온 통과 가능성을 감소시킨다. 복수 개자석 사용은 구머을 가로지르는 자속을 최대화시키며 웨이퍼(1065)를 향하여 쳄버내로 침입하는 자속을 최소화하는 이점을 갖는다. 바람직하게, 자석(2130,2135)은 플라즈마의 중이온에 영향을 줄만큼 충분히 강하다. 예를들어, 자석은 플라즈마내의 전자 에너지, 플라즈마 이온 에너지, 플라즈마 반응기 챔버 압력 및 기타 플라즈마 파라미터에 의거하여 약 500가우스 이상의 자속밀도를 나타내야 한다. 예를들어, 5mT 와 100mT 사이의 반응기 챔버 압력에 걸쳐 약 75% 만큼 자석 보다 2 cm 상부에서의 이온 포화 전류를 감소시킨 구멍을 가로지르는 100 가우스 내지 200 가우스 사이의 자속밀도, 1 입방 센티미터당 전자가 1 내지 5x10 11 인 범위의 전자 밀도. 자석은 바람직하게

100 c 로 냉각되거나, 적어도 자석의 퀴리 온도 보다 낮고 예를들어, 내구성 재료(예를들어 실리 콘 질화물)에 의한 포위에 의해 플라즈마 이온으로부터 차페된다. 이러한 자석(2130,2135)에 의한 대안 배열은 아래에서 설명된다.

자석(2130,2135)은 전하-중성 중합체-형성 입자를 포함하는 전하-중성 라디칼 또는 입자가 슬릿밸 보(1075)를 통과하는 것을 방해하지 않는다. 따라서, 중합체는 펌핑 환형부(1070)에 축적될 수 있다. 펌핑 환형부(1070)에 이러한 중합체를 포획 및 제어하기 위해, 펌핑 환형부(1070)의 내부 표면은 슬릿밸보(1075)를 통하여 탈출하는 중합체를 펌핑 환형부(1070)의 내부 표면에 증착하기 위해 중합체 응축 온도 보다 낮은 온도에서 유지된다. 바람직하게, 펌핑 환형부(1070)는 알루미늄, 양극처리된 알루미늄, 알루미늄상에 플라즈마-스프레이처리된 실리콘과 같은 제거가능한 냉각 라이너(2150)로 피복되고, 냉각 싱크(2155)에 열적으로 결합된다. 이 구조의 이점은 플라즈마 이온에 의해 영향을 받지 않은 펌핑 환형부(1070)의 냉각 라이너(2150)상에 축적되는 중합체가, 캠버(1030)내의 오염물질이 확산되어지도록 스퍼터링 오프되기가 용이하지 않으며 프라즈마 가열에 취약하지 않다는 것이다. 따라서, 중합체는 챔버(1030)내의 오염 위험을 생성하기 전에 냉각라이너(2150)에 두꺼운 두께로 축적되는 것을 허용할 수 있다. 결과적으로, 중요한 이점으로서, 냉각 라이너(2150)는 최 원격 위치인 경우를 제외하곤 주기적으로 세정되거나 교환될 필요가 없다. 냉각 라이너(2150)는 중합체 증착율이 너무 낮으므로 펌핑 환형부 표면에 축적된 중합체가 챔버에서 처리되는 30,000 내지 40,000 웨이퍼 보다 빈번히 제거될 필요가 없을 수 있다.

칼라(1050)의 표면상에서의 중합체 축적을 방지하기 위해, 칼라(1050)의 온도는 열 싱크(2170), 및 이 칼라(1050)에 열적으로 결합된 냉각 싱크(2175)를 포함하는 종래의 온도 제어 시스템에 의 해 중합체 응축 온도 보다 높게 선택된 온도로 유지된다.

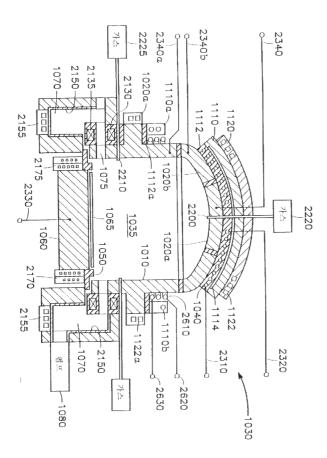

본 발명의 다른 특징 구조에 따라, 시일링(1020)의 중앙 및 에지부의 중앙 및 에지 가스 주입 포트(2200,2210)의 각각은 독립적인 가스 공급(2220,2225)으로부터 플라즈마 프리커서 가스를 수용한다. 이 구조로, 웨이퍼 중앙 및 웨이퍼 주변부에서의 가스 혼합 및 가스 유통율은 웨이퍼 센터에지 가공 비균일성을 정확히 보상하기 위해 독립적으로 조정될 수 있다. 따라서, 예를들어, 가스공급(2220)은 웨이퍼 중앙에 걸쳐 일 유통율로 일 플라즈마 프리커서 가스 혼합을 제공하는 반면에 가스 공급(2225)은 웨이퍼 주변부에 걸쳐 다른 유통율로 다른 플라즈마 프리커서 가스 혼합을 제공하는 반면에 가스 공급(2225)은 웨이퍼 주변부에 걸쳐 다른 유통율로 다른 플라즈마 프리커서 가스 혼합을 제공한다. 도면은 웨이퍼 중앙 상부에 가로 놓이는 단일 가스 유입구(2220)에 결합된 가스공급(2220)을 도시하지만, 다수의 가스 유입구 또는 샤워헤드 구성이 이 웨이퍼 중앙에 걸치는 가스의 흐름을 제어하기 위해 채용될 수 있다. 도면이 스커트91010) 또는 측벽을 통하여 웨이퍼 에지로 방사상으로 뻗는 다수의 가스 유입구(2210)에 결합된 가스 공급(2225)을 도시하지만, 이 가스 공급(2225)은 웨이퍼 에지에 걸친 게스 흐름을 제어하기 위해 시일링(1020)을 통하여 하향으로 또는 칼라(1050)를 통하여 상향으로 웨이퍼를 향하여 뻗는 가스 유입구에 결합될 수 있다.

플라즈마 소스 RF 전력은 코일 단자(2310,2320)를 가로질러 코일 인덕터(1040)에 인가된다. 바이어스 RF 전력이 페데스탈 단자(2330)를 통하여 웨이퍼 페데스탈(1060)에 인가된다. RF 전력 또는접지 전위는 단자(2340)를 통하여 반도체 밀봉 체 전극(1030)(디스크 시일링(1020) 및 실린더형스커트(1010)을 포함하는)에 인가된다. 유도 코일(1040)과 웨이퍼 페데스탈(1060)(예를들어, 도1,5,19 또는 23에 도시된) 또는 공통 RF 전력 공급(예를들어, 도4,18,19 또는 20에 도시된)으로부터거기로의 RF 전력 스플리팅에 별개의 RF 전력를 공급하기 위한 여러 방법이 본 명세서에 도시되어 잇으며, 이 별개의 RF 전력중의 임의의 하나는 도48a의 실시예에 인가될 수 있다.더우기,다양한 유도 코일의 기하학적 구성이 본 명세서에 개시되었으며(예를들어, 도30a, 30b, 30c, 31a, 31b, 31c, 32, 33 또는 34에 도시된), 이들중 임의의 하나는 도48a의 실시예를 수행하는 데채용될 수 있다.

따라서, 도 48a의 실시예는 3개의 독립적인 전극, 즉(a) 웨이퍼 페데스탈(160),(b) 반도체 시일 링(1020) 및 (c) 반도체 스커트(1010)이다. 이들 3개의 전극의 각각은 특정 전극 과 플라즈마간의 요구된 상호 작용에 종속하여, 다른 두 전극 보다 유효영역에서 더 작거나 클 수 있다. 3개 전극중의 하나가 다른 두 전극에 비해 유효영역에서의 증가 또는 감소에 의해, 일 전극에서의 플라즈마 이온 플럭스 및 에너지는 다른 전극에 대해 배분될 수 있다. 상세히는 다른 전극에 비해 전극의 유효 영역에서의 감소는 일 전극에서 플라즈마 이온 플럭스 및 에너지를 증가시킨다. 이것은일 전극과 플라즈마간의 상호작용을 제어하기 위한 또다른 방법을 제공하며, 예를들어, 요구된 전극 플라즈마 상호작용을 달성하는 데 필요한 RF 바이어스 전력 필요조건 및 온도 필요조건을 경감시키는 데 사용될 수 있다. 요구된 전극 플라즈마 상호작용의 한 예로서, 본 발명의 한 모드로 2개 반도체 전극(예를 들면, 상기 스커트(1010)와 상기 시일링(1020))을 포함하는 상기 반도체 밀봉 내부 표면상에 재료의 증착을 제공하는 것이 바람직하다. 그러므로 상기 반도체 전극을 증착

되는 오염물(예를 들면, 중합체 선구물질)로부터 자유롭게 유지함으로써, 상기 전극으로부터 증착 재료의 박편화에 기인하는 웨이퍼 오염은 방지되는 반면, 동시에 상기 전극은 그것이 상기 플라즈마 처리 반응에 유리하게 지속적으로 참여하도록 커버되지않은 체 유지된다. 예를 들면, 상기 전 극은 실리콘 함유 재료가 될 수 있고 상기 플라즈마 처리는 플루오르 함유 실리콘 재료를 사용하는 실리콘 산화물 에칭 처리가 될 수 있는데, 이런 경우에 상기 전극은 플루오르를 제거하기 위해 상기 플라즈마내에 스퍼터링된 실리콘 재료를 제공한다. 어떤 경우에, RF 바이어스 전력 요구 또는 전극 온도 요구의 경감이 다음과 같은 하나의 전극에서의 3가지 파라미터, 즉 (a) 한 전극에 인가된 RF 바이어스 전력, (b) 한 전극의 온도, 및 (c) 다른 전극의 효과적 영역에 관현한 한 전 극의 효과적 영역 중 어떤 하나, 또는 일부, 또는 모두를 조절함으로써 달성될 수 있다. 그러므로, 전극 중 하나의 온도를 최소화하고 상기 한 전극에 인가된 RF 바이어스 전력을 최소화하는 것이 요구된다면-그럼에도 불구하고 한 전극상의 재료의 증착(이를테면 중합체 선구물질)을 방지하면서, 상기 전극의 효과적 영역은 요구된 전극 온도와 전극 RF 바이어스 전력을 보상하도록 한 전극에서의 플라즈마 이온 플럭스 및 에너지를 증가시키기 위하여 감소될 수 있다. 이런 방식으로, 상기 효과적 전극 영역의 선택은 상기 전극과 플라즈마 사이의 요구된 상호 작용을 달성하면서 RF 바이어스 전력과 온도 요구를 경감할 수 있다.

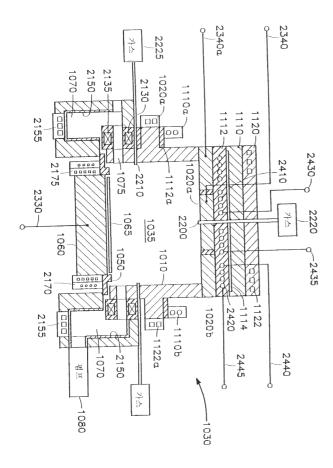

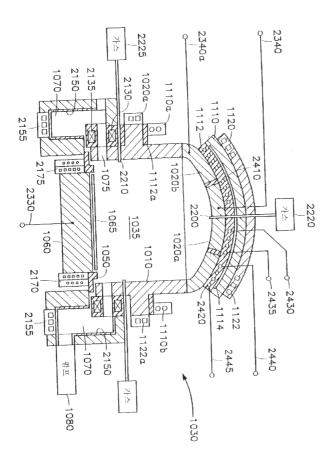

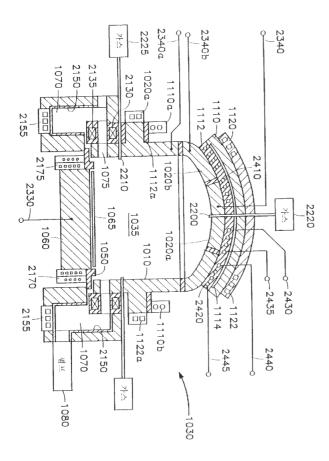

도 48a의 실시예에서, 상기 코일 인덕터(1040)는 전기적으로 개별 내부 및 외부 코일 인덕터로 분할될 수 있다. 예를 들면, 상기 내부 및 외부 코일 인덕터는 내부 및 외부 코일 인덕터(2410과 2420)로서 도 52에 도시된다. 상기 내부 및 외부 코일 인덕터를 개별적으로 구동하는 다양한 방법은 본 명세서에 이미 개시되어 있고(예를 들어 도 6, 16에 도시된 바와 같이), 그것중 어느 하나가 도 48a의 실시예를 수행하는데 사용될 수 있다. 상기 웨이퍼 대 시일링 거리가 작은 특별한경우에, 상기 외부 안테나 코일(2420)을 개별적으로 제어하는 한 장점은 상기 웨이퍼 중앙 상의플라즈마 밀도가 상기 작은 웨이퍼 대 시일링 거리에 기인하여 상기 웨이퍼 주변의 플라즈마 밀도보다 더 낮은 상기 웨이퍼 중앙상의 플라즈마 밀도가 상기 내부 코일 인덕터(2410)에 인가되는 RF플라즈마 소스 전력과 관련하여 상기 외부 코일 인덕터(2420)에 인가된 상기 RF 플라즈마 소스 전력을 감소시킴으로써 상기 웨이퍼 주변의 플라즈마 밀도에 관련하여 증진될 수 있다는 것이다.

도 48a의 실시예는 상기 처리 영역(1035)을 측면적으로 상기 펌핑 환형부(1070)로 배기하는 반면, 도 48b의 실시예는 하향으로 상기 실린더형 스커트(1010)의 축에 대해 평행하게 상기 펌프(1080)로 배기된다. 임의 자석 링(2130a, 2135a)은 상기 처리 영역(1035)으로부터 펌핑 환형부로의 하향 플라즈마 누출을 차단한다. 도 48a의 실시예에서, 플라즈마 누출을 추가로 차단하기 위하여 상기 개구부(1075)는 상대적으로 높은 종횡비를 가지고, 그결과 누출되는 플라즈마 이온 또는 전자는 이들의 통과 완료 이전에 상기 개구부(1075)의 내부 표면에 충돌하려는 경향이 있어 상기 내부 표면에 흡수된다. 플라즈마 누출을 감소하는 다른 형태는 상기 칼라(1050)와 상기스커트(1010) 하부 사이의 통로(1051)를 통과하는 구불구불한 경로이다. 도면에 도시된 바와 같이, 상기 칼라(1050)와 상기 스커트(1010)의 하부는 그 사이를 통과하는 어떤 플라즈마가 상기캡(1051)을 통해 구불구불한 경로를 따라가도록 하는 중첩 배플 식의 균일한 중첩 계단 형태를 가지며, 그결과 그것의 표면과의 플라즈마 충돌 빈도를 증가시킨다.

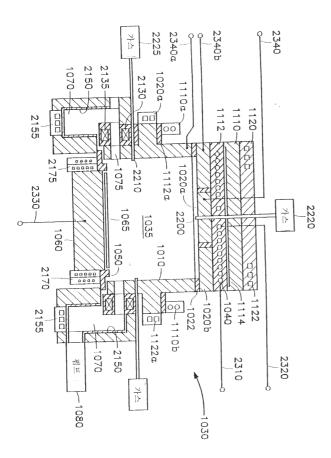

도 48a에서, 상기 실리더형 스커트(1010)는 각각 단자(2340과 2340a)를 통해 각각 개별 RF 전력 소스에 접속될 수 있는 상기 디스크 시일링(1020)으로부터 전기적으로 분리된다. 이것은 상기 웨이퍼 주변에 근접한 상기 플라즈마 조건이 상기 웨이퍼 중앙 근처의 플라즈마 조건에 영향을 미치려고 하는 상기 디스크 시일링(1020)의 상기 단자(2340)에 인가된 상기 RF 전위와 무관하게 상기실린더형 스커트(1010) 상의 상기 단자(2340a)에 인가되는 개별 RF 전위에 의해 제어될 수 있게한다. 상기 반도체 윈도우 밀봉체의 2개 전기적 개별 섹션상의 RF 전위를 제어하는 여러 가지 방법은 본 명세서(예를 들면, 도 42, 46, 10, 11 또는 12에 도시된 바와 같이)에 개시되어 있고, 그것 중 하나가 도 48a의 실시예를 수행하는데 사용될 수 있다.

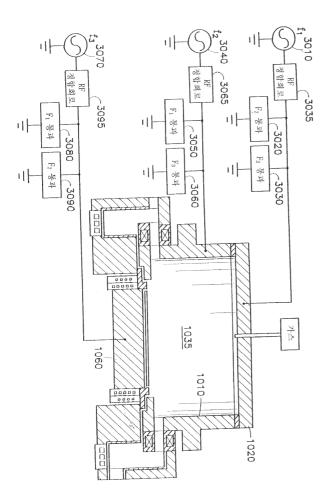

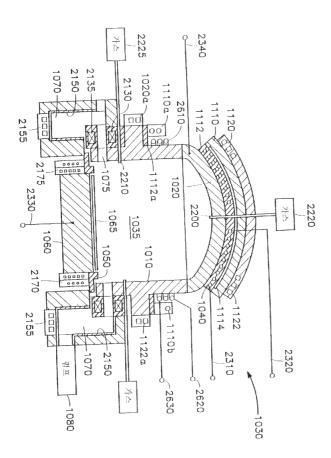

상기 스커트(1010), 상기 시일링(1020) 및 상기 웨이퍼 페데스탈(1060)은 개별 전국으로서 사용되어질 수 있고 ,이들중 하나는 다른 것에 관련하여 전기적으로 접지될 수 있는 반면, 접지되지않은 것들은 동일하거나 서로 다른 전력 소스로 구동될 수 있다. 예를 들면, 도 48c에 도시된 바와 같이, 주파수(f1)의 제 1 RF 전력 소스(3010)는 상기 반도체 시일링 전국(1020)에 결합되는 반면, 상기 필터(3020과 3030)는 RF 임피던스 정합 회로(3035)에 주파수( $f_2$ 와  $f_3$ )로 RF 전력이 다시 결합하는 것을 방지한다. 제 2 RF 전력 소스(3040)는 상기 반도체 시일링 스커트(1010)에 결합되는 반면, 상기 필터(3050과 3060)는 RF 임피던스 정합 회로(3065)에 주파수( $f_1$ 과  $f_3$ )로 RF 전력이 다시 결합하는 것을 방지한다. 제 3 RF 전력 소스(3070)는 상기 웨이퍼 페데스탈(1060)에 결합되는 반면, 상기 필터(3080과 3090)는 임피던스 정합 회로(3095)에 주파수( $f_1$ 과  $f_2$ )로 RF 전력이 다시 결합하는 것을 방지한다. 도 48c의 실시예는 3개 엘리먼트(1020, 1010 또는 1060) 중 어느 하나를 접지함으로써 요구된 바와 같이 변형될 수 있다.

2개 개별 실리콘 피스(1010, 1020)로서 상기 반도체 밀봉체(1030)를 형성하는 것은 제조 용이의 부가적 장점을 제공하며, 그결과 바람직하다.

도 49는 상기 스커트(1010)와 시일링(1020)이 서로 전기적으로 절연되지않고 단일 일체형 모노리틱 실리콘 피스로도 형성될 수 있다는 점만 제외하고 도 48a의 실시예에 대응하는 실시예를 도시한다.

도 50은 상기 디스크형 반도체 시일링(1020)이 내부 중앙 디스크부(1020a)와 상기 실린더형 스커트(1010)가 하향으로 연장하는 주변 환형부(1020b)로 분할되는 방법을 설명한다. 도 49의 실시예에서와 같이, 상기 웨이퍼 중앙과 웨이퍼 에지에서의 플라즈마 조건은 상기 개별 단자(2340과 2340a)에 각각 인가되는 개별 RF 바이어스 신호에 의해 독립적으로 제어될 수 있다. 도 48a의 실시예를 참조하여 이미 참조된 상기 반도체 윈도우 밀봉체(1030)의 개별 섹션을 제어하기 위한 이미 개시된 여러 가지 방법 중 어느 하나가 도 50의 실시예를 수행하는데 사용될 수 있다.

도 51은 상기 반도체 윈도우 밀봉체(1030)가 (1) 상기 시일링(1020)의 내부 디스크부(1020a), (2) 상기 시일링(1020)의 외부 환현부(1020b) alc (3) 상기 환형부(1020b)로부터 분리된 상기 스커트(1010)를 포함하는 3개 전기적 개별부로 분할되는 방법을 설명한다. 3개 개별 RF 신호는 상기 3개 부분에, 즉 상기 단자(2340)를 통해 상기 내부 디스크부(1020a)에, 상기 단자(2340a)를 통해 상기 스커트(1010)에, 그리고 상기 단자(2340b)를 통해 상기 외부 환형부(1020b)에 인가될수 있다.

도 52는 상기 도 50의 실시예가 상기 웨이퍼 중앙과 상기 웨이퍼 에지상에서 플라즈마 조건의 개별적 제어를 위해 개별적인 내부 및 외부 유도코일(2410, 2420)과 조합될 수 있는 방법을 설명한다. 상기 내부 및 외부 유도 코일(2410, 2420)에 대한 단자(2430, 2435와 2440, 2445)는 각각 개별 RF 전력 공급원에 의해 또는 공통 전원 공급원으로부터의 스플리팅 RF 전력에 의해 구동될 수있다. 상기 반도체 윈도우 밀봉체(1030)의 개별적으로 구동된 부분과 조합하여 상기 내부 및 외부 유도 코일(2410, 2420)에 전력을 인가하는 여러 가지 방법은 본 명세서에 이미 개시되어 있고(예를 들면, 도 42, 43 또는 46에서와 같은), 그중 어떤 하나가 도 52의 실시예를 수행하는데 사용될 수 있다.

도 53은 도 51의 실시예가 상기 개별 내부 및 외부 코일 인덕터(2410, 2420)과 조합될 수 있는 방법을 설명한다.

도 54는 도 48a의 실시예가 도 10의 실시예와 유사한 방식으로 상기 반도체 스커트(1010) 둘레에 감겨지는 실린더형 측면 코일(2610)과 조합될 수 있는 방법을 설명한다. 플라즈마 RF 소스 전력은 단자(2620, 2630)를 통해 상기 측면 코일(2610)에 인가된다. 바람직하게, 상기 상부코일(1040)과 상기 측면 코일(2610)은 상기 플라즈마내의 표피 깊이의 적어도 약 2배와 동일한 거리만큼 분리된다.

임으로, 상기 시일링(1020) 위에 놓이는 상기 코일 인덕터(1040)는 도 7, 8 및 9의 실시예와 유사하게 상기 측면 코일(2610)을 위해 제거될 수 있다. 이런 경우에, 단지 상기 스커트(1010)는 실린더형 반도체 윈도우 밀봉체(1030)를 제공하는 반도체 재료가 될 것이 요구되는 반면, 상기 시일링(1020)은 절연체(이를테면, 실리콘 질화물)가 될 수 있다. 상기 실린더형 반도체 윈도우 전극, 상기 측면 코일 및 상기 웨이퍼 페데스탈에 개별적으로 RF 전력을 인가하기 위해 도 7, 8 또는 9의 기술중 어느 하나가 도 54의 실시예를 수행하는데 사용될 수 있다.

도 55는 시일링(1020)과 스커트(1010)로 분할된 반도체 윈도우 밀봉체(1030)를 가지는 도 48a의 실시예가 상기 스커트(1010) 둘레에 감겨진 상기 실린더형 측면 코일(2610)과 조합될 수 있는 방법을 설명한다. 상기 개별 시일링 섹션과 상부 및 측면 코일 인덕터에 RF 전력을 인가하는 도 10, 11 및 12에 도시된 방법 중 어느 하나가 도 55의 실시예를 수행하는데 사용될 수 있다.

도 56은 상기 스커트(1010)를 갖는 내부 디스크부(1020a)와 외부 환형부(1020b)로 분할되는 반도체 윈도우 밀봉체(1030)를 가지는 도 50의 실시예가 상기 스커트(1010) 둘레에 감겨진 상기 측면코일(2610)과 조합될 수 있는 방법을 설명한다. 상기 개별 시일링 섹션과 상부 및 측면 코일 인덕터에 RF 전력을 인가하는 도 10, 11 및 12에 도시된 방법 중 어느 하나가 도 56의 실시예를 수행하는데 사용될 수 있다.

도 57은 내부 디스크부(1020a), 외부 환형부(1020b) 및 스커트(1010)로 분할되는 반도체 윈도우 밀봉체(1030)를 가지는 도 51의 실시예가 상기 스커트(1010) 둘레에 감겨진 상기 측면 코일(2610) 과 조합될 수 있는 방법을 설명한다.

도 58은 도 48a의 실시예의 상기 시일링(1020)이 돔 형태를가지도록 변형될 수 있는 방법을 설명한다. 바람직하게, 상기 돔 형태는 돔의 반경이 에지로부터 중앙으로 증가하는 다중 반경 돔 형태이다. 바람직하게, 꼭 필요한 것은 아니지만, 상기 시일링 코일 인덕터(1040)는 상기시일링(1020)의 돔 형태와 일치된다. 유사하게, 도 59는 도 49의 실시예의 상기 시일링(1020)이돔 형태를 가지도록 변형될 수 있는 방법을 도시하고, 도 60은 도 50의 실시예의 상기시일링(1020)이돔 형태를 가지도록 변형될 수 있는 방법을 도시하고, 도 61은 도 51의 실시예의상기시일링(1020)이돔 형태를 가지도록 변형될 수 있는 방법을 도시하고, 도 61은 도 51의실시예의상기시일링(1020)이돔 형태를 가지도록 변형될 수 있는 방법을 도시하고, 도 62는 도 52의실시예의상기시일링(1020)이돔 형태를 가지도록 변형될 수 있는 방법을 도시하고, 도 63은 도 53의실시예의상기시일링(1020)이돔 형태를 가지도록 변형될 수 있는 방법을 도시하고, 도 64는 도 54의실시예의상기시일링(1020)이돔 형태를 가지도록 변형될 수 있는 방법을 도시하고, 도 65은 도 55의실시예의상기시일링(1020)이돔 형태를 가지도록 변형될 수 있는 방법을 도시하고, 도 65은 도 55의실시예의상기시일링(1020)이돔 형태를 가지도록 변형될 수 있는 방법을 도시하고, 도 66은도 56의실시예의상기시일링(1020)이돔 형태를 가지도록 변형될 수 있는 방법을 도시하고, 도 66은도 56의실시예의상기시일링(1020)이돔 형태를 가지도록 변형될 수 있는 방법을 도시하고, 도 66은도 56의실시예의상기시일링(1020)이돔 형태를 가지도록 변형될 수 있는 방법을 설명한다.도 68는 이전에도 48a의상기사일리(1020)이돔 형태를 가지도록 변형될수 있는 방법을 설명한다.도 68a는 이전에도 48a의상기사업자 자식 링(2130, 2135)와관련하여참조된자기제한형태의제1실시예의단면도이다.도 68a에서,상기자석링은서로대향하는반대자극으로한쪽끝과다른한쪽끝을 있게방향지어진다.도 68c에서,상기반대자극은방대상의자극이병절정렬이되도록반대방향으로한쪽 측면과다른 측면을 있게방향지어진다.도 68c에서,상기반대자극은방대상의자극이라의 보다는유사한자극이라기보다는 유사한자극이라의 된다는 점안제외하면 각각도 68b와 68c에 대응한다.상기슬릿 밸브(1075)또는다른 등론를통과하는 직선 경로로부터 이온의필수 위회로를제공하는다른배열이본 발명을수행하는데제공될수있다.

도 48a-68c의 실시예가 서로 다른 형태의 시일링과 스커트(예를 들면, 디스크와 실린더 또는 디스크와 돔 중 어느하나)로 참조하여 개시되었더라도, 이들은 반구형, 다중 반경 돔, 실린더형, 원추형, 절두 원추형 등을 포함하는 곡선의 회전에 의해 형성되는 동일한 형태 또는 서로 다른 형태로이루어질 수 있다.

앞서 말한 설명이 회전 가능한 대칭적 유도 안테나에 기준하여 이루어졌더라도, 이런 안테나는 본 발명을 수행하는데 요구되지 않고, 상기 안테나는 RF 전력을 플라즈마에 유도적으로 결합할 수 있 는 어떤 다른 형태로 이루어질 수 있다. 그러므로, 상세한 설명과 첨부된 청구 범위에 사용되는 상기 유도 안테나는 적어도 상기 플라즈마에 RF 전력을 유도적으로 결합하는 상기 플라즈마에 인 접한 임의 전류 운반 엘리먼트이며, 그러므로 코일이 될 필요는 없고 상기 반응기 챔버 시일링에 인접하게 배치될 필요도 없지만, 상기 챔버 측벽과 같은 어떤 다른 적당한 위치에 인접하게 될 수 있다. 사실상, 도 69의 실시예에서와 같이 유도 안테나는 완전히 불필요하게 될 수 있다. 도 69 는 상기 유도 안테나(1040)가 제거되어지고 도 48a의 실시예에 대응한다. 대신에, RF 전력은 상 기 반도체 시일링(1020)과 상기 웨이퍼 페데스탈(1060)을 포함하는 한쌍의 전극으로부터 상기 플 라즈마에 용량성 결합된다.

도 70은 도 48a의 실시예의 상기 시일링(1020)이 반구형 형태를 가지도록 변형될 수 있는 방법을 설명한다. 상기 반구형 형태는 상기 돔의 반경이 에지로부터 중앙까지 동일한 단일 반경 돔 형태 이다. 바람직하게, 꼭 필요한 것은 아니지만, 상기 시일링 코일 인덕터(1040)는 시일링(1020)의 반구형 형태와 일치한다. 유사하게, 도 71은 도 49의 실시예의 상기 산기 시일링(1020)이 반구형 형태로 변형될 수 있는 방법을 설명한다. 마찬가지로, 도 72는 도 50의 실시예의 상기 시일링(1020)이 반구형 형태로 변형될 수 있는 방법을 설명하고, 도 73은 도 51의 실시예의 상기 시일링(1020)이 반구형 형태로 변형될 수 있는 방법을 설명하고, 도 74은 도 52의 실시예의 상기 시일링(1020)이 반구형 형태로 변형될 수 있는 방법을 설명하고, 도 75은 도 53의 실시예의 상기 시일링(1020)이 반구형 형태로 변형될 수 있는 방법을 설명하고, 도 76은 도 54의 실시예의 상기 시일링(1020)이 반구형 형태로 변형될 수 있는 방법을 설명하고, 도 77은 도 55의 실시예의 상기 시일링(1020)이 반구형 형태로 변형될 수 있는 방법을 설명하고, 도 78은 56의 실시예의 상기 시일링(1020)이 반구형 형태로 변형될 수 있는 방법을 설명하며, 도 79은 도 57의 실시예의 상기 시일링(1020)이 반구형 형태로 변형될 수 있는 방법을 설명한다.

상기 설명이 영구 자석이 되는 플라즈마 제한 자석에 기준하여 이루어지더라도, 전자석이 플라즈마 제한 자석으로서 사용될 수 있다.

도 48a-79의 실시예가 플라즈마 에칭 반응기에 기준하여 개시되었더라도, 또한 본 발명은 플라즈마 증착 반응기, 이를테면 화학 기상 증착(cVd) 플라즈마 반응기에 사용될 수 있다. 이런 경우에, 상기 처리는 웨이퍼 뿐만 아니라 챔버 벽에 증착이 발생하는 식으로 수행될 수 있다. 선택적으로, 상기 벽은 재료가 웨이퍼 상에 증착되는 동안에도 챔버 내부 벽상의 증착 축적물이 없도록 충분한 RF 전력으로 바이어싱될 수 있다. 이것은 특히 실리콘 산화물 cVd 플라즈마 반응기와의 상당한 장점을 제공한다. 이것은 본 발명 없이 상기 반응기의 내부 벽이 주기적으로 세정되기 때문이다. 이런 세정 동작은 실리콘 이산화물 에칭이 매우 느리기 때문에 표면 온도가 충분히 화학적 에칭 임계 온도를 초과하지 않는다면 플루오르 함유 세정 가스에서 조차 어렵다.

선택적으로, 본 발명은 세정 가스(예를 들면, 플루오르 함유 가스)를 챔버내로 유입하고, 각각의 반도체 밀봉 엘리먼트에 RF 전력을 인가하며, 반도체 밀봉 엘리먼트의 온도를 적당히 조절함으로써 후처리 자기 세정 cVd 반응기 챔버와 같이 기능할 수 있다. 이런 다른 실시예에서, 제조 웨이퍼의 cVd 처리동안 상기 반응기는 본 발명의 어떤 형태를 사용하지 않는 일반적 cVd 반응기의 방식으로 동작될 수 있다. 이후에, 세정 동작이 본 발명의 사용된 모든 형태로 수행된다. 이런 세정동작 동안, 상기 반도체 밀봉체의 내부 표면에 증착되는 오염물이 에칭되는 비율은 상기 표면온도를 상승시킬 필요없이 본 발명에 따른 반도체 밀봉체에 RF 바이어스 전력을 인가함으로써 증진된다.

상기 반도체 밀봉체의 형태는 특별한 응용의 유일한 요구에 부합하도록 숙련자에 의해 변형될 수 있다. 예를 들면, 도 48a와 48b의 실시예에서, 상기 실리콘 스커트(1010)는 상기 웨이퍼 주변으로부터 상기 스커트(1010)의 수직면까지의 방사 거리를 증가하기 위해 L형 단면(상기스커트(1010)의 반도체 실린더부와 상기 반도체 환형 푸트(1011)에 의해 형성된)을 가진다. 다른도면의 실시예에서 상기 스커트(1010)의 내부 표면은 완전히 직선이고, 그러므로 상기 웨이퍼 주변에 더 가깝다. 상기 반도체 스커트(1010)의 형태에서의 변형은 설명된 실시예 중 어느하나로수행될 수 있다.

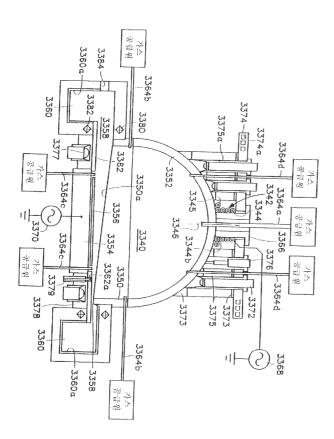

# 다중 반경 온도 구역 및 동일 형태가 아닌 코일

도 80은 다수의 방사상으로 접지되고 온도 제어된 구역, 다수의 방사상 대칭적 유도 코일을 갖는 돔형 또는 반구형 반도체 윈도우 전극 시일링을 가지는 플라즈마 반응기를 도시하는데, 상기 유도 코일은 상기 시일링 형태와 일치하지 않는다. 도 80에서, 상기 실린더형 챔버(3340)는 상기 측벽(3350)과 시일링(3352)이 단일 피스의 재료, 이를테면 실리콘으로 구성되도록 상기 측벽(3350)과 일체형으로 형성된 실린더형 측벽(3350)과 돔 또는 반구형 시일링(3352)으로 이루어 진다. 그러나, 본 발명은 이후에 개시되는 바와 같이 개별 피스로서 형성된 상기 측벽(3350)과 시일링(3352)을 사용하여 수행될 수 있다. 일반적으로, 상기 솔레노이드(3342)의 수직 피치(예를 들면, 그것의 수평 폭에 의해 분할된 그것의 수직 높이)는 상기 시일링(3352)의 수직 피치를 초과한다. 적어도 바람직한 실시예에서, 이것을 위한 목적은 상기 안테나 대칭 축 근처의 안테나의 유도에 집중된다. 상기 시일링의 피치를 초과하는 피치를 가지는 솔레노이드는 여기에서 동일 형태가 아닌 솔레노이드로서 참조되는데, 일반적으로 그것의 형태가 상기 시일링의 형태와 일치하지 않으며, 특히 그것의 수직 피치가 상기 시일링의 수직 피치를 초과한다는 것을 의미한다. 2차원 또는 평면 시일링은 제로의 수직 피치를 가지는 반면, 3 차원 시일링은 제로가 아인 수직 피치를 가진다.

상기 챔버(3340)의 하부에 있는 페데스탈(3345)는 처리 동안 제품 지지면에서 평면 제품(3356)을 지지한다. 상기 제품(3356)은 전형적으로 반도체 웨이퍼이고 상기 제품 지지면은 일반적으로 웨 이퍼 또는 제품(3356)의 평면이다. 상기 챔버(3340)는 환형 통로(3385)를 통해 상기 챔버(3340) 의 하부를 둘러싸는 펌핑 환형부(3360)으로 펌프(도면에 도시 안됨)에 의해 진공화된다. 상기 펌 핑 환형부의 내부는 대체가능한 금속 라이너(3360a)로 라이닝될 수 있다. 상기 환형 통로(3358)는 상기 실린더형 측벽(3350)의 상기 하부 에지(3350a)와 상기 페데스탈(3354)을 둘러싸는 평면링(3362)에 의해 한정된다. 처리 가스는 다양한 가스 공급장치 중 어떤 하나 또는 모두를 통해상기 챔버(3340)내로 공급된다. 상기 제품 중앙 근처의 처리 가스 흐름 속도를 제어하기 위하여,중앙 가스 공급장치(3364a)는 상기 제품(3356)의 중앙(또는 상기 제품 지지면 근처의 제품 중앙)을 향해 하향으로 연장될 수 있다. 상기 제품 주변 근처(또는 상기 제품 지지면 주변의 근처)의가스 흐름을 제어하기 위하여,상기 중앙 가스 공급장치(3364a)와 독립적으로 제어될 수 있는 다수의 방사형 가스 공급장치(3364b)가 상기 측벽(3350)으로부터 상기 제품 주변(또는 상기 제품 지지면 주변)을 향해 방사상으로 내부로 연장되고, 또는 베이스 축방향 가스 공급장치(3364c)가 상기 제품 주변을 향해 상기 페데스탈(3354)의 근처로부터 상향으로 연정되고, 또는 시일링 축방향가스 공급장치(3364d)가 상기 시일링(3352)으로부터 상기 제품 주변을 향해 하향으로 연장될 수 있다. 상기 제품 중앙 및 주변에서의 에칭율 및/또는 중합체 증착율은 상기 제품 중앙 및 주변을향하는 처리 가스 흐름 속도를 각각 상기 중앙 가스 공급장치(64a)와 상기 외부 가스공급장치(3364b-d) 중 어느 하나를 통해 제어함으로써 상기 제품에 걸쳐 더욱 방사상으로 균일한 에칭율 분포를 얻기 위하여 서로에 관련하여 개별적으로 조절될 수 있다. 이런 본 발명의 특징은 상기 중앙 가스 공급장치(3364a)와 단지 하나의 주변 가스 공급장치(3364b-d)로 수행될 수 있다.

상기 솔레노이드 코일 안테나(3342)는 상기 중앙 가스 공급장치(3364)를 둘러싸는 하우징(3366) 둘레에 감겨진다. 플라즈마 소스 RF 전력 공급원(3368)은 상기 코일 안테나(3342)의 양단에 접속되고 바이어스 RF 전력 공급원(3370)은 상기 페데스탈(3354)에 접속된다.

상기 시일링(3352)의 중앙 영역에 대한 오버헤드 코일 안테나(3342)의 제한은 차지되지않은 상기 시일링(3352)의 상부 표면의 상당한 부분을 남겨서 다수의 방사 가열기(3372), 이를테면 텅스텐 할로겐 램프와 냉각제 통로(3374a)를 갖는 구리 또는 알루미늄으로 형성될 수 있는 수냉식 냉각 플레이트(3374)를 포함하는 온도 제어 장치와 직접 접촉하기에 유용하다. 상기개별 가열기(3372) 는 다수의 그룹을 형성하는데, 각각의 그룹은 주변적으로 상기 시일링의 중앙으로부터 특정 반경 을 따라 배열된다. 상기 가열기는 상기 전체 시일링이 단일 온도 제어 구역을 구성하도록 서로 제어될 수 있다. 그러나, 상기 가열기(3372)의 각 방사 그룹은 모든 다른 그룹으로부터 개별적으 로 제어될 수 있고, 그결과 상기 시일링은 상기 제품 또는 웨이퍼 표면에서 처리 균일성을 최적화 하기 위해 다르게 형성될 수 있는 온도를 가지는 다수의 환형 온도 제어 구역으로 분할된다.

바람직하게 상기 냉각제 통로(3374a)는 상기 안테나 또는 솔레노이드(3342)의 전기적 부하 감소를 방지하도록 높은 열전도성을 가지지만 낮은 전기 저항성을 가지는 공지된 다양한 냉각제를 포함한다. 상기 냉각 플레이트(3374)는 상기 시일링(3352)의 일정한 냉각을 제공하는 반면, 상기 방사가열기(3372)의 최대 전력은 필요하다면 상기 냉각 플레이트(3374)에 의한 냉각을 압도할 수 있도록 선택되어 상기 시일링(3352)의 민감하고 안정된 온도 제어를 용이하게 한다. 상기가열기(3372)에 의해 조사되는 큰 시일링 영역은 온도 제어의 더 큰 균일성과 효율성을 제공한다(방사 가열은 본 발명의 수행에 필수적으로 요구되지 않으며, 이후에 기술되는 바와 같이 숙련자는전기적 가열 엘리먼트 사용을 선택할 수 있다). 상기 시일링(3352)이 실리콘이라면, 1996년 2월 2일 제출된 케니스 에스. 콜린에 의한 계류중인 미국 출원 일련번호 제08/597,577호에 개시된 바와 같이, 상기 시일링에 걸친 온도 제어의 균일성과 효율성을 증가함으로써 얻어질 상당한 장점이었다. 특히, 중합체 선구물질과 에천트 선구물질 처리 가스(예를 들면, 플루오르)가 사용되고 상기 에천트(예를 들면, 플루오르화 탄소)가 제거되어야 하는 경우에, 상기 전체 시일링(3352)에 걸친 중합체 증착율 및/또는 상기 시일링(3352)이 플루오르 에천트 제거 재료(실리콘)을 상기 플라즈마내로 공급하는 속도는 상기 온도 제어 가열기(3372)와 상기 시일링(3352)의 접촉 영역을 증가시킴으로써 양호하게 제어될 수 있다. 상기 솔레노이드 안테나(3342)는 상기 솔레노이드 권선(3344)이 상기 시일링(3352)의 중앙 축에 집중되기 때문에 상기 시일링(3352)상의 이용 가능한 열적접촉 영역을 증가시킨다.

열적 접촉을 위한 상기 시일링(3352)상의 이용 가능한 영역의 증가는 상기 시일링(3352)상에 안착되는 하부 표면 및 상기 냉각 플레이트(3374)를 지지하는 상부 표면을 가지는 높은 열전도성 원환체(3375)(알루미늄 질화물, 알루미늄 산화물 또는 실리콘 질화물과 같은 세라믹 또는 저도핑되거나 도핑되지 않은 실리콘 같은 비-세라믹으로 형성되는)에 의한 바람직한 실행에 이용된다. 상기원환체(3375)의 특징 중 하나는 그것이 상기 냉각 플레이트(3374)를 상기 솔레노이드(3342)의 상부상에 잘 변위시킨다는 것이다. 이런 특징은 실질적으로 마찬가지로 상기 냉각 플레이트(3374)의 전도 평면에 가까운 근처로부터 상기 솔레노이드(3342)까지 얻어지는 상기 솔레노이트(3342)와 상기 플라즈마 사이의 유도결합의 감소를 감소 또는 거의 제거한다. 이런 유도 결합의 감소를 방지하기 위하여, 상기 냉각 플레이트(3374)와 상기 솔레노이드(3342)의 정부 권선 사이의 거리가적어도 상기 솔레노이드(3342)의 전체 높이의 실질적 단편(예를 들어, 절반)이 되는 것이 바람직하다. 상기 원환체(3375)를 통해 연장하는 다수의 축방향 홀(3375a)은 2개 동심원을 따라 배치되고 상기 다수의 방사 가열기 또는 램프(3372)를 홀딩하여 이들이 직접 상기 시일링(3352)를 조사하도록 한다. 가장 큰 램프 효율을 위하여, 상기 홀 내부 표면은 반사 층(예를 들면, 알루미늄하는로 라이닝될 수 있다. 상기 중앙 가스 공급장치(64a)는 특별한 반응기 디자인과 처리 조건에 의존하여 방사 가열기에 의해 교체될 수 있다. 상기 시일링 온도는 램프 가열기(3372)에 의해 자지되지않는 상기 홀(3375a) 중 하나를 통해 연장하는 열전쌍(3376)과 같은 센서에 의해 감지될수 있다. 양호한열적 접촉을 위하여, 봉소 질화물로 주입된 높은 열전도성 엘라스토머(3373), 이를테면 실리콘 고무가 상기 세라믹 원환체(3375)와 상기 구리 냉각 플레이트(3374) 사이 및 상기세라믹 원환체(3375)와 상기 실리콘 시일링(3352) 사이에 배치될 수 있다.

이미 참조된 계류중인 출원에 개시된 바와 같이, 상기 챔버(3340)는 모든 반도체 챔버가 될 수 있고, 이런 경우에 상기 시일링(3352)과 상기 측벽(3350)은 둘다 반도체 재료, 이를테면 실리콘이다. 이미 참조된 계류중인 출원에 개시된 바와 같이, 상기 시일링(3352) 또는 상기 벽(3350) 중어느 한쪽의 온도 제어, 및 이들에 인가된 RF 바이어스 전력은 상기 플라즈마에 플루오르 제거 선

구물질 재료(실리콘)를 공급하는 범위, 또는 선택적으로 중합체로 코팅되는 범위를 조정한다. 상기 시일링(3352)의 재료는 실리콘에 제한되지 않지만, 다른 대안으로 실리콘 카바이드, 실리콘 이산화물(석영), 실리콘 질화물 또는 세라믹이 될 수 있다.

이미 참조된 계류중인 출원에 개시된 바와 같이, 상기 챔버 벽 또는 시일링(3350, 3352)는 플루오르 제거 재료의 소스로서 사용될 필요는 없다. 대신에, 일회용 실리콘 부재가 상기 챔버(3340) 내부에 배치될 수 있고, 그위의 중합체 응축을 방지하기 위해 충분히 높은 온도로 유지되어 실리콘 재료가 플루오르 제거 재료로서 상기 플라즈마내의 실리콘 부재로부터 제거될 수 있도록 한다. 이런 경우에, 상기 벽(3350)과 시일링(3352)은 실리콘이 될 필요는 없고, 또는 이들이 실리콘인경우 이들이 소모되는 것을 방지하기 위하여 플라즈마로부터 중합체로 코팅되도록 이들은 중합체 응축 온도(및/또는 중합체 응축 유 바이어스 임계값) 근처 또는 미만의 온도로 유지될 수 있다. 상기 일회용 실리콘 부재는 임의 적당한 형태를 취할 수 있지만, 예시된 실시예에서 상기 일회용실리콘 부재는 상기 페데스탈(3354)을 둘러싸는 환형 링(3362)이다. 바람직하게, 상기 환형링(3362)은 고순도 실리콘이고 그것의 전기적 또는 광학적 특성을 변경하기 위하여 도핑될 수 있다. 상기 플라즈마 처리에서 그것의 유리한 참여(예를 들면, 플루오르 제거동안 플라즈마내의 실리콘 재료의 기여)를 보장하기에 충분한 온도로 상기 실리콘 링(3362)을 유지하기 위하여, 다수의방사(예를 들면, 텅스텐 할로갠 램프) 가열기(3377)가 석영 윈도우(3378)를 통해 상기 실리콘링(3362)을 가열하는 상기 환형링(3362) 하부에 배열된다. 이미 참조된 계류중인 출원에 개시된바와 같이, 상기 가열기(3377)는 광학 고온계 또는 플루오르-광학 프로브와 같은 원격 센서가 될수 있는 온도 센서(3379)에 의해 감지된 상기 실리콘링(3362)의 측정된 온도에 따라 제어된다. 상기 센서(3379)는 상기 실리콘링(3362)의 열적 방사율의 온도 의존성 변화를 차단하기 위해 상기 링(3362)내의 매우 깊은 홀(3362a)내로 부분적으로 연장되며, 그것은 더욱 신뢰가능한 온도 취용을 위한 그레이-바디 방사기 처럼행동하는 것으로 믿어진다. 서로 다른 방사 위치에 다수의 센서가 제공될 수 있다.

이미 참조된 미국 출원 일련번호 제08/597,577호에 개시된 바와 같이, 모든 반도체 챔버의 장점은 플라즈마가 금속과 같은 재료를 생성하는 오염물과 접촉하지 않는다는 것이다. 이런 목적을 위하여, 상기 한형 통로(3358)에 인접한 플라즈마 제한 자석(3380, 3382)은 상기 펌핑 환형부(3360)내로의 플라즈마 흐름을 방지 또는 감소시킨다. 이의 중합체 선구물질 및/또는 활성 종이 상기 펌핑 환형부(3360)에 계속 진입하는 정도까지, 상기 교체가능한 내부 라이너(3360a)상의 임의의 얻어지는 중합체 또는 오염 증착물은 예를 들어 이미 참조된 계류중인 출원에 개시된 바와 같이 중합체 응축 온도 미만의 온도로 상기 라이너(3360a)를 유지함으로써 상기 플라즈마 챔버(3340)로의 재진입이 방지될 수 있다.

상기 펌핑 환형부(3360)의 외부 벽을 관통하는 물 슬릿 밸브(3384)는 물 진입과 배출을 도모한다. 상기 챔버(3340)와 상기 펌핑 환형부(3360) 사이의 환형 통로(3358)는 비대칭 펌프의 위치와 더욱 대칭적인 챔버 압력의 분배를 형성하도록 실린더형 측벽(3350)의 하부 에지의 경사에 의해 상기 웨이퍼 슬릿 밸브(3384)에 인접하여 가장 크고 반대쪽에서 가장 작다.

상기 챔버 중앙축(3346) 근처의 최대 인덕턴스는 수직으로 적층된 솔레노이드 권선(3344)에 의해 달성된다. 도시된 바와 같이, 상기 수직 적층 권선(3344)의 외부에 있지만 하부 솔레노이드 권선(3344a)의 수평면에 있는 다른 권선(3345)이 부가될 수 있으며, 상기 제공된 추가 권선(3345) 은 상기 하부 솔레노이드 권선(3344a)에 근접한다.

본 발명의 한 특징은 상기 웨이퍼 표면 근처의 플라즈마내에서 에천트 선구물질과 중합체 증착 선구물질에 대한 방사 밀도 분포의 조절이다. 상기 조절은 상기 웨이퍼에 걸쳐 더욱 균일한 에천트와 중합체 증착 선구물질의 방사 분포, 상당한 장점을 형성할 수 있다. 상기 조절은 상기 내부및 외부 가스 흐름 인렛(예를 들면, 도 80의 각각의 상기 내부및 외부 가스 흐름 인렛(3364a, 3363d))을 통해 흐름 속도를 차동적으로 제어하고, 시일링 가열기의 내부및 외부 그룹(예를 들면, 도 80의 각각의 내부및 외부 그룹(예를 들면, 도 80의 각각의 내부및 외부 가열기 램프(3376, 3372))에 대한 전력을 차동적으로 제어하고, 상기 내부및 외부 오버헤드 안테나 코일(예를 들면, 도 42-47의 각각의 내부및 외부 오버헤드안테나 코일(175, 180))에 인가되는 RF 전력을 차동적으로 조절하며, 및/또는 상기 시일링의 내부및 외부 섹션(예를 들면, 도 42-47의 각각의 내부및 외부 시일링 섹션(230a, 230b))에 인가되는 RF 전력을 차동적으로 조절하여, 이런 모든 조절 가능한 특징은 상기 내부및 외부 시일링 섹션(230a, 230b)와 도 47의 내부및 외부 안테나코일(175, 180)이 도 80의 상기 시일링(3352)과 안테나(3342)를 대신하도록 함으로써 도 80의 반응기내에 조합될 수 있다.

접지에 접속된 전도적 후면의 존재(이를테면 도 25a-c의 후면(400))는 분석으로 추정되고, 그 예는 본 명세서 이전의 바이어스 RF 소스의 귀환 경로의 손실없는 실리콘 시일링 부가에 개시되어 있다. 그러나, 현재 바람직한 실시예에서, 그런 후면은 사용되지 않는다. 대신에, 상기 반도체원도우 전극 또는 시일링(110)의 에지가 접지 또는 RF 바이어스 소스 중 어느 한쪽에 접속된다. 하나의 장점은 더 큰 시일링(110)의 영역이 열제어에 유용하다는 것이다. 이런 변화는 상기 분석과 이미 주어진 예에 관련하여 상기 시일링(110)의 삽입 임피던스를 증가시키고, 그결과 R<sub>slab</sub>/Re(Z)는 상기 시일링(110) 통해 방사상으로 흐르는 귀환 전류를 요구함으로써 0.004로부터 0.017로 증가된다. 그러나, 이런 비율은 여전히 바람직한 실시예에 맞지않을 만큼 작게 유지된다. 이런 증가는 바람직하게 그것의 에지에서 그것의 접속부(접지 또는 RF 바이어스 소스 중 어느 하나에)에 기인할 수 있는 상기 시일링(110)에 걸친 방사 전압 강하에 기인한다. 상기 방사전압 강하는 약 3.3%로 아주 작으며, 그것은 R<sub>slab</sub>/Re(Z)이 바람직한 실시예에서조차 상대적으로 작게 유지되는 이유이다.

이상에서는 본 발명의 양호한 일 실시예에 따라 본 발명이 설명되었지만, 첨부된 청구 범위에 의해 한정되는 바와 같은 본 발명의 사상을 일탈하지 않는 범위 내에서 다양한 변형이 가능함은 본

발명이 속하는 기술 분야의 당업자에게는 명백하다.

#### 발명의 효과

하나의 반응기에 병렬 플레이트 전극 용량성 결합 플라즈마 반응기의 이점과 오버헤드 평면 유도 안테나를 가진 유도 결합 플라즈마 반응기의 이점을 결합시켜서 플라즈마 공정 윈도우를 확장시키 도록 전체 웨이퍼 표면을 균일하게 플라즈마 처리하는 유도 결합 병렬 플레이트 전극 플라즈마 반 응기를 제공한다.

### (57) 청구의 범위

#### 청구항 1

제품 표면에 걸친 플라즈마 이온 밀도의 방사 분포를 제어할 수 있는 플라즈마 반응기에 있어서.

반도체 제품과 처리 가스를 포함하기 위한 반응기 챔버를 포함하는데, 상기 챔버는 상기 챔버의 내부에 대향하는 3차원적 형태의 내부 표면을 가지는 오버헤드 반도체 시일링을 포함하고;

상기 시일링 위에 놓이고, 개별 독립적으로 제어가능한 방사상 내부 및 방사상 외부 안테나 섹션을 포함하는 유도 안테나; 및

상기 내부 및 외부 안테나 섹션에 각각 접속되는 독립 RF 전력 소스를 포함하는 것을 특징으로 하는 플라즈마 반응기.

#### 청구항 2

제 1항에 있어서, 상기 시일링 내부 표면은 돔형인 것을 특징으로 하는 플라즈마 반응기.

#### 청구항 3

제 2항에 있어서, 상기 시일링 내부 표면은 반구형인 것을 특징으로 하는 플라즈마 반응기.

#### 청구항 4

제 1항에 있어서, 상기 시일링은 상기 시일링 내부 표면의 형태와 일치하는 외부 표면을 더 가지며, 유도 안테나는 상기 시일링 외부 표면 형태와 일치하는 것을 특징으로 하는 플라즈마 반응기.

#### 청구항 5

제 1항에 있어서, 상기 유도 안테나는 상기 3차원 형태의 시일링 내부 표면의 형태에 따르지 않는 것을 특징으로 하는 플라즈마 반응기.

### 청구항 6

제 5항에 있어서, 상기 유도 안테나는 평탄한 것을 특징으로 하는 플라즈마 반응기.

#### 청구항 7

제 1항에 있어서, 상기 시일링의 서로 다른 방사 위치에 배치된 다수의 가열 소스를 더 포함하는 것을 특징으로 하는 플라즈마 반응기.

#### 청구항 8

제 7항에 있어서, 서로 다른 방사 위치에서 가열 소스를 개별적으로 제어하는 온도 제어 시스템을 더 포함하여 상기 시일링은 다수의 방사 온도 제어 구역을 이루는 것을 특징으로 하는 플라즈마 반응기.

### 청구항 9

제 1항에 있어서, 상기 챔버내의 개별적 내부 및 외부 방사 위치에 내부 및 외부 처리 가스 인렛을 더 포함하는 것을 특징으로 하는 플라즈마 반응기.

### 청구항 10

제 9항에 있어서, 상기 내부 및 외부 가스 인렛내의 처리 가스 흐름 속도는 개별적으로 제어가능 한 것을 특징으로 하는 플라즈마 반응기.

# 청구항 11

제 1항에 있어서, 상기 반도체 시일링에 접속된 RF 전력 소스를 더 포함하는 것을 특징으로 하는 플라즈마 반응기.

#### 청구항 12

제 1항에 있어서, 3차원 형태의 시일링은 전기적으로 분리된 방사상 내부 및 외부 시일링 섹션을 포함하고, 상기 반응기는 상기 분리된 시일링 섹션에 접속된 개별 RF 전력 소스를 더 포함하는 것 을 특징으로 하는 플라즈마 반응기.

### 청구항 13

제 3항에 있어서, 상기 시일링은 상기 시일링 내부 표면과 일치하는 외부 표면을 추가로 가지고

유도 안테나는 상기 시일링 외부 표면의 형태와 일치하는 것을 특징으로 하는 플라즈마 반응기.

#### 청구항 14

제 3항에 있어서, 상기 유도 안테나는 상기 3차원 형태의 시일링 내부 표면의 형태에 따르지 않는 것을 특징으로 하는 플라즈마 반응기.

#### 청구항 15

제 3항에 있어서, 상기 시일링의 서로 다른 방사 위치에 배치된 다수의 가열 소스를 더 포함하는 것을 특징으로 하는 플라즈마 반응기.

#### 청구항 16

제 15항에 있어서, 서로 다른 방사 위치에서 가열 소스를 개별적으로 제어하는 온도 제어 시스템을 더 포함하여 상기 시일링은 다수의 방사 온도 제어 구역을 이루는 것을 특징으로 하는 플라즈마 반응기.

#### 청구항 17

제 3항에 있어서, 상기 챔버내의 개별 내부 및 외부 방사 위치에 내부 및 외부 처리 가스 인렛을 더 포함하는 것을 특징으로 하는 플라즈마 반응기.

#### 청구항 18

제 17항에 있어서, 상기 내부 및 외부 가스 인렛내의 처리 가스 흐름 속도는 개별적으로 제어가능 한 것을 특징으로 하는 플라즈마 반응기.

#### 청구항 19

제 3항에 있어서, 상기 반도체 시일링에 접속된 RF 전력 소스를 더 포함하는 것을 특징으로 하는 플라즈마 반응기.

#### 청구항 20

제 3항에 있어서, 상기 3차원 형태의 시일링은 전기적 분리 방사상 내부 및 외부 시일링 섹션을 포함하고, 상기 반응기는 상기 분리 시일링 섹션에 접속된 개별 RF 전력 소스를 더 포함하는 것을 특징으로 하는 플라즈마 반응기.

# 청구항 21

제 8항에 있어서, 상기 챔버내의 개별 내부 및 외부 방사 위치에 내부 및 외부 처리 가스 인렛을 더 포함하는 것을 특징으로 하는 플라즈마 반응기.

# 청구항 22

제 21항에 있어서, 상기 내부 및 외부 가스 인렛내의 처리 가스 흐름 속도는 개별적으로 제어가능 한 것을 특징으로 하는 플라즈마 반응기.

#### 청구항 23

제 8항에 있어서, 상기 시일링은 전기적 분리 방사상 내부 및 외부 시일링 섹션을 포함하고, 상기 반응기는 상기 분리 시일링 섹션에 접속된 개별 RF 전력 소스를 더 포함하는 것을 특징으로 하는 플라즈마 반응기.

#### 청구항 24

제 10항에 있어서, 상기 시일링은 전기적 분리 방사상 내부 및 외부 시일링 섹션을 포함하고, 상 기 반응기는 상기 분리 시일링 섹션에 접속된 개별 RF 전력 소스를 더 포함하는 것을 특징으로 하 는 플라즈마 반응기.

# 청구항 25