(19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第4799167号 (P4799167)

(45) 発行日 平成23年10月26日(2011.10.26)

(24) 登録日 平成23年8月12日(2011.8.12)

(51) Int. Cl.

FL

G05F 3/30 (2006, 01)

GO5F 3/30

> (全 22 頁) 請求項の数 1

(21) 出願番号

特願2005-366658 (P2005-366658)

(22) 出願日 (65) 公開番号 平成17年12月20日 (2005.12.20) 特開2007-172153 (P2007-172153A)

(43) 公開日

審查請求日

平成19年7月5日(2007.7.5)

平成20年5月14日 (2008.5.14)

||(73)特許権者 000221199

東芝マイクロエレクトロニクス株式会社 神奈川県川崎市川崎区駅前本町25番地1

(73)特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

|(74)代理人 100083806

弁理士 三好 秀和

|(74)代理人 100100712

弁理士 岩▲崎▼ 幸邦

|(74)代理人 100100929

弁理士 川又 澄雄

|(74)代理人 100108707

弁理士 中村 友之

最終頁に続く

(54) 【発明の名称】基準電圧発生回路

### (57)【特許請求の範囲】

### 【請求項1】

第1電源と前記第2電源間の第1電流経路に設けられ、前記第2電源の電位に一端の電 位が固定され、他端を第1ノードに接続し、該第1ノードに負の温度依存性を有する第1 基準電圧を発生する第1の基準電圧発生素子と、

前記第1電源と前記第2電源間の第2電流経路に設けられ、前記第2電源の電位に一端 の電位が固定され、前記第1の基準電圧発生素子より電流密度の低く、他端に負の温度依 存性を有する第2基準電圧を発生する第2の基準電圧発生素子と、

該第2の基準電圧発生素子の他端に一端を接続され、他端を前記第2電流経路に設けら れた第2ノードに接続された第1の抵抗素子と、

前記第1ノードに一方の入力端子、前記第2ノードに他方の入力端子を接続した第1差 動増幅器、及び、前記第1電源に一端を接続し、他端を前記第1又は前記第2電流経路に 設けられ、前記基準電圧を出力する出力ノードに接続し、ゲートを前記第1差動増幅器の 出力端子に接続した第1電流制御トランジスタを有し、前記第1基準電圧と、前記第2ノ ードに生じる前記第2基準電圧と前記第1の抵抗素子に発生する電圧の和とを比較し、前 記第1及び第2電流経路に一定の比で電流を供給し、前記第1及び第2基準電圧の差から 正の温度依存性を有する第1の電流量を、前記第1の抵抗素子に流す第1の電流制御回路

前記第1電源と前記第2電源間の第3電流経路において、前記第2電源の電位に一端の 電位を固定した第2の抵抗素子と、

前記第3電流経路において、前記第2の抵抗素子に直列接続されるように、前記第2の抵抗素子の他端と第3ノードの間に接続された第3の抵抗素子と、

前記第1ノードを負入力端子に、前記第2の抵抗素子の他端を正入力端子に接続した第 2差動増幅器と、

前記第3ノードと前記第1電源間に接続され、ゲートに前記第2差動増幅器の出力を接続した第2電流制御トランジスタと、

前記第3ノードと前記第1ノードの間に接続された第4の抵抗素子と、

前記第3ノードと前記第2ノードの間に接続された第5の抵抗素子と、

前記出力ノードと前記第1ノードの間に接続された第6の抵抗素子と、

前記出力ノードと前記第2ノードの間に接続された第7の抵抗素子と

を備え、前記負入力端子と、前記正入力端子の電位とが等しくなる様に、前記第2電流制御トランジスタを制御し、前記第2電流制御トランジスタから前記第5の抵抗素子を経由して、負の温度依存性を持った第2の電流量の電流を前記第2ノードに出力し、前記第7の抵抗素子に前記第1の電流量から前記第2の電流量を減じた電流量の電流を第3の電流量の電流として流し、前記第7の抵抗素子の両端子間に正の温度依存性を有する電圧を発生させ、該正の温度依存性を有する電圧と前記第2ノードの電圧とを加算して、基準電圧を発生し、前記出力ノードから前記基準電圧を出力することを特徴とする基準電圧発生回路。

【発明の詳細な説明】

### 【技術分野】

[00001]

本発明は、基準電圧発生回路に関し、特に、半導体チップ上に集積可能なバンドギャップ型定電圧発生回路に関する。

#### 【背景技術】

#### [0002]

アナログ回路の設計等では各種のばらつき要因に対して安定な電圧を得る必要が生じる。例えば、高分解能のA/D変換器やD/A変換器等では、その分解能を保証するため、温度補償をも考慮した高精度の基準電圧回路が必要となる。この様な目的で、例えば、複数のトランジスタ及び複数の抵抗からなり、出力電圧を出力するバンドギャップ回路と、供給電源との間に、複数のトランジスタからなる電流反転増幅器、及び複数のダイオード抵抗からなる起動回路を付加し、供給電源の変動に起因する出力電圧の変動を低減したバンドギャップ型定電圧発生回路が提案されている(特許文献 1 参照。)

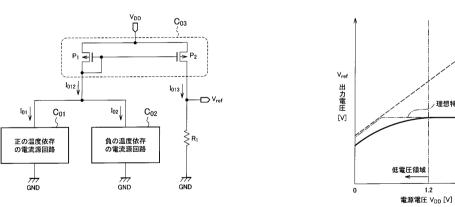

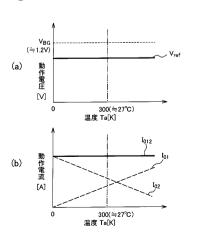

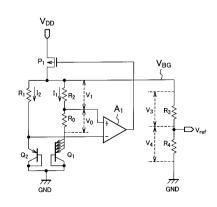

図16は、シリコンの絶対0度(0K)におけるバンドギャップ電圧(約1.2V)よりも低く温度依存性の無い基準電圧V<sub>ref</sub>を発生する基準電圧発生回路の一例である。又、図17に図16に示した基準電圧発生回路の動作電圧と動作電流の温度依存特性を模式的に示す。

#### [0003]

図16では、正の温度依存性を持った電流  $I_{01}$ を出力する電流源回路  $C_{01}$ と、負の温度依存性を持った電流  $I_{02}$ を出力する電流源回路  $C_{02}$ を設置し、電流  $I_{01}$ と電流  $I_{02}$ の和が温度依存特性を持たない一定の電流  $I_{012}$ となるように設定される。この電流  $I_{012}$ は、カレントミラー回路  $C_{03}$ によって所望のミラー比で折り返され電流  $I_{013}$ を出力する。  $I_{013}$ は抵抗  $R_1$ に印加され抵抗  $R_1$ の値に応じた電圧  $V_{ref}$ を出力する。

### [0004]

図18に図16に示した基準電圧発生回路の電源電圧依存特性を示す。図16に示した基準電圧発生回路では $V_{DD}$ 電源電圧が低下しシリコンのバンドギャップ電圧(約1.2V)程度の低電圧領域になると、カレントミラー回路 $C_{03}$ の出力トランジスタ $_{P2}$ の $V_{DS}$ が減少するため、電流 $I_{013}$ が低下し出力 $V_{ref}$ が理想特性から大きく低下する。よって、低電圧領域では、基準電圧 $V_{ref}$ の精度が悪化する不具合を生じる。

## [0005]

図19に基準電圧発生回路の他の例を示す。図19は、電流密度の異なるpnpトラン

10

20

30

40

ジスタ $Q_1$ ,  $Q_2$ の $V_{BE}$ 電位差 $V_0$ を $R_0$ によって電流  $I_1$ に変換し、抵抗  $R_1$ によりシリコンの 0 Kにおけるバンドギャップ電圧(約 1 . 2 V)近傍の電圧  $V_{BG}$ を作成する。この時、熱電圧  $V_T$  = K T / Q とし、 $Q_1$  と $Q_2$ の  $V_{BE}$ をそれぞれ  $V_{BEQ1}$ ,  $V_{BEQ2}$  とし、 $Q_1$  と並列接続された  $Q_2$ のエミッタ面積をそれぞれ  $S_{Q1}$ ,  $S_{Q2}$  とすると、

$V_0 = I_1 \times R_0 = V_T \times In((S_{Q1}/S_{Q2}) \times (R_1/R_2))$  ... (1)  $V_{BG} = V_{BEQ2} + R_1/R_0 \times V_0$

=  $V_{BEQ2}$  +  $R_1$  /  $R_0$  ×  $V_T$  × In ( ( $S_{Q1}$  /  $S_{Q2}$  ) × ( $R_1$  /  $R_2$  ) ) .... (2) で表わせる。この $V_T$  は約0.086 [m V / ]で正の温度依存性を持ち、 $V_{BEQ2}$  はおよそ・1.9 [m V / ]程度の負の温度依存性を持つ。よって、 $R_1$  /  $R_0$  を温度依存特性を相殺する値に設定すると温度依存性の無い $V_{BG}$  を出力できる。 $V_{ref}$  は $V_{BG}$  をブリーダ抵抗  $R_3$  ,  $R_4$  の抵抗比で分割した電圧であり、 $V_{BG}$  と同様に温度依存性の無い一定の電圧となる。

#### [0006]

通常、 $V_{BG}$ はシリコンのバンドギャップ電圧(約1.2V)近傍の電圧となるため、 $R_4$ /( $R_3+R_4$ )の比を1より小さく設定することで1.2V以下の電圧を出力可能であるが、 $V_{DD}$ 電源電圧が1.2V程度以下の低電圧領域では $V_{BG}$ が低下し $V_{ref}$ は所望の値を出力できないという不具合を生じる。

【特許文献 1 】特開平 7 - 2 3 0 3 3 2 号公報

【発明の開示】

【発明が解決しようとする課題】

[0007]

本発明は、バンドギャップ電圧以下の低い電源電圧でも動作し、電源電圧依存特性が小さく、温度補償された基準電圧を発生させることのできる基準電圧発生回路を提供することを目的とする。

【課題を解決するための手段】

### [0008]

上記目的を達成するために、本発明の第1の態様は、(イ)第1の基準電圧発生素子が生成する負の温度依存性を有する第1基準電圧と、この第1の基準電圧発生素子より電流密度の低い第2の基準電圧発生素子が生成する負の温度依存性を有する第2基準電圧との差を、第1及び第2の基準電圧の差に比例した第1の電流量に変換する第1の電流変換回路と、(ロ)第1又は第2の基準電圧を、この基準電圧に比例した第2の電流量に変換する第2の電流変換回路と、(ハ)第1の電流量から第2の電流量を減じ、第3の電流量を生成する電流減算回路と、(二)第3の電流量を電圧変換して正の温度依存性を有する温度特性補償電圧を生成する電流電圧変換回路と、(ホ)第1基準電圧と温度特性補償電圧とを加算し、この加算した値を基準電圧として出力する電圧加算回路とを備える基準電圧発生回路であることを特徴とする。

## [0009]

本発明の第2の態様は、(イ)第1電源と第2電源間の第1電流経路に設けられ、第2電源の電位に一端の電位が固定され、他端を第1ノードに接続し、この第1ノードに負の温度依存性を有する第1基準電圧を発生する第1の基準電圧発生素子と、(ロ)第1電源と第2電源間の第2電流経路に設けられ、第2電源の電位に一端の電位が固定され、第1の基準電圧発生素子より電流密度の低く、他端に負の温度依存性を有する第2基準電圧発生素子の他端に一端を接続する第1の抵抗素子の他端に一端を接続する第1の抵抗素子がらなる直列回路と、(ハ)第1基準電圧と第1の抵抗素子に発生する電圧の和とを接続で、第1及び第2電流経路に一定の比で電流を供給し、第1及び第2基準電圧の差から正の温度依存性を有する第1の電流量を、第1の電流量を減じ、正の温度依存性を有する電圧に変換し、この電流量を生成し、この第3の電流量を正の温度依存性を有する電圧に変換し、この第3の電流量を生成し、この第3の電流量を正の温度依存性を有する電圧に変換し、この第3の電流量を正の温度依存性を有する電圧に変換し、この

20

10

30

40

正の温度依存性を有する電圧と第1又は第2ノードの電圧とを加算して、基準電圧を発生する。

#### 【発明の効果】

#### [0010]

本発明によれば、バンドギャップ電圧以下の低い電源電圧でも動作し、電源電圧依存特性が小さく、温度補償された基準電圧を発生させることのできる基準電圧発生回路を提供することができる。

### 【発明を実施するための最良の形態】

### [0011]

次に、図面を参照して、本発明の第1~第9の実施の形態を説明する。以下の図面の記載において、同一又は類似の回路素子等の構成要素には同一又は類似の符号を付している。但し、図面は模式的なものであり、以下に示す第1~第9の実施の形態は、本発明の技術的思想を具体化するための装置や方法を例示するものであって、本発明の技術的思想は、回路構成のトポロジーや、構造、配置等を下記のものに特定するものでない。本発明の技術的思想は、特許請求の範囲に記載された技術的範囲内において、種々の変更を加えることができる。

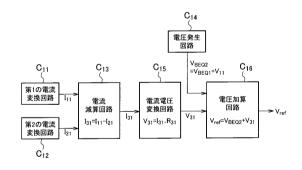

### [0012]

図 1 は、本発明の第 1 ~第 9 の実施の形態に係る基準電圧発生回路の論理的な構成を示すプロック図である。図 1 に示す基準電圧発生回路は、第 1 の基準電圧発生素子が生成する負の温度依存性を有する第 1 基準電圧  $V_{BEQ2}$ と、この第 1 の基準電圧発生素子より電流密度の低い第 2 の基準電圧発生素子が生成する負の温度依存性を有する第 2 基準電圧  $V_{BEQ1}$ との差  $V_{11}$ を、第 1 及び第 2 の基準電圧の差に比例した第 1 の電流量  $I_{11}$ に変換する第 1 の電流変換回路  $I_{11}$ と、第 1 基準電圧  $I_{11}$  又は第 2 基準電圧  $I_{11}$  と、第 1 基準電圧  $I_{11}$  を  $I_{$

## [0013]

「第1の基準電圧発生素子」及び「第2の基準電圧発生素子」としては、電流密度を変えpn接合ダイオード、電流密度の互いに異なるダイオード接続されたバイポーラトランジスタや電流密度の互いに異なるダイオード接続されたMOSトランジスタが使用可能である。

# [0014]

pn接合ダイオードの場合は、電流密度の互いに異なるpn接合の順方向電圧V<sub>f</sub>特性、ダイオード接続されたバイポーラトランジスタの場合は電流密度の互いに異なるバイポーラトランジスタのベースエミッタ間電圧V<sub>BE</sub>特性、ダイオード接続されたMOSトランジスタの場合は、電流密度の互いに異なるMOSトランジスタの弱反転領域特性が第1基準電圧及び第2基準電圧として使用可能である。

## [0015]

例えば、 p n 接合の順方向電圧の差を用いる場合は、図 1 に示す基準電圧発生回路の第 1 の電流変換回路  $C_{11}$  は、電流密度を変えた p n 接合の順方向電圧の差をその電圧に比例した第 1 の電流量  $I_{11}$  に変換する。第 2 の電流変換回路  $C_{12}$  は、 p n 接合の順方向電圧をその電圧に比例した第 2 の電流量  $I_{21}$  に変換する。なお、図 1 では、 p n 接合の順方向電圧に依存する第 1 の電圧  $V_1$  ( =  $V_{BEQ2}$  =  $V_{BEQ1}$  +  $V_{11}$ )を発生する電圧発生回路  $C_{14}$ を示しているが、図 1 は論理的な回路構成を示しているためであり、現実の回路としては、第 1 の電流変換回路  $C_{11}$  の第 1 の基準電圧発生素子又は第 2 の電流変換回路  $C_{12}$  の第 2 の基準電圧発生素子が生成する第 2 基準電圧を用いて、第 1 の電圧  $V_1$  ( =  $V_{BEQ2}$  =  $V_{BEQ1}$  +  $V_{11}$ )を発生するようにすることができる。

10

20

30

40

20

30

50

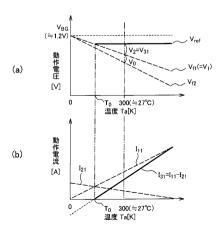

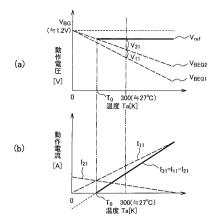

#### [0016]

図 2 ( a )に図 1 に論理的な構成を示した基準電圧発生回路の動作電圧の温度依存特性を、図 2 ( b )に図 1 の基準電圧発生回路の動作電流の温度依存特性を、それぞれ模式的に示す。電流密度を変えた 2 種類の p n 接合電位を  $V_{f1}$  ,  $V_{f2}$  とすると、  $V_0$  =  $V_{f1}$  -  $V_{f2}$  で示される電位差は絶対 0 度( 0 K )を原点とする正の温度依存性を持った値となる。これを抵抗素子などで電流変換した第 1 の電流量  $I_{11}$  は、同じく 0 K を原点とする正の温度依存性を持った電流となる。又、 p n 接合電位  $V_{f1}$  は、負の温度依存性を持った値となる。これを抵抗素子などで電流変換した第 2 の電流量  $I_{21}$  は、負の温度依存性を持った値となる。これを抵抗素子などで電流変換した第 2 の電流量  $I_{21}$  は、負の温度依存性を持った値となる。第 1 の電流量  $I_{11}$  から第 2 の電流量  $I_{21}$  を滅じた第 3 の電流量  $I_{31}$  =  $I_{11}$  -  $I_{21}$  は、図 2 ( b )に示すように、温度  $I_{21}$  を原点に増加する電流  $I_{31}$  となる。 p n 接合の順方向電圧に依存する第 1 の電圧を例えば  $V_{f1}$  とし、電流  $I_{31}$  を抵抗素子などで電圧に変換した電圧を第 2 の電圧(温度特性補償電圧)  $V_{2}$  とし、この和が温度依存特性を持たない比率で加算した電圧を  $V_{ref}$  とすると、  $V_{ref}$  =  $V_{f1}$  +  $V_{2}$  は図 2 ( a )に示すように定電圧になる。

#### [0017]

このとき、非常に低い温度  $T_0$ 以上の温度領域において、  $V_{ref}$  は温度  $T_0$ における  $p_0$  n 接合順方向電圧  $V_{f_1}$  の値と等しく温度依存性の無い電圧を出力する。この値は、シリコンの絶対 0 度 ( 0 K ) におけるバンドギャップ電圧(約 1 . 2 V ) よりも低い電圧となる。この  $T_0$  は、例えば  $V_{ref}$  = 0 . 8 V に設定した場合、 - 1 0 0 程度以下の値となり通常の I C の最低動作温度条件よりも小さな値となるため、低温での動作範囲が制限されることは無い。

#### [0018]

上記効果は、pn接合のV゚特性の代わりにpnpトランジスタなどのバイポーラトランジスタのVBE特性や、ダイオード接続されたMOSトランジスタの弱反転領域特性を利用しても同様の効果が得られる。

### [0019]

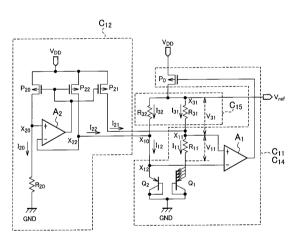

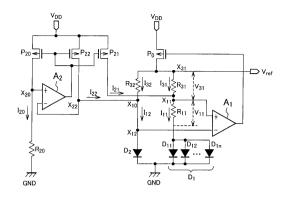

## (第1の実施の形態)

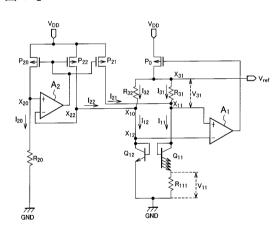

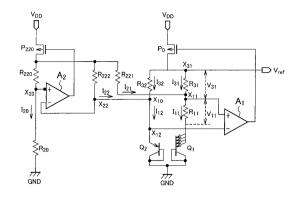

図3に本発明の第1の実施の形態に係る基準電圧発生回路の回路構成の一例を示す。図 3の基準電圧発生回路は、ベースとコレクタ端子を共にGND電源に接続しダイオード接 続したpnpトランジスタ(第1の基準電圧発生素子)Qっと、ベースとコレクタ端子を 共にGND電源に接続した(ダイオード接続した)単位素子を複数個並列接続させ、pn pトランジスタQ<sub>2</sub>よりエミッタ電流密度を低くしたpnpトランジスタ(第2の基準電 圧発生素子) Q₁と、出力端子 V refとpnpトランジスタ Q₁のエミッタ間に直列接続さ れた抵抗素子R31及びR11と、出力端子VrefとpnpトランジスタQ2のエミッタ間に接 続された抵抗素子 R 32 と、抵抗素子 R 31 と抵抗素子 R 11 の接続点(第 2 ノード) X 11 を正 (+)入力端子に接続し抵抗素子 $R_{32}$ とpnpトランジスタ $Q_2$ との接続点(第1ノード ) X <sub>12</sub>( = X <sub>10</sub>)を負( - )入力端子に接続した第1差動増幅回路 A <sub>1</sub>と、 V <sub>DD</sub>電源をソ ースに接続し出力端子 V<sub>ref</sub>をドレインに接続し第1差動増幅回路 A<sub>1</sub>の出力をゲートに接 続したрМОSトランジスタ(第1電流制御トランジスタ)Р ₀と、一端をGND電源に 接続した抵抗素子R<sub>20</sub>と、抵抗素子R<sub>32</sub>とpnpトランジスタQ<sub>2</sub>の接続点(第1ノード ) X<sub>12</sub> ( = X<sub>10</sub> = X<sub>22</sub> ) を負( - ) 入力端子に接続し抵抗素子 R<sub>20</sub>の他方の端子 ( ノード ) X <sub>2 0</sub> を正( + )入力端子に接続した第 2 差動増幅回路 A <sub>2</sub>と、それぞれ V <sub>DD</sub>電源をソー スに接続し第2差動増幅回路  $A_2$ の出力をゲートに接続した p M O S  $トランジスタ <math>P_{20}$  ,  $P_{21}$  ,  $P_{22}$ と、  $PMOSトランジスタ (第2電流制御トランジスタ) <math>P_{20}$ のドレインを第 3 ノード X <sub>20</sub> で抵抗素子 R <sub>20</sub> の他端に接続し、 p M O S トランジスタ(第 3 電流制御トラ ンジスタ) P<sub>21</sub> のドレインを抵抗素子 R<sub>31</sub>と R<sub>11</sub>の接続点(第 2 ノード) X<sub>11</sub>に接続し 、 p M O S トランジスタ P 22のドレインを抵抗素子 R 32 と p n p トランジスタ Q 2の接続 点(第 1 ノード)  $X_{12}$ ( =  $X_{10}$  =  $X_{22}$ )に接続している。

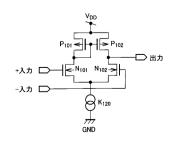

### [0020]

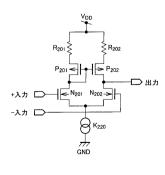

図 4 に示すように、第 1 差動増幅回路  $A_1$ 及び第 2 差動増幅回路  $A_2$ は、第 1 電源  $V_{DD}$ に

20

30

40

50

ソースを接続し、ゲートとドレインとを短絡した p M O S トランジスタ  $P_{101}$  と、第 1 電源  $V_{DD}$  にソースを接続し、 p M O S トランジスタ  $P_{101}$  のゲートにゲートを接続した p M O S トランジスタ  $P_{102}$  と、 p M O S トランジスタ  $P_{101}$  のドレインにドレインを接続し定電流源  $K_{120}$  にソースを接続した n M O S トランジスタ  $P_{102}$  のドレインにドレインを接続し定電流源  $K_{120}$  にソースを接続した n M O S トランジスタ  $P_{102}$  のドレインにドレインを接続し定電流源  $K_{120}$  にソースを接続した n M O S トランジスタ  $P_{102}$  とを備え、 n M O S トランジスタ  $P_{102}$  とを備え、 n M O S トランジスタ  $P_{102}$  のゲートを  $P_{102}$  の ゲートを  $P_{102}$  の  $P_{1$

## [0021]

図3に示す第1の実施の形態に係る基準電圧発生回路を、図1に示したブロック図に対 応させると、図1に示したブロック図の第1の電流変換回路C11は、第1電源VDDと第2 電源(GND)間に設けられ第2電源(GND)に一端を接続されたダイオード接続され 接続された、ダイオード接続されたpnpトランジスタ(第1の基準電圧発生素子)Q🤈 より電流密度の低いダイオード接続されたpnpトランジスタ(第2の基準電圧発生素子 ) Q <sub>1</sub> と第 1 の抵抗素子 R <sub>11</sub> からなる直列回路( Q <sub>1</sub> , R <sub>11</sub> )と、ダイオード接続された p  $nphランジスタ(第1の基準電圧発生素子)Q_2に発生するベース・エミッタ間電圧($ p n 接合順方向電圧) V <sub>BFO2</sub>で規定される第1の電圧とダイオード接続された p n p トラ ンジスタ(第 2 の基準電圧発生素子)  $Q_1$ に発生するベース・エミッタ間電圧( $p_1$  n 接合 順方向電圧) V B E O 1 で規定される電圧と第1の抵抗素子 R 1 1 に発生する電圧 V 1 1 の和( V BEQ1 + V<sub>11</sub>)となる第2の電圧を比較しダイオード接続されたpnpトランジスタ(第1 の基準電圧発生素子) Q <sub>2</sub> 及び直列回路( Q <sub>1</sub> , R <sub>1 1</sub> ) に一定の比で電流を供給し第 1 の電 圧と第2の電圧が等しくなる様に制御する第1の電流制御回路( $A_1$ ,  $P_0$ )とを備える。 第1の電流制御回路(A<sub>1</sub>,P<sub>0</sub>)は、第1ノードX<sub>10</sub>の第1の電圧を負(-)入力端子に 接続し、第2ノードXィィの第2の電圧を正(+)入力端子に接続し、第1の電圧と第2の 電圧を比較する第1差動増幅回路A<sub>1</sub>と、第2電源V<sub>DD</sub>に一端を接続し、他端を出力ノー ド X <sub>3 1</sub> に接続し、ゲートを第 1 差動増幅器 A <sub>1</sub> の出力端子に接続した p M O S トランジス タ(第1電流制御トランジスタ) P<sub>0</sub>とを備える。

## [0022]

# [0023]

20

30

40

50

#### [0024]

図 1 に示したブロック図の電圧加算回路  $C_{16}$ は、第 1 電源  $V_{DD}$ と第 2 電源( G N D )間に設けられ一端を直列回路(  $Q_1$  ,  $R_{11}$  )に直列接続され他端に第 1 の電流制御回路  $A_1$  の出力電流に応じた電流が供給される第 3 の抵抗素子  $R_{31}$ を設け、この第 3 の抵抗素子  $R_{31}$  の一端に第 2 の電流変換回路  $C_{12}$  の出力電流  $I_{21}$  を供給することで、第 3 の抵抗素子  $R_{31}$  に正の温度依存を持った第 1 の電流量  $I_{11}$  から負の温度依存を持った第 2 の電流量  $I_{21}$  を減じた第 3 の電流量  $I_{31}$  =  $I_{11}$  -  $I_{21}$  を発生させ、第 3 の抵抗素子  $R_{31}$  の他端に温度補償された電源電圧に依存しないバンドギャップ電圧以下の電圧  $V_{ref}$  =  $V_{BEQ2}$  +  $V_{31}$ を出力させる。これにより、第 1 の電流制御回路  $A_1$  の帰還作用によって第 1 電源  $V_{DD}$  の電圧がバンドギャップ電圧以下であっても電圧依存がより小さくなる様にしている。

[0025]

$$I_{31} = I_{11} - I_{21}$$

... (3)

$I_{32} = I_{12} - I_{22}$  ... (4)

となる。それぞれ  $I_{11}$  ,  $I_{12}$  から  $I_{21}$  ,  $I_{22}$  を減じた電流として出力されることで、図 1 に示したブロック図の電流減算回路  $C_{13}$  を構成する。又、抵抗素子  $R_{31}$  ,  $R_{32}$  は、図 1 に示したブロック図の電流電圧変換回路  $C_{15}$  を構成し、  $I_{31}$  ,  $I_{32}$  は、それぞれ抵抗素子  $R_{31}$  ,  $R_{32}$  により第 2 の電圧(温度特性補償電圧)  $V_2$  ( $=V_{31}$ ) を形成する。第 2 の電圧(温度特性補償電圧)  $V_2$  ( $=V_{31}$ ) は、ベース・エミッタ間電圧  $V_{BEQ2}$  ( $=V_{BEQ1}+V_{11}$  ) に加算され出力電圧  $V_{CR1}$  を出力する。

## [0026]

ここで、熱電圧を $V_T$  (= kT/q)、 $pnphランジスタQ_1 と Q_2 のエミッタ面積をそれぞれ <math>S_{Q1}$  ,  $S_{Q2}$ 、 $pMOShランジスタP_{20}$  ,  $P_{21}$  ,  $P_{22}$  のカレントミラー比  $I_{20}$  :

$$V_{11} = I_{11} \times R_{11} = V_T \times ln((S_{Q1}/S_{Q2}) \times (I_{12}/I_{11}))$$

... (5)

$I_{11} = I_{21} + I_{31}$

$$= ((V_{BEQ2} / R_{20}) \times (q / p)) + (V_{ref} - V_{BEQ2}) / R_{31} \qquad ... (6)$$

$I_{12} = I_{22} + I_{32}$

$$= ((V_{BEQ2} / R_{20}) \times (r / p)) + (V_{ref} - V_{BEQ2}) / R_{32} \qquad ... (7)$$

と表わせる。更に、

$$K = (1 / R_{20}) \times (q / p) = (1 / m) \times (1 / R_{20}) \times (r / p)$$

... (8)

$$L = 1 / R_{31} = 1 / (n \times R_{32})$$

... (9)

と置き、式(6),(7)に代入するとI<sub>12</sub>/I<sub>11</sub>は、

$I_{12}/I_{11} = (m \times V_{BEQ2} \times K + n \times L \times (V_{ref} - V_{BEQ2}))/(V_{BEQ2} \times K + L \times (V_{ref} - V_{BEQ2}))$

となる。簡単化のために式(10)において例えばm=nとすると、 $I_{12}$  /  $I_{11}$  = m ( =

20

30

50

n)となる。この場合、

$I_{11} = V_T \times \ln((S_{01}/S_{02}) \times m) / R_{11}$  ... (11)

と表わせる。又、

$I_{21} = (V_{BEQ2} / R_{20}) \times (q / p)$  ... (12)

であるから、出力電圧Vィѧィは、

$V_{ref} = V_{BEQ2} + V_{31}$

$= V_{BEQ2} + R_{31} \times (I_{11} - I_{21})$

=  $V_{BEQ2} + R_{31} \times (V_T \times In((S_{Q1}/S_{Q2}) \times m)/R_{11} - (V_{BEQ2}/R_{20}) \times (q/p))$  ... (13)

と表わせる。この式(13)には $V_{DD}$ 電源の電圧に依存する項が無いので $V_{ref}$ は $V_{DD}$ 依存の無い電圧として定電圧動作を行なう。又、一般的に p n p h p h p n p h p n p h p n p h p n p h p n p h p n p h p n p h p n p h p n p h p n p h p n p h p n p h p n p h p n p h p n p h p n p h p n p h p n p h p n p h p n p h p n p h p n p h p n p h p n p h p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p n p

### [0027]

ここで、 $V_{DD}$ が低下した場合の動作について更に詳細に説明する。 $V_{DD}$ が低下すると、 $P_{DD}$  M O S トランジスタ(第 1 電流制御トランジスタ) $P_0$  の  $V_{DS}$  が低下し $I_{31}$  ,  $I_{32}$  が減少しようとする。この時、電流  $I_{11}$  ,  $I_{12}$  が減少し、第 1 差動増幅回路  $A_1$  の正(+)入力端子が負(-)入力端子より小さくなると、 $P_{DD}$  M O S トランジスタ(第 1 電流制御トランジスタ) $P_0$  のゲートを下げ  $I_{31}$  ,  $I_{32}$  を増やす方向にフードバック制御する。これにより、 $I_{11}$  ,  $I_{12}$  が増加し第 1 差動増幅回路  $A_1$  の正(+)入力端子と負(-)入力端子が等しい点で安定しようと動作する。又、 $P_{DD}$  M O S トランジスタ  $P_{20}$  ,  $P_{21}$  ,  $P_{22}$  は、第 1 差動増幅回路  $A_1$  及び第 2 差動増幅回路  $A_2$  のオフセットを無視すると、 $V_{DS}$  が等しくなる。よって、 $V_{DD}$  変動によるチャネル長変調の影響は 3 つのトランジスタでまったく同じに作用するため、 $V_{DS}$  の違いによるカレントミラー電流比の設計値からのずれは非常に小さくなる。よって、 $I_{21}$  ,  $I_{22}$  の  $V_{DD}$  変動による設計値からのずれ量は非常に小さくなり、 $I_{31}$  ,  $I_{32}$  に 所 ど影響しない。

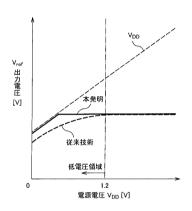

# [0028]

図6に第1の実施の形態に係る基準電圧発生回路の出力電圧の電源電圧依存特性を示す。図6に示した様に $V_{DD}$ 電源が低電圧領域、例えばシリコンの絶対0度におけるバンドギャップ電圧 $V_{BG}$ (約1.2V)より小さな領域であっても、電源電圧変動の非常に小さい理想的な出力電圧を得ることができる。これは、図16に示した従来回路での $V_{ref}$ 出力特性における不具合を大幅に改善するものである。

### [0029]

又、従来の基準電圧発生回路では、抵抗素子 R  $_{11}$  の温度依存等により高温時と低温時で抵抗値が変化すると、ベース・エミッタ間電圧 V  $_{BEQ1}$  , V  $_{BEQ2}$ 特性が温度に対して湾曲した特性となる不具合があった。式(10)において、m及びnをベース・エミッタ間電圧 V  $_{BE}$  の特性変化を補正する様に変更することで更に温度依存に対する精度向上が図れる。 m nの時、低温時はベース・エミッタ間電圧 V  $_{BEQ2}$  がより大きくなるため、(V  $_{BEQ2}$  × K)に掛かる係数mの依存度が大きくなり動作電流 I  $_{12}$  / I  $_{11}$  比は係数 n ~ mの範囲内でより係数mにより近い値となる。その逆に高温はベース・エミッタ間電圧 V  $_{BEQ2}$  がより小さな値となるため、(L × (V  $_{ref}$  - V  $_{BEQ2}$ ))に掛かる係数 n の依存度が大きくなり動作電流 I  $_{12}$  / I  $_{11}$  比は係数 n ~ mの範囲内でより係数 n により近い値となる。例えば、正の温度依存の抵抗素子を用いた場合、高温時はエミッタ電流が減少しベース・エミッタ間電圧 V  $_{BEQ2}$  が本来の値より小さくなる。これにより、 V  $_{ref}$  電圧は温度に対して上に凸の弧を描いた特性となってしまう。これは、温度依存に対する精度が悪化することを意味する。図 3 に示す第 1 の実施の形態に係る基準電圧発生回路の場合、係数 m 、 n の関係を m < n と設定することで低温時に比べ高温時の I

$_{12}$  /  $_{11}$ 比をより大きくすることが可能となる。 V  $_{11}$ は式(5)で示される様に  $_{12}$  /  $_{11}$ 比が大きい程大きくなるので、高温時において  $_{m}$  =  $_{n}$  と設定した場合よりも V  $_{11}$  をより大きくできる。よって、高温時に  $_{11}$  が増大し抵抗素子の温度依存による  $_{11}$  の減少を抑制できる。 つまり、 V  $_{ref}$  出力電圧の温度に対して上に凸の弧を描く特性を改善する効果を有する。 負の温度特性の抵抗素子を用いた場合はその逆で  $_{n}$   $_{n}$  不と設定することで、従来技術では温度に対して下に凸の弧を描く V  $_{ref}$  電圧特性を緩和することが可能となる。

更に、図3の構成の場合はベース・エミッタ間電圧  $V_{BEQ1}$  、 $V_{BEQ2}$ の値がプロセスばらつき等で大きくなった場合、式(12)で示される様に、電流  $I_{21}$  , $I_{22}$ もそれに伴い増加する。よって、電流  $I_{31}$  , $I_{32}$ は減少する方向に作用するため、ベース・エミッタ間電圧  $V_{BE}$ の上昇は相殺され  $V_{ref}$ の上昇を抑える効果も有する。

# [0031]

この様に、第1の実施の形態に係る基準電圧発生回路によれば、シリコンのバンドギャップ電圧(約1.2V)以下の低い電圧領域でも、温度依存の無い基準電圧を発生し、バンドギャップ電圧以下等の低電圧電源でも電源電圧変動の非常に小さい理想的な出力電圧を得ることができる。又、本発明の第1の実施の形態に係る基準電圧発生回路によれば、使用される抵抗素子の温度依存性による出力電圧の歪みを補正し、V゚特性やVве特性等のばらつきに対してもそれを補正する様に動作するため、より高精度な基準電圧を発生できる。これにより、本発明の第1の実施の形態に係る基準電圧発生回路によれば、基準電圧が供給されるアナログ回路等の半導体集積回路の精度を向上でき、半導体集積回路の製品としての付加価値を高めることができる。

#### [0032]

### (第2の実施の形態)

図3で示した第1の実施の形態に係る基準電圧発生回路では、第1及び第2の基準電圧発生素子としてバイポーラトランジスタを採用したが、第2の実施の形態に係る基準電圧発生回路のように、基準電圧発生素子としてpn接合ダイオードを採用することも可能であり、pn接合ダイオードの $V_f$ 特性を利用しても同様の効果が得られる。即ち、図7では、図3に示した第1の実施の形態に係る基準電圧発生回路のpnphランジスタ $Q_1$ ,  $Q_2$ のエミッタ・コレクタ(ベース)間の代わりにpn接合ダイオード(以下、ダイオード) $D_1$ ,  $D_2$ のアノード・カソード間を接続し置き換えている。

### [0033]

図 7 では、図 1 に示したブロック図の第 1 の電流変換回路 C 11は、第 1 電源 V DDと第 2 電源(GND)間に設けられ第2電源(GND)に一端を接続された第1のpn接合ダイ オード(第1の基準電圧発生素子) D 2 と、第2電源(GND)に一端を接続された、第 1のpn接合ダイオード(第1の基準電圧発生素子)D<sub>2</sub>より電流密度の低い第2のpn 接合ダイオード(第2の基準電圧発生素子)D₁と第1の抵抗素子R₁₁からなる直列回路 ( D ₁ , R ₁ ₁ )と、第 1 の p n 接合ダイオード(第 1 の基準電圧発生素子) D ₂ に発生する 順方向電圧V<sub>f2</sub>で規定される第1の電圧と第2のpn接合ダイオード(第2の基準電圧発 生素子) D 1 に発生する順方向電圧 V 11 で規定される電圧と第1の抵抗素子 R 11 に発生す 1の基準電圧発生素子) D<sub>2</sub>及び直列回路(D<sub>1</sub>, R<sub>11</sub>) に一定の比で電流を供給し第1の 電圧と第2の電圧が等しくなる様に制御する第1の電流制御回路(A₁,P。) とを備える 。第1の電流制御回路(A<sub>1</sub>,P<sub>ο</sub>)は、第1の電圧を負(-)入力端子に接続し、第2の 電圧を正(+)入力端子に接続し、第1の電圧と第2の電圧を比較する第1差動増幅回路  $A_1$ と、第1差動増幅回路  $A_1$ の出力をゲートに入力する p M O S トランジスタ(第1電流 制御トランジスタ)P゚とを備える。そして、第1の電流変換回路C゚゚゚は、第1のpn接 合ダイオード(第 1 の基準電圧発生素子) D <sub>2</sub>の順方向電圧 V <sub>f 2</sub>と第 2 の p n 接合ダイオ ード(第2の基準電圧発生素子) D<sub>1</sub>の順方向電圧 V<sub>f1</sub>との差 V<sub>11</sub> = V<sub>f2</sub> - V<sub>f1</sub>から正の 温度依存を持った第1の電流量I<sub>11</sub>に変換する。

[0034]

10

20

30

20

30

50

第 2 の p n 接合ダイオード(第 2 の基準電圧発生素子) D  $_1$  は、図 3 に示した第 1 の実施の形態に係る基準電圧発生回路の Q  $_1$  と同様に、複数個の p n 接合ダイオード D  $_{11}$  ,D  $_{12}$  ,・・・・,D  $_{1n}$  を並列接続され、第 2 の p n 接合ダイオード(第 2 の基準電圧発生素子) D  $_1$  の並列接続されたすべての p n 接合面積の合計を S  $_{D1}$  、第 1 の p n 接合ダイオード(第 1 の基準電圧発生素子) D  $_2$  の p n 接合面積を S  $_{D2}$  とし、第 2 の p n 接合ダイオード(第 2 の基準電圧発生素子) D  $_1$  の順方向電圧を V  $_{11}$  、第 1 の p n 接合ダイオード(第 1 の基準電圧発生素子) D  $_2$  の順方向電圧を V  $_{12}$  とすると V  $_{11}$  には、

$V_{11} = I_{11} \times R_{11} = V_T \times In((S_{D1}/S_{D2}) \times (I_{12}/I_{11}))$  … (14) の電圧を発生し、図3に示す第1の実施の形態に係る基準電圧発生回路と同等の動作特性を示し同等の効果を得られる。

# [0035]

図 1 に示したブロック図の第 2 の電流変換回路  $C_{12}$ は、図 7 では、第 1 の p n 接合ダイオード(第 1 の基準電圧発生素子)  $D_2$ の順方向電圧  $V_{f2}$ を入力電圧とし第 2 電源(G N D)を一端に接続された第 2 の抵抗素子  $R_{20}$ の他端が入力電圧と等しくなる様に電流を制御する第 2 の電流制御回路( $A_2$ ,  $P_{20}$ 、 $P_{21}$ )を備え、負の温度依存を持った第 2 の電流量  $I_{21}$ に変換する。第 2 の電流制御回路( $A_2$ ,  $P_{20}$ 、 $P_{21}$ )は、第 1 の p n 接合ダイオード(第 1 の基準電圧発生素子)  $D_2$ の順方向電圧  $V_{f2}$ を負( - )入力端子に接続し、第 2 の抵抗素子  $R_{20}$ の他端を正(+ )入力端子に接続した第 2 差動増幅回路  $A_2$ と、第 2 差動増幅回路  $A_2$ の出力をゲートに入力する p M O S  $P_{20}$ 及び P M O S  $P_{20}$  とを備える。 P M O S  $P_{20}$  との M O S  $P_{20}$  とを備える。 P M O S  $P_{20}$  との M O S  $P_{20}$  とを備える。 P M O S  $P_{20}$  とは、カレントミラー回路を構成している。

### [0036]

図 1 に示したブロック図の電圧加算回路  $C_{16}$ は、第 1 電源  $V_{DD}$ と第 2 電源(G N D )間に設けられ一端を直列回路( $D_1$  , $R_{11}$ )に直列接続され他端に第 1 の電流制御回路  $A_1$ の出力電流に応じた電流が供給される第 3 の抵抗素子  $R_{31}$ を設け、この第 3 の抵抗素子  $R_{31}$ の一端に第 2 の電流変換回路  $C_{12}$ の出力電流  $I_{21}$ を供給することで、第 3 の抵抗素子  $R_{31}$  に正の温度依存を持った第 1 の電流量  $I_{11}$  から負の温度依存を持った第 2 の電流量  $I_{21}$ を 減じた第 3 の電流量  $I_{31}$  =  $I_{11}$  -  $I_{21}$ を発生させ、第 3 の抵抗素子  $R_{31}$  の他端に温度補償された電源電圧に依存しないバンドギャップ電圧以下の電圧  $V_{ref}$  =  $V_{f2}$  +  $V_{31}$ を出力させる。これにより、第 1 の電流制御回路  $A_1$  の帰還作用によって第 1 電源  $V_{DD}$  の電圧がバンドギャップ電圧以下であっても電圧依存特性がより小さくなる様にしている。

#### [0037]

本発明の第2の実施の形態に係る基準電圧発生回路によれば、第1の実施の形態に係る基準電圧発生回路と同様に、シリコンのバンドギャップ電圧(約1.2 V)以下の低い電圧領域でも、温度依存の無い基準電圧を発生し、バンドギャップ電圧以下等の低電圧電源でも電源電圧変動の非常に小さい理想的な出力電圧を得ることができる。又、本発明の第2の実施の形態に係る基準電圧発生回路によれば、使用される抵抗素子の温度依存性による出力電圧の歪みを補正し、V<sub>f</sub>特性やV<sub>BE</sub>特性等のばらつきに対してもそれを補正する様に動作するため、より高精度な基準電圧を発生できる。これにより、本発明の第2の実施の形態に係る基準電圧発生回路が基準電圧を供給するアナログ回路等の半導体集積回路の制度を向上でき、半導体集積回路の製品としての付加価値を高めることができる。

### [0038]

# (第3の実施の形態)

図3で示した第1の実施の形態に係る基準電圧発生回路では、第1及び第2の基準電圧発生素子としてバイポーラトランジスタを用いる場合を例示したが、基準電圧発生素子として、ダイオード接続されたMOSトランジスタを採用することも可能であり、ダイオード接続されたMOSトランジスタの弱反転領域特性を利用しても同様の効果が得られる。即ち、図8に示す第3の実施の形態に係る基準電圧発生回路では、図3に示した基準電圧発生回路のpnpトランジスタQ1,Q2のエミッタ・コレクタ(ベース)間の代わりに、

20

30

40

50

ダイオード接続された n M O S トランジスタ N  $_1$  , N  $_2$  のドレイン ( ゲート ) - ソース間を接続し置き換えている。

#### [0039]

図1に示したプロック図の第1の電流変換回路C1は、図8に示す第3の実施の形態に 係る基準電圧発生回路では、第1電源V<sub>DD</sub>と第2電源(GND)間に設けられ第2電源( GND)に一端を接続されたダイオード接続されたnMOSトランジスタ(第1の基準電 圧発生素子) N っと、第 2 電源( G N D )に一端を接続された、ダイオード接続された n  $MOSトランジスタ(第1の基準電圧発生素子)<math>N_2$ より電流密度の低いダイオード接続 されたnMOSトランジスタ(第2の基準電圧発生素子)N₁と第1の抵抗素子R₁₁から なる直列回路(N╴,R ₁ ₁)と、ダイオード接続されたnMOSトランジスタ(第1の基 準電圧発生素子)Nゥに発生する弱反転領域特性で規定される第1の電圧とダイオード接 続されたnMOSトランジスタ(第2の基準電圧発生素子)Nィに発生する弱反転領域特 性で規定される電圧と第1の抵抗素子Rュュに発生する電圧Vュュの和(Vュ+Vュュ)となる 第2の電圧を比較しダイオード接続されたnMOSトランジスタ(第1の基準電圧発生素 子) N ₂ 及び直列回路( N ₁ , R ₁ ₁ ) に一定の比で電流を供給し第1の電圧と第2の電圧が 等しくなる様に制御する第1の電流制御回路( $A_1$ , $P_0$ )とを備える。第1の電流制御回 路(A<sub>1</sub>,P<sub>0</sub>)は、第1の電圧を負(-)入力端子に接続し、第2の電圧を正(+)入力 端子に接続し、第1の電圧と第2の電圧を比較する第1差動増幅回路A₁と、第1差動増 幅回路A₁の出力をゲートに入力するpMOSトランジスタ(第1電流制御トランジスタ ) P<sub>0</sub>とを備える。そして、第1の電流変換回路 C<sub>11</sub>は、ダイオード接続された n M O S トランジスタ(第1の基準電圧発生素子)N₂の弱反転領域特性で規定される電圧 V₂とダ イオード接続されたnMOSトランジスタ(第2の基準電圧発生素子)N<sub>1</sub>の弱反転領域 特性で規定される電圧 $V_1$ との差 $V_{11}$  =  $V_2$  -  $V_1$ から正の温度依存を持った第1の電流量 Ⅰ₁₁に変換する。

#### [0040]

第 2 の n M O S トランジスタ(第 2 の基準電圧発生素子) N  $_1$  は、図 3 に示した第 1 の実施の形態に係る基準電圧発生回路の Q  $_1$  と同様に、それぞれのチャネル長 L が等い複数個の n M O S トランジスタ N  $_{11}$  , N  $_{12}$  ,・・・・・, N  $_{1n}$  を並列接続されている。第 2 の n M O S トランジスタ(第 2 の基準電圧発生素子) N  $_1$  の並列接続されたすべてのチャネル幅 W の合計を W  $_{N1}$  、第 1 の n M O S トランジスタ(第 1 の基準電圧発生素子) N  $_2$  のチャネル幅 W を W  $_{N2}$  とし、それぞれのチャネル長 L が等しい第 2 、第 1 の n M O S トランジスタ N  $_1$  , N  $_2$  のゲート・ソース間電圧を V  $_{G1}$  , V  $_{G2}$  とし、 n M O S トランジスタの弱反転領域における V  $_{G3}$  - In ( I  $_{DS}$  ) 特性の傾きを 1 / ( V  $_T$  ) とする。第 2 、第 1 の n M O S トランジスタ N  $_1$  , N  $_2$  の 引 反転領域の直線領域で動作する様に設定すると、この V  $_T$  は温度比例することから V  $_1$  には、

$V_{11} = I_{11} \times R_{11} = V_T \times In((W_{N1}/W_{N2}) \times (I_{12}/I_{11}))$  … (15) の電圧を発生し、図3に示す第1の実施の形態に係る基準電圧発生回路と同等の動作特性を示し同等の効果を得られる。

#### [0041]

図 1 に示したブロック図の第 2 の電流変換回路  $C_{12}$ は、図 8 に示す第 3 の実施の形態に係る基準電圧発生回路では、ダイオード接続された n M O S トランジスタ(第 1 の基準電圧発生素子)  $N_2$ の弱反転領域特性で規定される電圧  $V_2$ を入力電圧とし第 2 電源(G N D )を一端に接続された第 2 の抵抗素子  $R_{20}$ の他端が入力電圧と等しくなる様に電流を制御する第 2 の電流制御回路( $A_2$ ,  $P_{20}$ 、  $P_{21}$ )を備え、負の温度依存を持った第 2 の電流量  $I_{21}$ に変換する。第 2 の電流制御回路( $A_2$ ,  $P_{20}$ 、  $P_{21}$ )は、 n M O S トランジスタ(第 1 の基準電圧発生素子)  $N_2$ の弱反転領域特性で規定される電圧  $V_2$ を負( - )入力端子に接続し、第 2 の抵抗素子  $R_{20}$ の他端を正( + )入力端子に接続した第 2 差動増幅回路  $A_2$ と、第 2 差動増幅回路  $A_2$ の出力をゲートに入力する  $P_2$ 0 M O S トランジスタ(第 2 電流制御トランジスタ)  $P_{20}$ 0 及び  $P_2$ 1 M O S トランジスタ(第 3 電流制御トランジスタ)  $P_2$ 1

とを備える。 pMOSトランジスタ(第2電流制御トランジスタ)  $P_{20}$ と pMOSトランジスタ(第3電流制御トランジスタ)  $P_{21}$  とは、カレントミラー回路を構成している。

#### [0042]

図 1 に示したブロック図の電圧加算回路  $C_{16}$ は、図 8 に示す第 3 の実施の形態に係る基準電圧発生回路では、第 1 電源  $V_{DD}$ と第 2 電源(G N D ) 間に設けられ一端を直列回路( $N_1$ ,  $R_{11}$ )に直列接続され他端に第 1 の電流制御回路  $A_1$ の出力電流に応じた電流が供給される第 3 の抵抗素子  $R_{31}$ を設け、この第 3 の抵抗素子  $R_{31}$ の一端に第 2 の電流変換回路  $C_{12}$ の出力電流  $I_{21}$ を供給することで、第 3 の抵抗素子  $R_{31}$ に正の温度依存を持った第 1 の電流量  $I_{11}$  から負の温度依存を持った第 2 の電流量  $I_{21}$ を減じた第 3 の電流量  $I_{31}$  =  $I_{11}$  -  $I_{21}$  を発生させ、第 3 の抵抗素子  $R_{31}$  の他端に温度補償された電源電圧に依存しないバンドギャップ電圧以下の電圧  $V_{ref}$  =  $V_2$  +  $V_{31}$ を出力させる。これにより、第 1 の電流制御回路  $A_1$  の帰還作用によって第 1 電源  $V_{DD}$  の電圧がバンドギャップ電圧以下であっても電圧依存がより小さくなる様にしている。

### [0043]

本発明の第3の実施の形態に係る基準電圧発生回路によれば、第1及び第2の実施の形態に係る基準電圧発生回路と同様に、シリコンのバンドギャップ電圧以下の低い電圧領域でも、温度依存の無い基準電圧を発生し、電源電圧変動の非常に小さい理想的な出力電圧を得ることができる。又、本発明の第3の実施の形態に係る基準電圧発生回路によれば、使用される抵抗素子の温度依存性による出力電圧の歪みを補正し、MOSトランジスタ閾値電圧特性等のばらつきに対してもそれを補正する様に動作するため、より高精度な基準電圧を発生できる。これにより、本発明の第3の実施の形態に係る基準電圧発生回路によれば、アナログ回路等の半導体集積回路の精度を向上でき、半導体集積回路の製品としての付加価値を高めることができる。

### [0044]

### (第4の実施の形態)

## [0045]

npnトランジスタ $Q_{11}$ ,  $Q_{12}$ の $V_{BE}$ をそれぞれ $V_{BEQ11}$ ,  $V_{BEQ12}$ とすると、エミッタ電流密度の違いから $V_{11}$  =  $V_{BEQ12}$  -  $V_{BEQ11}$ なる電位差を発生する。第 1 差動増幅回路 A  $_1$  は正(+)入力端子と負(-)入力端子を同電位に保つ様にフィードバック制御し、抵抗素子 $R_{11}$ によって $V_{BE}$ 電位差 $V_{11}$ に応じた電流  $I_{11}$ を発生する電流変換回路を構成する。よって、この場合も図 3 に示した第 1 の実施の形態に係る基準電圧発生回路と同等の動作特性を示し同等の効果が得られる。

#### [0046]

本発明の第4の実施の形態に係る基準電圧発生回路によれば、第1~第3の実施の形態に係る基準電圧発生回路と同様に、シリコンのバンドギャップ電圧以下の低い電圧領域でも、温度依存の無い基準電圧を発生し、電源電圧変動の非常に小さい理想的な出力電圧を得ることができる。又、本発明の第4の実施の形態に係る基準電圧発生回路によれば、使用される抵抗素子の温度依存性による出力電圧の歪みを補正し、V<sub>f</sub>特性やV<sub>BE</sub>特性等のばらつきに対してもそれを補正する様に動作するため、より高精度な基準電圧を発生できる。これにより、本発明の第4の実施の形態に係る基準電圧発生回路によれば、アナログ回路等の半導体集積回路の精度が向上し、半導体集積回路の製品としての付加価値を高めることができる。

# [0047]

(第5の実施の形態)

20

10

30

20

30

50

### [0048]

抵抗素子 R  $_{32}$  と p n p トランジスタ Q  $_2$  との接続点(第 1 ノード) X  $_{12}$  ( = X  $_{10}$  ) と、抵抗素子 R  $_{31}$  と抵抗素子 R  $_{11}$  の接続点(第 2 ノード) X  $_{11}$  は共に第 1 差動増幅回路 A  $_1$  によってフィードバック制御され同電位(イマジナリショート)となるため、図 3 に示した第 1 の実施の形態に係る基準電圧発生回路と同等の動作特性を示し同等の効果が得られる。 【 0 0 4 9 】

本発明の第5の実施の形態に係る基準電圧発生回路によれば、第1~第4の実施の形態に係る基準電圧発生回路と同様に、シリコンのバンドギャップ電圧以下の低い電圧領域でも、温度依存の無い基準電圧を発生し、電源電圧変動の非常に小さい理想的な出力電圧を得ることができる。又、本発明の第5の実施の形態に係る基準電圧発生回路によれば、使用される抵抗素子の温度依存性による出力電圧の歪みを補正し、V<sub>f</sub>特性やV<sub>BE</sub>特性等のばらつきに対してもそれを補正する様に動作するため、より高精度な基準電圧を発生できる。これにより、本発明の第5の実施の形態に係る基準電圧発生回路によれば、アナログ回路等の半導体集積回路の精度が向上し、半導体集積回路の製品としての付加価値を高めることができる。

### [0050]

### (第6の実施の形態)

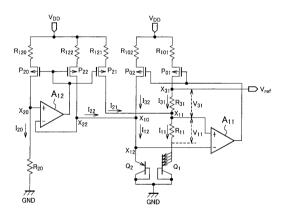

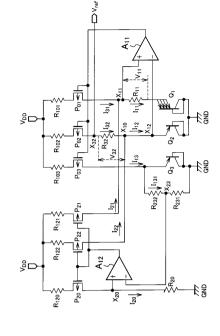

図 1 1 に本発明の第 6 の実施の形態に係る基準電圧発生回路を示す。図 1 1 では、図 3 に示した第 1 の実施の形態に係る基準電圧発生回路の p M O S トランジスタ(第 1 電流制御トランジスタ) P  $_0$ と抵抗素子 R  $_{32}$ の代わりに、 V  $_{DD}$ 電源と出力端子 V  $_{ref}$ 間に直列接続された抵抗素子 R  $_{101}$ と p M O S トランジスタ(第 1 電流制御トランジスタ) P  $_{01}$ と、 V  $_{D}$  電源と p n p トランジスタQ  $_2$  のエミッタ間に直列接続された抵抗素子 R  $_{102}$ と p M O S トランジスタ(第 1 電流制御トランジスタ) P  $_{02}$ を設置し、 p M O S トランジスタ(第 1 電流制御トランジスタ) P  $_{01}$  , P  $_{02}$  のゲートには第 1 差動増幅回路 A  $_{11}$  の出力を接続する。又、 p M O S トランジスタ P  $_{20}$  , P  $_{21}$  , P  $_{22}$  のソースと V  $_{DD}$  電源間にそれぞれ抵抗素子 R  $_{120}$  , R  $_{121}$  , R  $_{122}$  を設置している。抵抗素子 R  $_{101}$  , R  $_{102}$  と p M O S トランジスタ(第 1 電流制御トランジスタ) P  $_{01}$  , P  $_{02}$  は第 1 差動増幅回路 A  $_{11}$  からのフィードバック制御によって、所望の電流比を持った I  $_{31}$  , I  $_{32}$  を出力するカレントミラー回路として動作する。

# [0051]

20

30

50

に接続し、ゲートを第1差動増幅器  $A_{11}$ の出力端子に接続した第1電流制御トランジスタ  $P_{01}$ とを備える。

### [0052]

又、図1に示したブロック図の第2の電流変換回路 $C_{12}$ は、図11では、第1電源 $V_{DD}$ と第2電源(G N D)の第3電流経路に設けられ、第2電源(G N D)の電位に一端の電位が固定され、他端を第3ノード $X_{20}$ に接続した第2の抵抗素子 $R_{20}$ と、第3ノード $X_{20}$ と第1電源 $V_{DD}$ 間に抵抗 $R_{120}$ を介して接続された第2電流制御トランジスタ $P_{20}$ と、第1ノード $X_{12}$ (=  $X_{10}$  =  $X_{22}$ )を負(- )入力端子に、第3ノード $X_{20}$ を正(+ )入力端子に接続した第2差動増幅器 $A_{12}$ の負(- )入力端子に接続した第2差動増幅器 $A_{12}$ の負(- )入力端子の間に抵抗 $R_{122}$ を介して接続され、ゲートに第2差動増幅器 $A_{12}$ の出力を接続し、第2電流制御トランジスタ $P_{20}$ とカレントミラーを構成する第3電流制御トランジスタ $P_{20}$ とカレントミラーを構成する第3電流制御トランジスタ $P_{20}$ とカレントミラーを構成する第3電流制御トランジスタ $P_{20}$ とカレントミラーを構成する第4電流制御トランジスタ $P_{21}$ とを更に備える。第2の電流変換回路 $C_{12}$ は、第2差動増幅器 $A_{12}$ の負(- )入力端子と、正(+ )入力端子の電位とが等しくなる様に、第2~第4電流制御トランジスタ $P_{20}$ , $P_{22}$ , $P_{21}$ を制御し、第4電流制御トランジスタ $P_{21}$  から負の温度依存性を持った第2の電流量 $I_{21}$ の電流を第2ノード $X_{11}$ に出力する。

# [0053]

図 1 に示したブロック図の電圧加算回路  $C_{16}$ は、図 1 1 では、出力ノード  $X_{31}$ と第 2 ノード  $X_{11}$ 間に接続された第 3 の抵抗素子 $R_{31}$ を更に備え、この第 3 の抵抗素子 $R_{31}$ に第 1 の電流量  $I_{11}$ から第 2 の電流量  $I_{21}$ を減じた電流量の電流を、第 3 の電流量  $I_{31}$ の電流として流し、第 3 の抵抗素子 $R_{31}$ の両端子間に正の温度依存性を有する温度特性補償電圧  $V_{31}$ を発生させ、出力ノード  $X_{31}$ から基準電圧 V refを出力する。

#### [0054]

# [0055]

第6の実施の形態に係る基準電圧発生回路において、抵抗素子  $R_{120}$  ,  $R_{121}$  ,  $R_{122}$  は、トランジスタ  $P_{20}$  ,  $P_{21}$  ,  $P_{22}$  の素子相対ばらつきやチャネル長変調による設計値からのずれを改善させ出力電流  $I_{20}$  ,  $I_{21}$  ,  $I_{22}$  の精度を向上させる効果を持つ。図11に示した基準電圧発生回路の場合も図3に示した第1の実施の形態に係る基準電圧発生回路と同様に、 $I_{31}$  =  $I_{11}$  -  $I_{21}$ なる電流を発生し、式(13)で示す  $V_{ref}$  出力電圧を得る。よって、図3に示した第1の実施の形態に係る基準電圧発生回路と同等の動作特性を示し同等の効果が得られる。

### [0056]

本発明の第6の実施の形態に係る基準電圧発生回路によれば、第1~第5の実施の形態に係る基準電圧発生回路と同様に、シリコンのバンドギャップ電圧以下の低い電圧領域でも、温度依存の無い基準電圧を発生し、電源電圧変動の非常に小さい理想的な出力電圧を得ることができる。又、本発明の第6の実施の形態に係る基準電圧発生回路によれば、使用される抵抗素子の温度依存性による出力電圧の歪みを補正し、Vҕ特性やVBE特性等のばらつきに対してもそれを補正する様に動作するため、より高精度な基準電圧を発生できる。これにより、本発明の第6の実施の形態に係る基準電圧発生回路によれば、アナログ

20

30

40

50

回路等の半導体集積回路の精度が向上し、半導体集積回路の製品としての付加価値を高めることができる。

### [0057]

(第7の実施の形態)

図13に本発明の第7の実施の形態に係る基準電圧発生回路を示す。図13では、図3に示した第1の実施の形態に係る基準電圧発生回路のpMOShランジスタ $P_{20}$ ,  $P_{21}$ ,  $P_{22}$ の代わりに、ソースを $V_{DD}$ 電源に接続しゲートを第2差動増幅回路  $A_2$ に接続した pMOSh ランジスタ $P_{220}$ と、それぞれ一端をpMOSh ランジスタ $P_{220}$ のドレインに接続した抵抗素子 $R_{220}$ ,  $R_{221}$ ,  $R_{222}$ を設置し、抵抗  $R_{220}$ の他端を第3ノード $X_{20}$ において抵抗素子 $X_{20}$ の他端に接続し、抵抗素子 $X_{221}$ の他端を抵抗素子 $X_{31}$ と抵抗素子 $X_{11}$ の接続点(第2ノード) $X_{11}$ に接続し、抵抗素子 $X_{222}$ の他端を抵抗素子 $X_{32}$ と $X_{32}$ と $X_{32}$ 0  $X_{32}$ 0  $X_{33}$ 0  $X_{33}$ 0  $X_{34}$ 0  $X_{35}$ 0

#### [0058]

抵抗素子 R  $_{220}$ は、図 3 の基準電圧発生回路と同様に第 2 差動増幅回路 A  $_{2}$ によってフィードバック制御された電流 I  $_{20}$  = V  $_{BEO2}$  / R  $_{20}$ が印加される。

#### [0059]

ここで、抵抗素子 R  $_{220}$  の他端の接続された第 3 ノード X  $_{20}$  と抵抗素子 R  $_{222}$  の他端の接続されたノード X  $_{22}$  とは第 2 差動増幅回路 A  $_2$  によって同電位(イマジナリショート)となり、抵抗素子 R  $_{222}$  の他端の接続されたノード X  $_{12}$  と抵抗素子 R  $_{221}$  の他端の接続されたノード X  $_{14}$  とは第 1 差動増幅回路 A  $_1$  によって同電位(イマジナリショート)となる。結果として、第 3 ノード X  $_{20}$  ,ノード X  $_{22}$  ,ノード X  $_{12}$  ,ノード X  $_{11}$  は、それぞれ第 1 差動増幅回路 A  $_1$  及び第 2 差動増幅回路 A  $_2$  によって同電位(イマジナリショート)となるため、電流 I  $_{20}$  , I  $_{21}$  , I  $_{22}$  はそれぞれ抵抗素子 R  $_{220}$  , R  $_{221}$  , R  $_{222}$  の抵抗値に反比例する電流を出力する。よって、図 3 に示した第 1 の実施の形態に係る基準電圧発生回路と同等の動作特性を示し同等の効果が得られる。

#### [0060]

本発明の第7の実施の形態に係る基準電圧発生回路によれば、第1~第6の実施の形態に係る基準電圧発生回路と同様に、シリコンのバンドギャップ電圧以下の低い電圧領域でも、温度依存の無い基準電圧を発生し、電源電圧変動の非常に小さい理想的な出力電圧を得ることができる。又、本発明の第7の実施の形態に係る基準電圧発生回路によれば、使用される抵抗素子の温度依存性による出力電圧の歪みを補正し、Vҕ特性やVBE特性等のばらつきに対してもそれを補正する様に動作するため、より高精度な基準電圧を発生できる。これにより、本発明の第7の実施の形態に係る基準電圧発生回路によれば、アナログ回路等の半導体集積回路の精度が向上し、半導体集積回路の製品としての付加価値を高めることができる。

### [0061]

(第8の実施の形態)

# [0062]

p n p トランジスタQ  $_3$ には抵抗素子 R  $_{33}$ の値に応じた V  $_{BE}$ 電圧 V  $_{BEQ3}$ を発生する。又、第 2 差動増幅回路 A  $_2$ は正(+)入力端子と負( - )入力端子を同電位に保つ様にフィードバック制御し、 V  $_{BEQ3}$ を抵抗素子 R  $_{20}$ によって電圧電流変換しカレントミラー構成の M O S トランジスタ P  $_{20}$  , P  $_{21}$  , P  $_{22}$ によりドレイン電流 I  $_{20}$  , I  $_{21}$  , I  $_{22}$ を出力する電圧電流変換回路を構成する。この V  $_{BEQ3}$ は、図 3 に示した基準電圧回路の V  $_{BEQ2}$ と同様に負の温度依存性を持った電圧となるため、この場合も図 3 に示した第 1 の実施の形態

20

30

40

50

に係る基準電圧発生回路と同等の動作特性を示し同等の効果が得られる。

#### [0063]

本発明の第8の実施の形態に係る基準電圧発生回路によれば、第1~第7の実施の形態に係る基準電圧発生回路と同様に、シリコンのバンドギャップ電圧以下の低い電圧領域でも、温度依存の無い基準電圧を発生し、電源電圧変動の非常に小さい理想的な出力電圧を得ることができる。又、本発明の第8の実施の形態に係る基準電圧発生回路によれば、使用される抵抗素子の温度依存性による出力電圧の歪みを補正し、V<sub>f</sub>特性やV<sub>BE</sub>特性等のばらつきに対してもそれを補正する様に動作するため、より高精度な基準電圧を発生できる。これにより、本発明の第8の実施の形態に係る基準電圧発生回路によれば、アナログ回路等の半導体集積回路の精度が向上し、半導体集積回路の製品としての付加価値を高めることができる。

### [0064]

#### (第9の実施の形態)

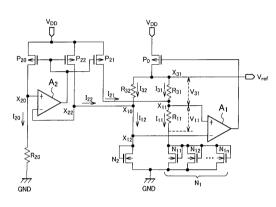

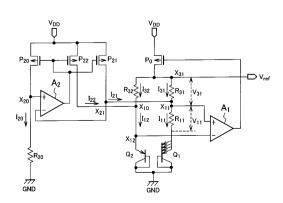

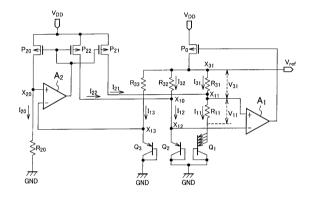

図 1 5 に本発明の第 9 の実施の形態に係る基準電圧発生回路を示す。図 1 5 では、図 1 1 に示した第 6 の実施の形態に係る基準電圧発生回路の第 1 電源  $V_{DD}$ と第 2 電源(G N D )間に直列接続された抵抗素子  $R_{103}$ , p M O S トランジスタ  $P_{03}$ , p n p トランジスタ  $Q_3$ と、 p n p トランジスタ  $Q_3$ のエミッタ端子と G N D 電源間に直列接続された抵抗素子  $R_{232}$ と  $R_{231}$ を追加している。

### [0065]

即ち、図1に示す基準電圧発生回路の第1の電流変換回路C11は、図15では、第1電 源Vppと第2電源(GND)の第1電流経路に設けられ、第2電源(GND)の電位に一 端(コレクタ端子)の電位が固定され、他端(エミッタ端子)を第1ノードXィゥに接続し 、この第1ノードX<sub>12</sub>に負の温度依存性を有する第1基準電圧を発生する第1の基準電圧 発生素子(pnpトランジスタ)Q。と、第1電源Vnnと第2電源(GND)の第2電流 経路に設けられ、第2電源(GND)の電位に一端(コレクタ端子)の電位が固定され、 第1の基準電圧発生素子(pnpトランジスタ)Qゥより電流密度の低く、他端(エミッ タ端子)に負の温度依存性を有する第2基準電圧を発生する第2の基準電圧発生素子(p n p トランジスタ) Q <sub>1</sub> と、 第 1 電源 V <sub>DD</sub>と第 2 電源 ( G N D ) の第 3 電流経路に設けら れ、第2電源(GND)の電位に一端(コレクタ端子)の電位が固定され、他端(エミッ タ端子)に負の温度依存性を有する第3基準電圧を発生する第3の基準電圧発生素子(p npトランジスタ)Q₂と、この第2の基準電圧発生素子(pnpトランジスタ)Q₁の他 端に一端を接続され、他端を第2ノードX<sub>11</sub>に接続する第1の抵抗素子R<sub>11</sub>からなる直列 回路(Q<sub>1</sub>, R<sub>11</sub>)と、第1基準電圧と、第2ノードX<sub>11</sub>に生じる第2基準電圧と第1の 抵抗素子R<sub>11</sub>に発生する電圧の和とを比較し、第1及び第2電流経路に一定の比で電流を 供給し、第1及び第2基準電圧の差から正の温度依存性を有する第1の電流量Ⅰィィを、第 1の抵抗素子R<sub>11</sub>に流す第1の電流制御回路(A<sub>11</sub>,P<sub>01</sub>)とを備える。第3の基準電圧 発生素子(pnpトランジスタ)Q<sub>3</sub>の他端(エミッタ端子)は、抵抗素子R<sub>103</sub>及びpM OSトランジスタP<sub>03</sub>を介して第1電源V<sub>DD</sub>に接続され、第3の基準電圧発生素子(pn pトランジスタ) Q ₃のエミッタ端子とコレクタ端子間には、抵抗素子 R ₂₃₂と抵抗素子 R <sub>231</sub>とが第4ノードX<sub>23</sub>で接続された直列回路が、並列接続されている。ここで、第1の 電流制御回路( $A_{11}$ ,  $P_{01}$ )は、第1ノード $X_{12}$ に一方の入力端子、第2ノード $X_{11}$ に他 方の入力端子を接続した第1差動増幅器A<sub>11</sub>と、第1電源V<sub>DD</sub>に抵抗R<sub>101</sub>を介して一端 を接続し、他端を第2電流経路に設けられ、基準電圧Vrefを出力する出力ノードX<sub>31</sub>に 接続し、ゲートを第1差動増幅器A11の出力端子に接続した第1電流制御トランジスタP 01とを備える。

# [0066]

図 1 に示したブロック図の第 2 の電流変換回路  $C_{12}$ は、図 1 5 では、第 1 電源  $V_{DD}$ と第 2 電源(G N D)の第 3 電流経路に設けられ、第 2 電源(G N D)の電位に一端の電位が固定され、他端を第 3 ノード  $X_{20}$ に接続した第 2 の抵抗素子  $X_{20}$ と、第 3 ノード  $X_{20}$ と第 1 電源  $Y_{DD}$ 間に抵抗  $X_{120}$ を介して接続された第 2 電流制御トランジスタ  $Y_{20}$ と、第 4 ノ

20

30

[0067]

図 1 に示したプロック図の電圧加算回路  $C_{16}$ は、図 1 5 では、出力ノード  $X_{32}$  と第 1 ノード  $X_{10}$  ( =  $X_{12}$  ) 間に接続された第 3 の抵抗素子 $R_{32}$ を更に備え、この第 3 の抵抗素子 $R_{32}$  に第 1 の電流量  $I_{11}$  から第 2 の電流量  $I_{21}$  を減じた電流量  $I_{31}$  に比例した電流量  $I_{32}$  の電流を第 3 の電流量  $I_{32}$  の電流として流し、第 3 の抵抗素子 $R_{32}$  の両端子間に正の温度依存性を有する温度特性補償電圧  $V_{32}$ を発生させ、出力ノード  $X_{32}$  から基準電圧  $V_{12}$  refを出力する。

### [0068]

即ち、図11に示した第6の実施の形態に係る基準電圧発生回路の p M O S トランジスタ  $P_{02}$ と p n p トランジスタ  $Q_2$ の接続点(第1ノード)  $X_{12}$ の代わりに抵抗素子  $R_{232}$ と  $R_{231}$ の接続点(第4ノード)  $X_{23}$ を第2差動増幅回路  $A_2$ の負(-)入力端子に接続し、抵抗素子  $R_{31}$ を廃止し p M O S トランジスタ  $P_{01}$ のドレインと抵抗素子  $R_{11}$ の他端を接続点(第2ノード)  $X_{11}$ で接続し第1差動増幅回路  $A_1$ の正(+)入力端子に接続し、替わりに p M O S トランジスタ  $P_{02}$ のドレインと p n p トランジスタ  $Q_2$ のエミッタ間に抵抗  $R_{32}$ を追加し、 p M O S トランジスタ  $P_{02}$ と抵抗  $R_{32}$ の接続点(出力ノード)  $X_{32}$ を出力端子  $V_{ref}$ としている。

### [0069]

この場合、抵抗素子 R  $_{101}$  と p M O S トランジスタ P  $_{01}$  及び抵抗素子 R  $_{102}$  と p M O S トランジスタ P  $_{02}$ で構成されるカレントミラー回路の電流比 I  $_{31}$  : I  $_{32}$  = 1 : m とし、抵抗素子 R  $_{120}$  と p M O S トランジスタ(第 2 電流制御トランジスタ) P  $_{20}$  及び抵抗素子 R  $_{121}$  と p M O S トランジスタ(第 3 電流制御トランジスタ) P  $_{21}$  及び抵抗素子 R  $_{122}$  と p M O S トランジスタ P  $_{22}$  で構成されるカレントミラー回路の電流比 I  $_{20}$  : I  $_{21}$  : I  $_{22}$  = p : q : (m × q)とし、抵抗素子 R  $_{32}$  に発生する電圧を V  $_{32}$  とすると、

$I_{12} = V_T \times ln((S_{Q1}/S_{Q2}) \times m)/R_{11} \times m$  ...(16) と表わせる。又、

$I_{22}$  = ( $V_{BEQ3}$  /  $R_{20}$ ) × ( $R_{231}$  / ( $R_{231}$  +  $R_{232}$ )) × (( $m \times q$ ) / p) ... (17) となり、出力電圧  $V_{ref}$  は、

$$V_{ref} = V_{BEQ2} + V_{32}$$

$$= V_{BEQ2} + R_{32} \times (I_{12} - I_{22})$$

$$= V_{BEQ2} + R_{32} \times (V_{T} \times In((S_{Q1} / S_{Q2}) \times m) / R_{11} \times m$$

$$- (V_{BEQ3} / R_{20}) \times (R_{231} / (R_{231} + R_{232})) \times ((m \times q) / p))$$

式(18)は式(13)と同様に $V_{DD}$ 電源の電圧に依存する項が無いので、 $V_{ref}$ は $V_{DD}$  依存の無い電圧として定電圧動作を行なう。又この場合、 $p_{RE}$  内  $p_{RE}$  トランジスタの $V_{RE}$  電圧、 $V_{BEQ_3}$  の温度依存の傾きを抵抗素子  $V_{REQ_3}$  により任意に変更でき、電圧電流変換後の電流  $V_{REQ_3}$  の設定自由度が増す。この場合も、図 3 に示した第 1 の実施の形態に係る基準電圧発生回路と同等の動作特性を示し同等の効果が得られる。

#### [0070]

本発明の第9の実施の形態に係る基準電圧発生回路によれば、第1~第8の実施の形態

に係る基準電圧発生回路と同様に、シリコンのバンドギャップ電圧以下の低い電圧領域で も、温度依存の無い基準電圧を発生し、電源電圧変動の非常に小さい理想的な出力電圧を 得ることができる。又、本発明の第9の実施の形態に係る基準電圧発生回路によれば、使 用される抵抗素子の温度依存性による出力電圧の歪みを補正し、V,特性やVઠҕ特性等の ばらつきに対してもそれを補正する様に動作するため、より高精度な基準電圧を発生でき る。これにより、本発明の第9の実施の形態に係る基準電圧発生回路によれば、アナログ 回路等の半導体集積回路の精度が向上し、半導体集積回路の製品としての付加価値を高め ることができる。

[0071]

(その他の実施の形態)

10

上記のように、本発明は第1~第9の実施の形態によって記載したが、この開示の一部 をなす論述及び図面は本発明を限定するものであると理解すべきではない。この開示から 当業者には様々な代替実施の形態、実施の形態及び運用技術が明らかとなろう。したがっ て、本発明の技術的範囲は上記の説明から妥当な特許請求の範囲に係る発明特定事項によ ってのみ定められるものである。

【図面の簡単な説明】

[0072]

- 【図1】本発明の第1~第9の実施の形態に係る基準電圧発生回路の論理的な構成を示す ブロック図である。

- 【図2】図2(a)は、図1の基準電圧発生回路の動作電圧の温度依存特性を模式的に示 す図で、図2(b)は、その動作電流の温度依存特性を模式的に示す図である。

- 【図3】本発明の第1の実施の形態に係る基準電圧発生回路の構成を示す回路図である。

- 【図4】図3の差動増幅回路の構成を示す回路図である。

- 【図5】図5(a)は、図3に示した本発明の第1の実施の形態に係る基準電圧発生回路 の動作電圧の温度依存特性を模式的に示す図で、図5(b)は、第1の実施の形態に係る 基準電圧発生回路の動作電流の温度依存特性を模式的に示す図である。

- 【図6】第1の実施の形態に係る基準電圧発生回路の出力電圧の電源電圧依存特性を示す 図である。

- 【図7】本発明の第2の実施の形態に係る基準電圧発生回路の構成を示す回路図である。

- 【図8】本発明の第3の実施の形態に係る基準電圧発生回路の構成を示す回路図である。

- 【図9】本発明の第4の実施の形態に係る基準電圧発生回路の構成を示す回路図である。

- 【図10】本発明の第5の実施の形態に係る基準電圧発生回路の構成を示す回路図である

【図11】本発明の第6の実施の形態に係る基準電圧発生回路の構成を示す回路図である

【図12】図11の差動増幅回路の構成を示す回路図である。

【図13】本発明の第7の実施の形態に係る基準電圧発生回路の構成を示す回路図である

【図14】本発明の第8の実施の形態に係る基準電圧発生回路の構成を示す回路図である

【図15】本発明の第9の実施の形態に係る基準電圧発生回路の構成を示す回路図である

【図16】比較例としての基準電圧発生回路の構成を示すブロック図である。

【図17】図16に示した基準電圧発生回路の動作電圧と動作電流の温度依存特性を模式 的に示す図である。

【図18】図16に示した基準電圧発生回路の電源電圧依存特性を示す図である。

【図19】基準電圧発生回路の他の比較例を示す回路図である。

【符号の説明】

[0073]

A<sub>1</sub>, A<sub>2</sub>, A<sub>11</sub>, A<sub>12</sub>...差動増幅回路

20

30

40

C<sub>01</sub>, C<sub>02</sub>...電流源回路

C<sub>03</sub>…カレントミラー回路

C<sub>11</sub>…第1の電流変換回路

C<sub>12</sub>…第2の電流変換回路

C <sub>13</sub> ... 電流減算回路

C<sub>14</sub>…電圧発生回路

C<sub>15</sub>...電流電圧変換回路

C<sub>16</sub>…第1の電圧加算回路

$D_1$ ,  $D_2$ ...  $\vec{y}$   $\vec{1}$

$N_1$ ,  $N_2$ ... n M O S F D  $\mathcal{Y}$   $\mathcal{X}$   $\mathcal{Y}$

$Q_{11}$ ,  $Q_{12}$ ... n p n h b b b b b c A b b c A b b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c A b c

$R_0$  ,  $R_1$  ,  $R_2$  ,  $R_{101}$  ,  $R_{102}$  ,  $R_{103}$  ,  $R_{111}$  ,  $R_{11}$  ,  $R_{120}$  ,  $R_{121}$  ,  $R_{122}$  ,  $R_{20}$  ,  $R_{220}$  ,  $R_{221}$  ,  $R_{222}$  ,  $R_{231}$  ,  $R_{232}$  ,  $R_{31}$  ,  $R_{32}$  ,  $R_{33}$ ...抵抗素子

R<sub>3</sub>, R<sub>4</sub>...ブリーダ抵抗

# 【図1】

# 【図2】

# 【図3】

【図4】

【図5】

【図7】

【図6】

【図8】

【図9】

【図11】

【図10】

【図12】

【図13】

【図15】

【図14】

【図16】

【図18】

【図17】

【図19】

### フロントページの続き

(74)代理人 100095500

弁理士 伊藤 正和

(74)代理人 100101247

弁理士 高橋 俊一

(74)代理人 100098327

弁理士 高松 俊雄

(72)発明者 諏訪部 裕之

神奈川県川崎市川崎区駅前本町25番地1 東芝マイクロエレクトロニクス株式会社内

(72)発明者 三村 安志

神奈川県川崎市川崎区駅前本町25番地1 東芝マイクロエレクトロニクス株式会社内

審査官 三島木 英宏

(56)参考文献 特開2004-192608(JP,A)

(58)調査した分野(Int.CI., DB名)

G05F 3/30