#### **ECE 498AL**

Programming Massively Parallel Processors

Lecture 6: CUDA Memories Part 2

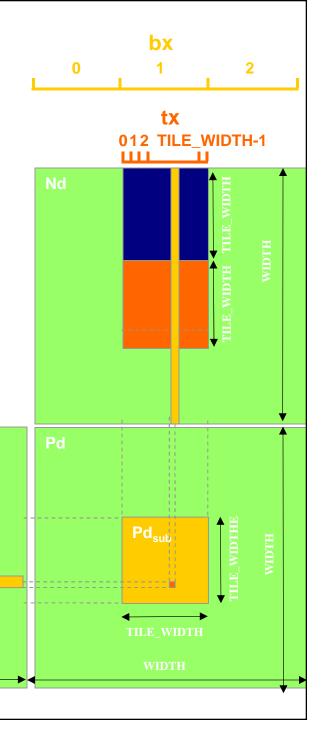

### Tiled Multiply

Break up the execution of the kernel into phases so that the data accesses in each phase is focused on one subset (tile) of Md and Nd

TILE WIDTH

© David Kirk/NVIDIA and Wen-mei W. Hwu, 2007-200 ECE498AL, University of Illinois, Urbana Champaign

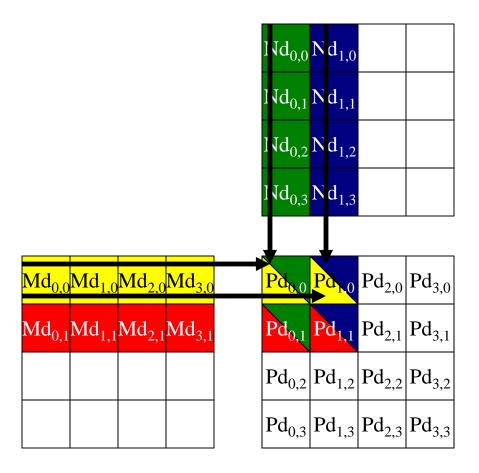

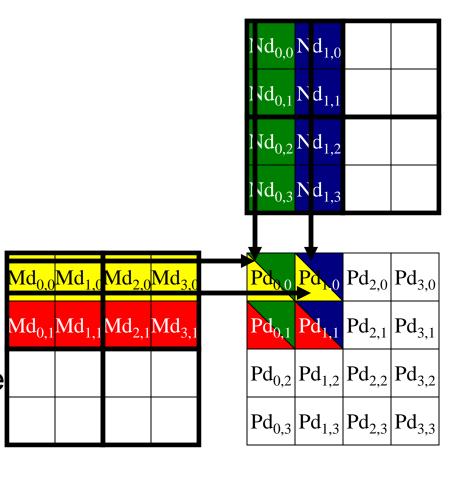

### A Small Example

## Every Md and Nd Element is used exactly twice in generating a 2X2 tile of P

Access order

| P <sub>0,0</sub>                               | P <sub>1,0</sub>                               | P <sub>0,1</sub>                    | P <sub>1,1</sub>                    |

|------------------------------------------------|------------------------------------------------|-------------------------------------|-------------------------------------|

| thread <sub>0,0</sub>                          | thread <sub>1,0</sub>                          | thread <sub>0,1</sub>               | thread <sub>1,1</sub>               |

| M <sub>0,0</sub> * N <sub>0,0</sub>            | M <sub>0,0</sub> * N <sub>1</sub>              | M <sub>0,1</sub> * N <sub>0,0</sub> | M <sub>0,1</sub> * N <sub>1</sub>   |

| M <sub>1</sub> <sub>0</sub> * N <sub>0,1</sub> | M <sub>1</sub> <sub>0</sub> * N <sub>1,1</sub> | M <sub>1,1</sub> * N <sub>0,1</sub> | M <sub>1,1</sub> * N <sub>1,1</sub> |

| M <sub>2,0</sub> * N <sub>0,2</sub>            | M <sub>2,0</sub> * N <sub>1,2</sub>            | M <sub>2,1</sub> * N <sub>0,2</sub> | M <sub>2,1</sub> * N <sub>1,2</sub> |

| M <sub>3,0</sub> * N <sub>0,3</sub>            | M <sub>3,0</sub> * N <sub>1,3</sub>            | M <sub>3,1</sub> * N <sub>0,3</sub> | M <sub>3,1</sub> * N <sub>1,3</sub> |

### Breaking Md and Nd into Tiles

- Break up the inner product loop of each thread into phases

- At the beginning of each phase, load the Md and Nd elements that everyone needs during the phase into shared memory

- Everyone access the Md and Nd elements from the shared memory during the phase

## Each phase of a Thread Block uses one tile from Md and one from Nd

|                  | Phase 1                                             |                                                    |                                                                                                                  | Phase 2                                             |                                                     | -                                                                                                               |

|------------------|-----------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| T <sub>0,0</sub> | $Md_{0,0}$ $\downarrow$ $Mds_{0,0}$                 | <b>Nd<sub>0,0</sub></b><br>↓<br>Nds <sub>0,0</sub> | PValue <sub>0,0</sub> +=<br>Mds <sub>0,0</sub> *Nds <sub>0,0</sub> +<br>Mds <sub>1,0</sub> *Nds <sub>0,1</sub>   | <b>Md<sub>2,0</sub></b><br>↓<br>Mds <sub>0,0</sub>  | $Nd_{0,2}$ $\downarrow$ $Nds_{0,0}$                 | PValue <sub>0,0</sub> +=<br>Mds <sub>0,0</sub> *Nds <sub>0,0</sub> +<br>Mds <sub>1,0</sub> *Nds <sub>0,1</sub>  |

| T <sub>1,0</sub> | <b>Md</b> <sub>1,0</sub><br>↓<br>Mds <sub>1,0</sub> | <b>Nd</b> <sub>1,0</sub> ↓ Nds <sub>1,0</sub>      | PValue <sub>1,0</sub> +=<br>Mds <sub>0,0</sub> *Nds <sub>1,0</sub> +<br>Mds <sub>1,0</sub> *Nds <sub>1,1</sub>   | <b>Md</b> <sub>3,0</sub><br>↓<br>Mds <sub>1,0</sub> | <b>Nd</b> <sub>1,2</sub><br>↓<br>Nds <sub>1,0</sub> | PValue <sub>1,0</sub> +=<br>Mds <sub>0,0</sub> *Nds <sub>1,0</sub> +<br>Mds <sub>1,0</sub> *Nds <sub>1,1</sub>  |

| T <sub>0,1</sub> | $Md_{0,1}$ $\downarrow$ $Mds_{0,1}$                 | $Nd_{0,1}$ $\downarrow$ $Nds_{0,1}$                | PdValue <sub>0,1</sub> +=<br>•Mds <sub>0,1</sub> *Nds <sub>0,0</sub> +<br>Mds <sub>1,1</sub> *Nds <sub>0,1</sub> | <b>Md</b> <sub>2,1</sub><br>↓<br>Mds <sub>0,1</sub> | $Nd_{0,3}$ $\downarrow$ $Nds_{0,1}$                 | PdValue <sub>0,1</sub> +=<br>Mds <sub>0,1</sub> *Nds <sub>0,0</sub> +<br>Mds <sub>1,1</sub> *Nds <sub>0,1</sub> |

| T <sub>1,1</sub> | <b>Md</b> <sub>1,1</sub><br>↓<br>Mds <sub>1,1</sub> | Nd <sub>1,1</sub> ↓ Nds <sub>1,1</sub>             | PdValue <sub>1,1</sub> +=<br>Mds <sub>0,1</sub> *Nds <sub>1,0</sub> +<br>Mds <sub>1,1</sub> *Nds <sub>1,1</sub>  | <b>Md</b> <sub>3,1</sub><br>↓<br>Mds <sub>1,1</sub> | <b>Nd</b> <sub>1,3</sub><br>↓<br>Nds <sub>1,1</sub> | PdValue <sub>1,1</sub> +=<br>Mds <sub>0,1</sub> *Nds <sub>1,0</sub> +<br>Mds <sub>1,1</sub> *Nds <sub>1,1</sub> |

time

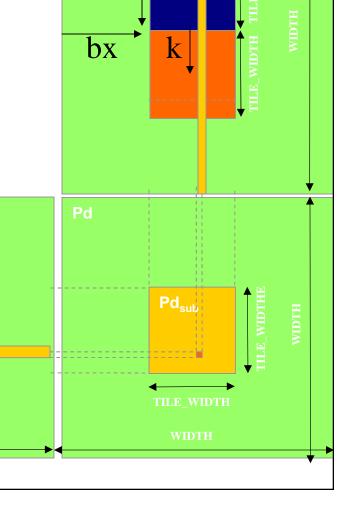

### Tiled Matrix Multiplication Kernel

```

global void MatrixMulKernel(float* Md, float* Nd, float* Pd, int Width)

shared float Mds[TILE WIDTH][TILE WIDTH];

shared float Nds[TILE WIDTH][TILE WIDTH];

int bx = blockIdx.x; int by = blockIdx.y;

int tx = threadIdx.x; int ty = threadIdx.y;

Identify the row and column of the Pd element to work on

int Row = by * TILE_WIDTH + ty;

int Col = bx * TILE_WIDTH + tx;

float Pvalue = 0;

// Loop over the Md and Nd tiles required to compute the Pd element

for (int m = 0; m < Width/TILE_WIDTH; ++m) {</pre>

Coolaborative loading of Md and Nd tiles into shared memory

Mds[ty][tx] = Md[Row*Width + (m*TILE WIDTH + tx)];

10.

Nds[ty][tx] = Nd[Col + (m*TILE_WIDTH + ty)*Width];

11.

__syncthreads();

for (int k = 0; k < TILE_WIDTH; ++k)

11.

12.

Pvalue += Mds[ty][k] * Nds[k][tx];

13.

Synchthreads();

14.

13.

Pd[Row*Width+Col] = Pvalue;

© David Kirk/NVIDIA and Wen-mei W. Hwu, 2007-2009

```

ECE498AL, University of Illinois, Urbana Champaign

# CUDA Code – Kernel Execution Configuration

#### First-order Size Considerations in G80

- Each thread block should have many threads

- TILE\_WIDTH of 16 gives 16\*16 = 256 threads

- There should be many thread blocks

- A 1024\*1024 Pd gives 64\*64 = 4096 Thread Blocks

- TILE\_WIDTH of 16 gives each SM 3 blocks, 768 threads (full capacity)

- Each thread block perform 2\*256 = 512 float loads from global memory for 256 \* (2\*16) = 8,192 mul/add operations.

- Memory bandwidth no longer a limiting factor

### Tiled Multiply

by

m

TILE WIDTH

- Each block computes one square sub-matrix Pd<sub>sub</sub> of size TILE\_WIDTH

- Each thread computes one element of Pd<sub>sub</sub>

m

012 TILE WIDTH-1

© David Kirk/NVIDIA and Wen-mei W. Hwu, 2007-200 ECE498AL, University of Illinois, Urbana Champaign

### G80 Shared Memory and Threading

- Each SM in G80 has 16KB shared memory

- SM size is implementation dependent!

- For TILE\_WIDTH = 16, each thread block uses 2\*256\*4B = 2KB of shared memory.

- The shared memory can potentially have up to 8 Thread Blocks actively executing

- This allows up to 8\*512 = 4,096 pending loads. (2 per thread, 256 threads per block)

- The threading model limits the number of thread blocks to 3 so shared memory is not the limiting factor here

- The next TILE\_WIDTH 32 would lead to 2\*32\*32\*4B= 8KB shared memory usage per thread block, allowing only up to two thread blocks active at the same time

- Using 16x16 tiling, we reduce the accesses to the global memory by a factor of 16

- The 86.4B/s bandwidth can now support (86.4/4)\*16 = 347.6 GFLOPS!

### Tiled Matrix Multiplication Kernel

```

global void MatrixMulKernel(float* Md, float* Nd, float* Pd, int Width)

shared float Mds[TILE_WIDTH][TILE_WIDTH];

shared float Nds[TILE WIDTH][TILE WIDTH];

int bx = blockIdx.x; int by = blockIdx.y;

int tx = threadIdx.x; int ty = threadIdx.y;

Identify the row and column of the Pd element to work on

int Row = by * TILE_WIDTH + ty;

int Col = bx * TILE_WIDTH + tx;

float Pvalue = 0;

// Loop over the Md and Nd tiles required to compute the Pd element

for (int m = 0; m < Width/TILE_WIDTH; ++m) {</pre>

Coolaborative loading of Md and Nd tiles into shared memory

Mds[ty][tx] = Md[Row*Width + (m*TILE WIDTH + tx)];

10.

Nds[ty][tx] = Nd[Col + (m*TILE_WIDTH + ty)*Width];

11.

__syncthreads();

for (int k = 0; k < TILE_WIDTH; ++k)

11.

12.

Pvalue += Mds[ty][k] * Nds[k][tx];

13.

Synchthreads();

14.

13.

Pd[Row*Width+Col] = Pvalue;

© David Kirk/NVIDIA and Wen-mei W. Hwu, 2007-2009

```

ECE498AL, University of Illinois, Urbana Champaign

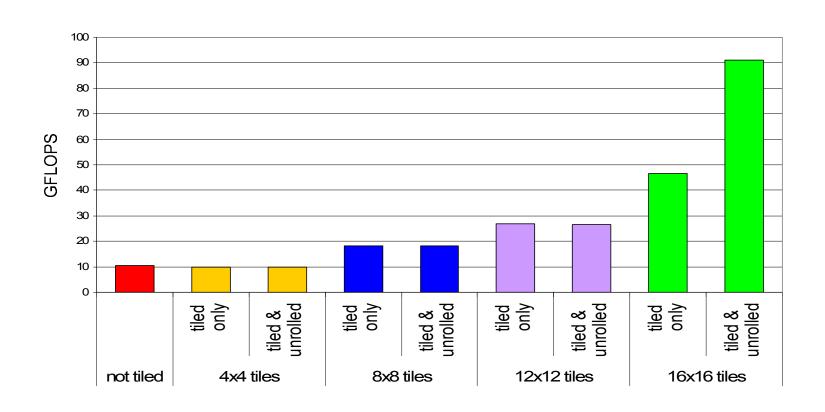

### Tiling Size Effects

# Summary- Typical Structure of a CUDA Program

```

Global variables declaration

host

__device__... __global__, __constant__, __texture__

Function prototypes

__global__ void kernelOne(...)

float handyFunction(...)

Main ()

allocate memory space on the device cudaMalloc(&d_GlbIVarPtr, bytes)

transfer data from host to device cudaMemCpy(d_GlbIVarPtr, h_GI...)

execution configuration setup

kernel call kernelOne<<execution configuration>>>( args... );

repeat

transfer results from device to host cudaMemCpy(h GlblVarPtr,...)

as needed

optional: compare against golden (host computed) solution

Kernel void kernelOne(type args,...)

variables declaration - __local__, __shared__

• automatic variables transparently assigned to registers or local memory

syncthreads()...

Other functions

float handyFunction(int inVar...);

```