MC68000

MC68000P10 | |

| 生産時期 | 1980年から1996年まで |

|---|---|

| 生産者 | モトローラ |

| CPU周波数 | 4 MHz から 20 MHz |

| 命令セット | M68000(32ビット) |

| パッケージ | 64ピンDIP |

MC68000(エムシーろくまんはっせん)、68000は米・モトローラ(フリースケール・セミコンダクタを経由して、現NXPセミコンダクターズ)が開発したMPU(MPUはマイクロプロセッサを指すのにモトローラが使った語でマイクロプロセッシングユニットの略)である。略して68K(ろくはちケー)などとも。後継MPUも含めた同一アーキテクチャのシリーズを総称するときは、680x0と呼称される。モトローラ自体は周辺LSIを含めてM68000ファミリと呼称した。MC型番は量産ロットで、量産先行品はXC型番となる。M68000ファミリは、Apple Macintosh や Apollo/Domain、NeXTcube、HP 9000、Sun-3、ソニーNEWS、NEC EWS4800、シャープX68000、DCL Uステーション[1][2]など様々なパソコンやワークステーションに採用された。オペレーティング・システムとしては、Mac OS、Domain/OS、NeXTSTEP、HP-UX、SunOS、CP/M-68K、OS-9/68000、NetBSDなどがある。

歴史

[編集]68000 は1976年に開始された MACSS (Motorola Advanced Computer System on Silicon) プロジェクトから出てきたものである。従来製品との互換性を考慮するような妥協したアーキテクチャにはしないということが開発の初期に決定されていた。これは、利用者がその新システムを一から新たに学ぶ必要があることを意味しており、一種の賭けだった。最終的に、6800系の周辺デバイスとのインタフェースの互換性だけは持つこととなったが、6800のコードは実行できないものとなった。しかし、その後の拡張における互換性には最大限の注意が払われ、68000に乗り換えさえすれば今後が保証されるようにした。例えば、CPUのレジスタは32ビット幅とされたが、外部バスはより小さく設計され、アドレスバスは24ビット幅であり、データバスは16ビット幅となっている。ちなみに、アドレスバスとデータバスはマルチプレクスされておらず分離されている[3]。MACSSチームはPDP-11やVAXシステムのようなミニコンピュータのプロセッサに影響を受けた。命令セットはハードウェアの制限よりもソフトウェア開発の観点で設計された。そこにはミニコンピュータでの開発になれた技術者がプログラミングしやすいものにしようとの考えがあった。

"68000" という名称は6800との連続性を想起させるよう選択されたが、これらの間に設計上の類似点はあまりない。集積されたトランジスタ数が68,000だったからとも言われているが、実際には70,000に近かった。

当時、8ビットから16ビットへの移行で熾烈な競争が繰り広げられていた。ナショナル セミコンダクターは1973年から1975年にかけてIMP-16とPACEというプロセッサで一歩先んじたが、使用したプロセス技術が原因で、性能に問題を抱えていた。次にテキサス・インスツルメンツがTMS9900をリリースしたが、広く使われるには至らなかった。そして1977年にインテルが8086をリリースした。しかし、モトローラのマーケティング部門は68000をより完全な16ビット設計にすることが重要と考えた。このため、68000はハードウェアとしては複雑なものとなった。複雑さの指標としてトランジスタ数を見ると、8086は29000個であり、68000は前述のように70000近い。

68000の単純な命令は4クロックサイクルで実行できたが、複雑な命令の実行にはもっと時間がかかった。8MHzの68000で、平均性能は約1MIPS弱だった。

典型的なプログラムで平均をとると、68000のコードはインテルのプロセッサよりも一命令あたりにできることが多く、コードのサイズが小さくて済んだ。また、8086が、8080との互換性を重視した結果、汎用レジスタの不足や実行速度の低下に苦しんだ事に対して、十分な数のレジスタと、当時としては先進的な内部設計のため、実行速度の面では8086に対して優位に立っていた。さらに68000は24ビットリニアアドレッシングによって最大16MBの連続するメモリ空間をサポートし、この空間内の任意のアドレスへのダイレクトアクセスを可能としている。これは開発当時としては非常に広大なメモリ空間だった。これに対し8086は従来の8080との間でソフトウェアのアセンブリ言語レベル(注: バイナリレベルではない)での互換性のため、従来と同じ16ビットのアドレッシングを「オフセット」とし、「セグメント」と称する(詳細はセグメント方式#x86を参照)16ビットレジスタの値を4ビットシフトしてベースアドレスとする、20ビット空間のノンリニアアドレッシングだった。そのため、64Kバイトを超えるデータやコードを扱うにはセグメントレジスタの値を適宜変更する必要があり、面倒であった。32ビットアドレッシングは、x86では1986年の80386で初めて可能になった。

このような事情から68000は8086と比較して学習が容易で使いやすく、開発者に好まれた。

オリジナルのMC68000は、3.5μmルールのHMOSプロセスで製造された。技術サンプルは1979年末に出荷された。量産チップは1980年に出荷され、当初のクロック周波数は4, 6, 8MHzだった。10MHz版は1981年、12.5MHz版が1982年に登場している。HMOSでは最高速の16.67MHz版 (12F) は1980年代終盤まで生産されなかった。

メモリ量の少ないシステム向けの低価格版として1982年に MC68008 が登場した。これは MC68000 の8ビットデータバス版であり、アドレスバスも当初は24ビットよりも縮小され、48ピンDIP版は20ビット。後の52ピンPLCCパッケージ版では22ビットである。MC68012 は後に31ビットアドレスバスで登場した。

68HC000はモトローラと日立製作所が1985年にリリースしたオリジナルとピン配置互換のHCMOS版である。モトローラのものは MC68HC000、日立のものはHD68HC000と呼ばれた。68HC000では8MHzから20MHzまでのクロック周波数が可能となった。またCMOS化されただけでオリジナルと機能が全く変わらず、かつ電力消費が低減されている。オリジナル版は25℃の環境で約1.35ワットを消費した(クロック周波数に依存しない)。一方、MC68HC000は8MHzで0.13ワット、20MHzで0.38ワットしか消費しない。なお、CMOSとは異なり、HMOS回路の電力消費はスイッチング時も何もしていないときも一定である。従って、クロック周波数が違っても電力消費はほとんど変化しない。ただし、周囲の気温には影響される。

モトローラは1990年、MC68HC001をリリースした[4]。このチップは68HC000と仕様がほぼ共通であるが、データバスに16ビット幅と8ビット幅の2つのモードが用意されており、リセット時のピンへの入力でモード選択が行えるようになっていた。従って、このチップは68008の代替として 8ビットメモリを使った安価なシステムで利用できた。

HMOS版の68000はいくつかのセカンドソース企業で製造された。日立 (HD68000)、Mostek (MK68000)、ロックウェル (R68000)、シグネティックス (SCN68000)、Thomson/SGS-Thomson (EF68000, TS68000)、東芝 (1988年発売。TMP68000を含めたTLCS-68000ファミリー) などである。東芝はCMOS版の68HC000のセカンドソースでもあった (TMP68HC000)。また、後にシグネティックスがアーキテクチャ互換のSCC68070を製造した。 SCC68070は現在フィリップスが版権を持つ。

68000は数々のマイクロコントローラや組み込み用プロセッサのベースにもなった。1989年、モトローラはMC68302通信プロセッサをリリースした。これが68000CPUコアを使用した最初のマイクロコントローラだった。このコアはCMOS版の68HC000をベースとしているが、8ビットの6800周辺チップとのインタフェース機能が省略されている。1991年、モトローラはここからプロセッサ部分だけを抜き出したMC68EC000をリリースした[5]。

モトローラは68EC000コアを使ったいくつかのマイクロコントローラを開発した。MC68306とMC68307は汎用マイクロコントローラ、MC68322 "Bandit" はプリンターコントローラ、MC68356はモデム用、MC68328 DragonBallは携帯機器向けだった。他のマイクロコントローラとして683XXファミリーは、より強力なCPU32プロセッサコアを使っていた。

68EC000ベースの683XXマイクロコントローラの一部にはスタティック版の68EC000コアが使われた。この場合クロックを遅くしたり停止させたりして電力消費を抑えることができる。1996年、モトローラはこのスタティックコアをプロセッサとして独立させ、MC68SEC000としてリリースした[6]。

モトローラは1996年、HMOS版MC68000とMC68008の製造を終了した[7]。生産終了の予告は1994年末ごろなされた。モトローラの通常の手順からいけば、1995年まで注文を受け付け、最後の出荷は1996年になったということになる。その後スピンオフしたフリースケール・セミコンダクタは現在もMC68HC000、MC68HC001、MC68EC000、MC68SEC000を製造販売し続けている。また、MC68302やMC68306マイクロコントローラやその後のDragonBallファミリーも生産し続けている。68000のアーキテクチャを受け継いだ680x0、CPU32、ColdFireも生産されている。

後継のMC68020からは外部データバス、アドレスバス共に32ビットの、名実共に32ビットのCPUとなり、コプロセッサがサポートされた。ソフトウェア的には、アドレッシングモードが拡張されたほか、ユーザーモードではほぼMC68000の上位互換だった。一部互換性のない部分は、存在しない命令を実行しようとしたときに割り込みでトラップ処理することで、ソフト的に吸収することができた。このMC68020や、後継のMC68030は数多くのワークステーションで採用された。

なおRISCであるPowerPCシリーズとの互換性はなく、同プロセッサを搭載したMacintoshではMC68LC040をエミュレーションしている。

RISC技術を採用したColdFireシリーズは、68000から使用頻度の低い命令の多くを削除した下位互換の組み込み用プロセッサである。

利用例

[編集]

68000は1980年代前半には比較的高価なシステムに使われた。

- マルチユーザー型のパーソナルコンピュータ : WICAT 150、タンディ TRS-80 Model 16、Fortune 32:16

- ワークステーション : ヒューレット・パッカード HP 9000 Series 200、アポロコンピュータの最初のシステム、サン・マイクロシステムズ Sun-1

- グラフィックス端末 : DEC VAXstation 100、シリコングラフィックス IRIS 1000 および 1200

UNIXシステムではプロセッサのメモリアドレッシングの上限やMMUの制限などにより、68000そのものは長く使われることはなかったが、その後継品種は1980年代を通して UNIX市場で広く使われた。そのアーキテクチャがDECのPDP-11やVAXによく似ていて、C言語のコードを動作させるのに最適なコンピュータだったからである。

1983年から68000はパーソナルコンピュータ (PC)、特にホビーパソコンで使われるようになった。まず、Apple ComputerのLisaとMacintoshで使われ、その後コモドール Amiga、アタリ Atari ST、シャープ X68000、それにソニー PalmTopなどで1990年代中盤まで使われた。一方68008が使われたホビーパソコンとしてはシンクレアQLぐらいしかない。(ちなみに日立製作所製のMB-S1には、オプションとして68008ボードが存在した)

68000はコントローラ用として最も成功した。1981年、Imagen社のImprint-10などのレーザープリンターは68000をCPUとする外部コントローラで制御されていた。最初のHP LaserJetは8MHzの68000を使ったコントローラを内蔵していた(1984年)。同様に68000を使ったコントローラが多くのレーザープリンターで使われている。例えばAppleのLaserWriterなどである。68000は1980年代を通してレーザープリンターで使用され、1990年代に入ってもローエンドのプリンターに使われ続けた。

また、68000は工業制御システムの分野でも成功を収めた。この種のシステムでは、68000やその派生CPUを中心としたプログラマブルロジックコントローラ (PLC) を利用する。このようなシステムは一般市場に比較して製品寿命が長く、20年前のものでもそのまま使い続けることが多い。そのため、21世紀になっても68000ベースのコントローラが数多く使われ続けている。

コンピュータゲームメーカーはアーケードゲームや家庭用ゲーム機などに68000を使った。アーケードゲームでは1983年にアタリが「Food Fight」で68000を使ったのが最初である。日本での初使用は同年のナムコ(後のバンダイナムコアミューズメント)の「 リブルラブル」である。1980年代後半から1990年代初めごろまでアーケードゲーム基板ではメインCPUとして68000がよく使われた。例えば、セガのセガ・システム16、カプコンのCPS-1とCPS-2、SNKのネオジオなどである。アーケードゲームでは68000を2個使ったり、場合によっては3個使う場合もあった[8]。1990年代、アーケードゲームのメインCPUはもっと高性能なプロセッサが使われるようになっていったが、68000はサウンドコントローラなどとして使われ続けた。

家庭用ゲーム機で68000がメインCPUとして使われた例としては、メガドライブ、メガCD[8]、家庭用のネオジオがある。その後のゲーム機でも、セガサターンは68EC000をサウンドコントローラとして使用し、Atari Jaguarでもグラフィックスやサウンドチップの制御に使われた。

また、クリエイティブテクノロジーのWave BLASTERやENSONIQ社のENSONIQ SoundScape DBをはじめとするPC向けサウンドカード用MIDIシンセサイザー・ドーターボードへ、制御用として68000が搭載されるケースが1990年代中盤には多数見られた。

技術の進歩によって68000がスタンドアローンのコンピュータ市場では使われなくなると、一般消費者向けの各種機器の組み込み用途に使われるようになった。テキサス・インスツルメンツは68000をハイエンドのグラフ表示電卓、TI-89、TI-92などで使っている。これらの初期のバージョンではスタティック版68EC000コアを使った特殊なマイクロコントローラだった。後のバージョンでは標準のMC68SEC000プロセッサが使われている。

CPU32とColdFireプロセッサは自動車のエンジン制御に数百万個単位で使われた。 また、低価格で信頼性が高いことから医療機器分野でも多く使用された。 低電圧版のDragonBallは、Palm PilotシリーズやHandspring VisorなどのPDAで使われた。後にこの市場はARMプロセッサコアに奪われた。高速シリアルポートを内蔵した派生品(68302と68360)は、シスコシステムズ、3Com、Ascend、Marconiなどが通信機器に使用した。

アーキテクチャ

[編集]| 開発者 | モトローラ |

|---|---|

| ビット数 | 32ビット |

| デザイン | CISC |

| エンコード | 可変多倍長 |

| エンディアン | Big |

| 拡張 | F系列命令 |

| オープン | プロプライエタリ |

| レジスタ | |

| 汎用 | D0-D7=32、D0-D8[要出典]=32 |

|

汎用(データ8本、 アドレス8本)、 ステータスレジスタ | |

概要

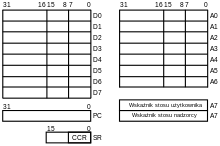

[編集]32ビットのデータレジスタを8本、また、32ビットのアドレスレジスタを8本持つ、CISCアーキテクチャのマイクロプロセッサである。8ビットのMC6800シリーズとはアセンブラソースレベルでもバイナリレベルでも互換性を持たない。

MC68000は、DECのVAXを参考にしたと言われる、直交性の高い命令体系をもつ。

外部バス幅はアドレスバス24ビット、データバス16ビットで、発表当初のクロック周波数は4 - 16MHz。約68,000個のトランジスタからなるN-MOS集積回路であり、当初は巨大な64ピンDIPパッケージ、後にPGAパッケージでも供給された。

データーバスはダイナミックバスサイジングを採用しており8ビットまたは16ビットのバスにアクセス可能である。これはM68000ファミリ周辺チップだけではなく、M6800ファミリなど廉価な8ビット周辺チップとの接続を考慮したものである。

MC68000自体は16ビットCPUとして取り扱われたが、内部アーキテクチャは32ビットプロセッサとして設計されており、レジスタとアドレスのデータ長は等しく32ビットとなっている。

32ビットのアドレス空間は4GBに相当するが、当時の技術では、4GB分のアドレス空間をフルに使う可能性は無いとされ、外部のアドレスバスとのデータ入出力では上位8ビットをマスクして下位24ビットを使用し、最大16MB分のメモリ領域を管理する実装とされていた。

このように最初に理想とする32ビットアーキテクチャを決めておき、その時々で利用できる技術で実現可能な機能から順に実装するという方式をとっていたため、無理なく上位互換性が確保できた。

また、ライバルであるx86系プロセッサではメモリ空間とは別にI/O空間が設けられ、専用のI/O命令が用意されていたが、MC68000シリーズではメモリ空間内にI/O用領域を割り当てるメモリマップドI/O方式を採用しているのも特徴の一つである。

ファンクションコード

[編集]| FC2 | FC1 | FC0 | 参照の分類 |

|---|---|---|---|

| 0 | 0 | 0 | 未定義 |

| 0 | 0 | 1 | ユーザ・データ |

| 0 | 1 | 0 | ユーザ・プログラム |

| 0 | 1 | 1 | 未定義 |

| 1 | 0 | 0 | 未定義 |

| 1 | 0 | 1 | スーパーバイザ・データ |

| 1 | 1 | 0 | スーパーバイザ・プログラム |

| 1 | 1 | 1 | 割り込み応答 |

MC68000ユーザズマニュアル[9]によると、MC68000シリーズのアドレス空間はFC0 - FC2ピンのデコードによって、スーパーバイザ・プログラムアドレス空間、ユーザ・プログラムアドレス空間、スーパーバイザ・データアドレス空間、ユーザ・データアドレス空間に分離された4つの32bitアドレス空間がある。しかし実際のところ、それぞれのアドレス空間を通信する機能が不十分であったため、ユーザはハードウェア実装においてはFCピンのデコードを行わずに1つの32ビットアドレス空間とするほかはなかった[10]。

MC68000シリーズではプログラムアドレス空間とデータアドレス空間を分離するハーバード・アーキテクチャを採用していた[要出典]。しかし、アドレス空間の分離におけるメモリ管理の複雑化、またハーバード・アーキテクチャを採用したオペレーティングシステム (OS) があまり供給されなかったことから、多くの実装ではプログラムアドレス空間とデータアドレス空間を分離しない設計が採用される場合が殆どだった。

スタック

[編集]スタックがOS用とアプリケーション用に二つあり[11]、特権モード(スーパバイザモード)と、ユーザモードの2つの特権レベルを持つなど、当初よりUNIXに代表される高度なメモリ管理機能やマルチタスク機能を備えたOSを搭載することを前提に設計されている。

ユーザーモードで動作するプログラムの互換性はMC68000からMC68060までバイナリレベルでほぼ完全に保たれているが、スーパバイザモードでの動作についてはこのモードで動作するOSが差異を吸収することを前提として、世代ごとに改良や変更が加えられている。

このため特にスタックポインタの実装とその挙動には世代間での相違が多く、アプリケーションがハードウェアリソースへ直接アクセスするためにスーパーバイザモードをアプリケーションに解放した原始的な実装のOSではMC68000用に書かれたこの種の動作を行うアプリケーションプログラムが後継各プロセッサで正常動作しないケースが存在する。

メモリアドレッシング

[編集]MC68000は16ビットのALUを持つ一方で、アドレスは常に32ビットで扱われ、フラットな32ビットアドレス空間を持つ。その実効アドレスの演算の為に、専用の16ビット幅のALUを2個持つ。

8086は20ビットのアドレス空間を持つが、リニアにアクセスできるのはセグメントと称された(セグメント方式#x86)16ビットの空間だけであった。これは特にグラフィックの扱いなどを面倒にした。[注 1]

MC68000では実効アドレス演算の為に専用の2つの16ビットのALUを接続して用い、3つめのALUが16ビットの演算を行った。

例えば、32ビットのアドレスレジスタのポストインクリメント(そのアドレスにアクセスした後、アドレスレジスタの内容をインクリメント(増加)するアドレッシングモード)「ADD.W (An)+,Dn」はポストインクリメントをしない場合に較べても速度低下することがない。

したがって、16ビットCPUとして始まってはいるが、68000の命令セットは32ビットアーキテクチャになっている。後継のMC68020は32ビットのALUと32ビットのデータバスを持っていたが、68000用のソフトウェアをほぼ変更することなしに、データバス幅を32ビットに拡張することで速度向上を果たした。

しかし、ソフトウェアの互換性を完全に保てたわけではない。68000では(同様のテクニックは同じく32ビットマシンだがアドレスが24ビットだったSystem/360で行われていたが)使われない(無視される)上位8ビットに何らかの情報を持たせる、というテクニックが一部のシステムプログラムなどで使われた。例えば、LISPなどでポインタの指すオブジェクトの種類を区別する情報をそこに格納したり、ガベージコレクション用のフラグを格納した。そのようなコードを、後継のより広いアドレスバスを持つマシンで実行するとバスエラーが発生した(やはりSystem/360の後継機でも同様の問題が起きており、System/370-XAではMSBを互換モードのために残した31ビット化という苦肉の策がとられている)[12]。

Macintoshでは8MB以上のRAMを搭載する際にソフトウェアのアップグレードが必要だった。

多くのアプリケーションは将来を見越して書かれており、問題は発生しなかった。

内部レジスタ

[編集]

8本の汎用データレジスタ (D0 - D7)と8本のアドレスレジスタ (A0 - A7) を持つ。 アドレスレジスタ (A7) はスタックポインタ (SP) であり、スタック上位のオブジェクトをアクセスする事が容易となった。

68000ファミリでの多バイトデータのメモリ上での配置はビッグ・エンディアンである。

ステータスレジスタ

[編集]68000の比較命令、算術演算命令、論理演算命令は実行結果をステータスレジスタに反映させ、後で条件ジャンプ命令でそれを使えるようになっている。 ステータスレジスタのビットには、"Z"ero(ゼロ)、"C"arry(キャリー)、o"V"erflow(オーバーフロー)、eXtend、そして"N"egative(ネガティブ)がある。 eXtendビットはCarryビットと分離されている。 eXtendとCarryは、シフト/算術演算/論理演算命令の桁上がり結果を保持するが、eXtendビットはより多バイトの演算を実現するために使い、Carryビットは処理の流れを制御するのに用いる。

命令セット

[編集]68000の設計者はアセンブリ言語が直交性を持つよう注意を払った。つまり、命令は操作とアドレッシングモードに分けられ、多くの場合は任意の操作に任意のアドレッシングモードを使えるようになっている。

ビットレベルで見ると、命令のオペコードの値は必ずしも現状の通りである必然性はない。このことは、ある意味でよい妥協点だった。真の直交性のあるマシンと同等の利便性を得ると同時にCPU設計者はオペコード表を自由に埋めることができた。

最小命令サイズは当時としては大きい16ビットである。さらに多くの命令やアドレッシングモードは追加のワードでアドレスやアドレスモードビット等を表現する。

多くの設計者はMC68000アーキテクチャはコストに見合うコンパクトなコードを実現していると信じている(特にコンパイラがコードを生成した場合)。多くの組み込み制御システムの設計者はメモリのコストに敏感であり、コードがコンパクトであるという信念がMC68000ならびに後継CPUを採用する動機に繋がり、アーキテクチャの寿命を延ばした。そして同様にコンパクトなARMアーキテクチャのThumb命令セットが登場するまで、多くの68000命令セット(のCPU)の採用をもたらし続けた。

特権レベル

[編集]このCPUと他の全ファミリは二段階の特権レベルを実装している。ユーザモードでは割り込みレベル制御以外はアクセス可能である。 スーパバイザ特権では全てにアクセスできる。割り込みが発生するとスーパバイザモードに移行する。 スーパバイザビットはステータスレジスタに格納され、ユーザプログラムからも見える。

割り込み

[編集]68000は8つの割り込みレベルを持つ。レベル0から7まで厳密に優先順位が決まっている。 番号が大きい割り込みが番号の小さい割り込みに対して割り込むことが出来る。ステータスレジスタには現在の割り込みレベルを特権命令でセットすることができ、これにより低いレベルの割り込みをブロックする。レベル7はマスクすることができないため、NMI(英: Non-Maskable Interrupt)とも言う[13]。レベル0は他の全てのレベルが割り込むことができる。レベル0は割り込み要求がないことを示す[14]。レベルはステータスレジスタに格納され、ユーザレベルプログラムからも見ることが出来る。

ハードウェア割り込みは3本の信号線によってCPUに伝えられ、この3本の値がペンディング中の最も高い割り込みレベルにエンコードされる。別途割り込みをエンコードするための割り込みコントローラが必要である。ただし、割り込み発生源が三つ以下のシステムでは、各割り込みを三本の信号線にそれぞれつなぐことで割り込みコントローラを省略できる。ただし、割り込みレベルと割り込みの対応が単純ではないためソフトウェアでの処理が複雑になる。割り込みコントローラは汎用ロジックIC74148のような単純なエンコーダでもよいし、VLSIの周辺チップでもよい。例えばMC68901は、割り込み制御だけでなくUART(シリアル)、タイマー、パラレルI/Oを備えている。

例外テーブル(割り込みベクターテーブル)はアドレス0番地から1023番地まで固定で置かれ、256個の32ビットアドレスを表す。最初のベクターは初期スタックアドレスであり、二番目のベクターは初期コードアドレスである。3番から15番のベクターは各種エラー処理ルーチンのアドレスである。エラーの種類としてはバスエラー、アドレスエラー、不正命令、ゼロによる割り算、CHK/CHK2命令ベクター、特権違反、そして予約されたベクター(後にline 1010エミュレータ、line 1111エミュレータ、ハードウェアブレークポイントに割り当てられた)がある。ベクター24から実際の割り込みに対応する。ハードウェアに対応しない擬似割り込み、レベル1から7のベクター、15個のTRAPベクター、いくつかの予約されたベクター、ユーザ定義ベクターの順番で並んでいる。

リセットされたとき、少なくともスタートコードアドレスのベクターには正しいアドレスが入っている必要がある。多くのシステムは不揮発メモリ(つまりROM)を持っていて、0番地に配置し、そのROMにベクターテーブルとブートストラップコードが入っている。しかし、汎用システムでは動作中にベクターを書き換えられるのが望ましい。これを実現するため、ROM上のベクターがRAM上のジャンプテーブルを指すようにするか、バンク切り替えで動作中に0番地付近の配置をROMからRAM変更する。

68000はPopekとGoldbergの仮想化要件(英: virtualization requirements for full processor virtualization)を満たしていない。というのは、"MOVE from SR" 命令が特権命令でないため、ユーザモードから特権ステータスが見えてしまうからである。この問題は後述する仮想記憶サポートの問題とともに後のMC68010で改善された。"MOVE from SR" 命令は特権命令となり、ユーザモードのソフトウェア用に "MOVE from CCR" 命令を追加した。ユーザモードで "MOVE from SR" 命令を使った場合、トラップが発生してOS側でエミュレートすることも可能である。

MC68000 でのデマンドページングの実現

[編集]680x0系の最初のプロセッサであるMC68000の仕様は、外部支援なしにはデマンドページングの実現が困難なものであった。

デマンドページングでは、実行中の命令のメモリアクセスがページフォールトを起こしたら、(それが正常なアクセスであれば)その実行中の命令の実行を一旦フリーズし、外部記憶と主記憶の間でスワッピングをおこなってから、実行中だった命令の実行から再開する、という処理が必要である。

しかし、MC68000がページフォールトの際に保存する内部情報は、「実行中だった命令の実行からの再開」ができないものであった。このため、MC68000の通常の割り込みの処理に従ってしまうと、デマンドページングは実現できない。これを、単にそもそもサポートするつもりが無かったものとみるむきもあれば、「仕様のバグ」とみるむきもあれば、後述のようにして実現が可能であるし、MMUも計画中に過ぎなかったのだから「将来仮想記憶をシリコン上に実装することを正当化する需要が発生するまでの暫定的な実装仕様」だったと考えるほうが自然である、とみるむきもある。

そのようなMC68000で仮想記憶を実装するためには、MC68000には次のような機能があった。バスアクセス中にあるピンをアサートすることにより、命令の実行をそこで一旦フリーズし、スリーステートバスをハイインピーダンスにして解放させたままいつまででも止めておいて、そののち、元の命令の中断したバスアクセスから再実行(re-run)する機能である。これによるバスサイクルをリランサイクル(rerun cycle)という。

これを利用して、メインのCPUであるMC68000を止めた状態で、別のプロセッサでページ処理をおこなうようにして、デマンドページングを実装できる。必然性はないが、同じバスに接続する容易性から、この補助プロセッサにもMC68000が使われることが多い。

以上のようなMC68000のデュアル・プロセッサによる仮想記憶を実現したコンピュータとしてはアポロコンピュータのDomainが有名である。同社の実装ではページスワップを担うスレーブ・プロセッサは、通常時はグラフィックス・プロセッサとして動作し、必要に応じてマスターのページ・スワップ要求に応じた。

この問題は後のMC68010で解決された。MC68010では、バスエラーとアドレスエラーが発生した場合、エラーを発生させた元の命令を指すプログラムカウンタのアドレスをスーパバイザスタックに保存することにより、元の処理に復帰できるようになった。

命令セットの詳細

[編集]基本的なアドレッシングモードは以下の通りである。

- レジスタ直接

- データレジスタ、例 "D0"

- アドレスレジスタ、例 "A6"

- レジスタ間接

- 単純アドレス、例 (A0)

- ポストインクリメント付アドレス、例 (A0)+

- プレデクリメント付アドレス -(A0)

- 16ビット符号付オフセット、例 16(A0)

- 実際のインクリメントやデクリメントのサイズはオペランドの指定によって変わる。バイトリード命令ではインクリメントすると、アドレスに1を加算し、ワード(16ビット)では2を、ロング(32ビット)では4を加算する。

- インデックス付レジスタ間接

- 8ビット符号付オフセット、例 8(A0, D0) または 8(A0, A1)

- プログラムカウンタ相対

- 16ビット符号付オフセット、例 16(PC). このモードは非常に便利

- インデックス付8ビット符号付オフセット、例 8(PC, D2)

- 絶対アドレス指定

- "$4000"のような数値や、アセンブラが翻訳するシンボリックな名前。

- 68000のアセンブリ言語では16進数を表すのに "0x" ではなく "$" を使うものが多い。

- イミディエート値

- 命令内に埋め込み、例 "#400".

追加:ステータスレジスタへのアクセス。後のモデルでは他の特殊レジスタも同様。

多くの命令にはドットに続くサフィックスが付き、処理単位を8ビット (".b")、 16ビット (".w")、32ビット (".l") で指定する。

多くの命令は入力(ソース)と出力(デスティネーション)を持ち、デスティネーションに変更を加える。主な命令は以下の通りである。

- 算術演算:

ADD,SUB,MULU(符号なし掛け算),MULS(符号あり掛け算),DIVU,DIVS,NEG(否定加算),CMP(減算の一種だが、ステータスビットにのみ結果を反映し、実際の減算結果は格納しない) - 二進化十進演算:

ABCD,SBCD - 論理演算:

EOR(排他的論理和),AND,NOT(論理否定) - シフト演算:

- 論理シフト、つまり右シフトで最上位ビットをゼロにする:

LSL,LSR - 算術シフト、つまり最上位ビットを符号拡張する:

ASR,ASL - ローテート、eXtendを使う命令と使わない命令:

ROXL,ROXR,ROL,ROR

- 論理シフト、つまり右シフトで最上位ビットをゼロにする:

- メモリ内のビット操作:BSET(1にする), BCLR(0にする), and BTST(SRのZeroビットをセット)

- マルチプロセッサ制御:

TAS(テストアンドセット、1命令でビットテストのためのリードとその結果のライトの2つのメモリアクセスを割り込みなどで中断されない不可分なバスサイクルで行うことによりメモリ共有型マルチプロセッサでのセマフォを実現) - フロー制御:

JMP(ジャンプ),JSR(サブルーチンコール),BSR(相対アドレスでのサブルーチンコール),RTS(サブルーチンからの復帰),RTE(例外や割り込みからの復帰),TRAP(ソフトウェア割り込みに似たソフトウェア例外を発生),CHK(条件付きソフトウェア割り込み) - 分岐:

Bcc("cc"は分岐条件として16種類のステータスレジスタのチェック方法を記述:equal(等しい), greater than(大きい), less-than(小さい), carry, これらの組み合わせや論理否定) - デクリメント付き分岐:

DBcc("cc"は分岐命令と同じ意味)指定したデータレジスタをデクリメントした後、指定された条件が真で、デクリメント結果が-1でないなら分岐する。0ではなく-1でチェックするのは、ループを記述する場合にコードを単純化するためである。ループカウンタとして最初から0が指定された場合、デクリメントされて-1になるので分岐しない。したがって0かどうかをループに入る前にチェックする必要がない。

M68000ファミリ

[編集]メインプロセッサ

[編集]

- MC68000 - サン・マイクロシステムズの初代UNIXワークステーションであるSun-1や、初期のMacintoshなどに採用された。日本ではシャープ X68000シリーズ、SEGA メガドライブ、SNK ネオジオなどに採用された。

- MC68EC000 - 8ビットデータバスとして使用できるローコスト版。各種機器制御用の組み込みMPUとして使用されたほか、セガサターンではサウンド制御用MPUとして搭載された。

- MC68008 - データバスを8ビット、アドレスバスを20ビットに縮小、安価な48ピンパッケージに収めた縮小版の68000MPUである。

- MC68010 - MC68000に仮想記憶および仮想機械を実現するための機構を追加した。3ワード分のキャッシュを持ち、MC68000に較べ、DBcc命令等を高速に実行可能だった。サン・マイクロシステムズのUNIXワークステーションであるSun-2や日立 2050(初代)に搭載された。

- MC68012 - 外部アドレスバス31ビット。

- MC68020 - 外部アドレスバス32ビット、データバス32ビットと、名実ともに32ビット化。命令キャッシュ256バイトを追加。コプロセッサの接続も可能になった。 Sun-3、Macintosh II、Amiga 1200、日立 2050/32などに搭載。

- MC68030 - MC68851相当のMMU内蔵、命令キャッシュのほかにデータキャッシュ256バイトを追加。Sun3/80、ソニー NEWS、Next Cube(初代)、Macintosh IIx以降、Amiga 3000、日立 2050/32Eなどに搭載。

- MC68040 - MMU、MC68882相当のFPU内蔵(一部命令はソフトウェアエミュレート)、各キャッシュを4Kバイトに増加、命令の高速化、マルチプロセッサのサポート。NeXTcube、Macintosh Quadra・Centris、Amiga 4000などに搭載。なお、68040はXC68040(ソフトで言うベータ版)チップがそのまま量産されており、いわゆるエラッタが解消したMC68040はほとんど流通していない。

- MC68LC040 - FPU無し。Macintosh LC475・575等、Appleの廉価モデルなどに搭載。

- MC68EC040 - FPU無し。MMU無し。

- MC68040V - 低電圧動作 (3.3V) 版。

- MC68060 - 68040とピン互換、内部2逓倍、ワイヤードロジック化に伴い、一部の命令が削除された。しかしサン・マイクロシステムズはSPARC、MacintoshはPowerPC、他はMIPSなどに移行したためワークステーション・PCではほとんど採用されず。AmigaやX680x0ではアクセラレータとして使われた。

- MC68EC060

- MC68LC060

- SCC68070 - シグネティックスが、CD-iのために製造した組み込み用の互換MPU。

- MC68MH360FE - MC68360(CPU32+ベース)+SCC (Serial Communications controllers)

周辺LSI

[編集]

- MC68120 - IPC (Intelligent Peripheral Controller with mask ROM)

- MC68121 - IPC (Intelligent Peripheral Controller w/o mask ROM)

- MC68122 - CTC(クラスタ ターミナル コントローラ)[3]

- MC68150 - DBS (Dynamic Bus Sizer)

- MC68153 - Bus Interrupter

- MC68160 - EEST (Ethernet Driver)

- MC68184 - BIC (Broadband Interface Controller)

- MC68185 - Twisted Pair Modem

- MC68194 - Carrier band Modem for IEEE 802.4

- MC68195 - Local Talk Adapter

- MC68230 - PI/T (Parallel Interface & Timer) パラレルインターフェイス&タイマ

- MC68338 - MAC (Media Access Controller)

- MC68339 - FSI (FDDI System Interface)

- MC68341 - 浮動小数点ROM[3]

- MC68356 - SPCE (Signal Processing Communication Engine)

- MC68360 - QUICC ( Quad Integrated Communication Controller)

- SCC68430 - DMAC (1ch Direct Memory Access Controller)

- MC68440 - DMAC (2ch Direct Memory Access Controller)

- HD68450 - DMAC (4ch Direct Memory Access Controller)

- MC68451 - MMU (Memory Management Unit)[3]

- MC68452 - Bus Arbiter

- MC68453 - Bubble Memory Controller バブルメモリコントローラ[3]

- HD63463 - HDC (Hard Disk Controller) ハードディスクコントローラ

- HD63484 - ACRTC (Advanced Cathode Ray Tube Controller)

- MC68488 - GPIBA (GP-IB Adapter)

- R68C552 - DACIA (Dual Asynchronous Communication Interface Adapter)

- R68560 - MPCC ( Multi Protocol Communication Controller)

- HD68562 - DUSCC (Dual Universal Serial Communication Controller)

- MK68564 - UART

- MC68605 - X.25 Protocol Controller

- MC68606 - X.25 Multi-Link LAPD Protocol

- SCN68652 - MPCC (Multi-protocol Communication Controller)

- MC68661 - UART

- MC68681 - DUART (Dual Universal Asynchronous Receiver/Transmitter)

- SCC68692 - 68681 Compatible CMOS

- R68802 - LNET (Local Network Controller)

- MC68824 - TBC (Token Bus Controller)

- MC68834 - Stream Cipher Chip

- MC68836 - FCG (FDDI Clock Generator)

- MC68837 - ELM (Elasticity Buffer and Link management)

- MC68838 - MAC (Media Access Controller)

- MC68839 - FSI (FDDI System Interface)

- MC68840 - Integrated FDDI

- MC68847 - quad ELM

- MC68848 - CAMEL

- MC68851 - PMMU (32bit Page Memeoy Management Unit)

- MC68881 - FPU (Floating-Point Unit) 浮動小数点演算ユニット

- MC68882 - FPU (Floating-Point Unit) 浮動小数点演算ユニット(改良版)

- MC68901 - MFP (Multi Function Peripheral) 多機能周辺コントローラ

後継製品

[編集]- CPU16

- TMP68301 - 68HC000 + UART etc(東芝製)

- TMP68303 - 68HC000 + UART + PI/T(東芝製)

- MC68302 - 68EC000 + SCC(高機能通信コントローラ)、DMA、Timer他。ISDN等の通信機器に使われた。

- MC68306 - 68EC000 + DUART

- MC68307 - 68EC000 + UART

- MC68322 (BANDIT) - 68EC000 +

- MC68328 (DragonBall) - 68EC000 + LCDコントローラ、UART、SPI、PWM、Timer、RTC他。Palm (PDA) に使われた。

- CPU32 MCU

- MC68330 - CPU32

- MC68331 - CPU32 + GPT (Timer),QSM(キュー付シリアルモジュール)

- MC68332 - CPU32 + TPU(高機能なタイマ/カウンタ),QSM,SIM(システム統合モジュール)

- MC68334 - モジュラプロセッサ - CPU32 + TPU,SIM, 8/10ビットADコンバータ(変換速度は8ビット時8ms、10ビット時9ms[15]), 132ピンPQFPパッケージ, 最高動作周波数16.78MHz(システムクロックを停止することも可能)[15]。

- MC68340 - CPU32 + DMA,DUART,Timer

- MC68341 - CPU32 + タイマ,2チャネルDMA,2チャネルSIO(シリアルIO),SIM41(システム統合モジュール)、CD-Iエンジン向けプロセッサ、データバス16ビット、アドレスバス32ビット

- MC68356 - MC68302のスーパーセット(統合マルチプロトコル・プロセッサ) - 68EC000 + RISCプロセッサ(CP:通信プロセッサとして利用) + DSP56002, SIB(システム統合ブロック), PCMCIAサポート, 16550UARTエミュレーション

- MC68360 (QUICC) - CPU32+(CPU32上位互換) + CPM(高機能通信コントローラ),DMA,Timer

- ColdFire - M68Kシリーズから派生したRISCプロセッサ。命令セットは68000から一部削除されソースコードレベルでサブセットとなっている。

- MCF52xx - ColdFire V2

- MCF53xx - ColdFire V3

- MCF54xx - ColdFire V4/V4e

エミュレータ

[編集]- BUFFEE Accelerator - MC68000と差替えて使えるよう、AM335x ARM Cortex-A8を搭載しMC68040 400MHz相当のアクセラレータとして、2021年3月現在、開発途上[16]

参考文献

[編集]- Motlora, Inc.『M68000マイクロプロセッサユーザーズ・マニュアル』(4th edition第9版)CQ出版、1990年5月10日。ISBN 978-4-7898-4091-0。M68000UMJ/AD4。

- 日立マイクロコンピュータエンジニアリング 著、関根慶太郎 編『図解16ビットマイコン68000とファミリの活用DMAC・ACRTC・HDC』東京電機大学出版局、1987年。ISBN 978-4-501-51240-8。 NCID BN02581340。

- 阿刀田央一『68000ハードウェア設計』五十嵐智・鵜沢繁行(初版第2刷(第1回修正))、昭晃堂、1987年。ISBN 978-4-7856-3062-1。 NCID BN01471063。

- 日本モトローラ株式会社半導体事業部『MC68030ユーザーズ・マニュアル』CQ出版1990年、日本モトローラ。米: MC 68030 enhanced 32-bit microprocessor user's manual。NCID BN06695647。

- MOTOROLA (1994年). “M68000 8-/16-/32-Bit Microprocessors User's Manual, Ninth Edition” (PDF). MOTOROLA. 2015年1月20日閲覧。

- 禿節史、喜田祐三、田邊皓正、藤岡旭『16ビットマイクロプロセッサ』丸善株式会社、1981年6月30日。

- 『インターフェース』1995年1月号、CQ出版社、1995年1月。

- 「ASCII 1983年5月号」第7巻第5号、株式会社アスキー出版、1983年5月1日。

脚注

[編集]- ^ ASCII 1983年5月号, p. 88.

- ^ “DCL、東京・多摩に新工場建設――ワークステーション増産、カスタムLSIも。”. 2023年10月18日閲覧。

- ^ a b c d e 禿節史、喜田祐三、田邊皓正、藤岡旭『16ビットマイクロプロセッサ』丸善株式会社、1981年6月30日、158-161頁。

- ^ "68HC001 obsoletes 68008."[リンク切れ], Microprocessor Report, 1990年6月20日; available from HighBeam Research (subscription).

- ^ "Motorola streamlines 68000 family; "EC" versions of 68000, '020, '030, and '040, plus low-end 68300 chip."[リンク切れ], Microprocessor Report, 1991年4月17日; available from HighBeam Research (subscription).

- ^ "Motorola reveals MC68SEC000 processor for low power embedded applications", Motorola press release, 1996年11月18日; archived by Internet Archive on 1997年3月28日.

- ^ comp.sys.m68k Usenet posting, 1995年5月16日; 同スレッド内の他のポストも参照されたい。

- ^ a b 【連載】セガハードストーリー 第3回“時代が求めた16ビット” 『メガドライブ』セガハード大百科 2017年10月27日

- ^ a b Motlora, Inc.『M68000マイクロプロセッサユーザーズ・マニュアル』(4th edition第9版)CQ出版、1990年5月10日。ISBN 978-4-7898-4091-0。M68000UMJ/AD4。

- ^ 阿刀田央一 1987.

- ^ MOTOROLA 1994, p. 2-2.

- ^ このような、アドレスの空きビットの「活用」を防ぐような実装も、x64(初期リリースでは64ビットのアドレス空間のうち48ビットだけを利用、残りのビットは47ビット目のコピーでないとエラー)などで行われている。

- ^ 16-bit_microprocessors 1983, p. 202.

- ^ 16-bit_microprocessors 1983, p. 163.

- ^ a b インターフェース 1995年1月号, p. 233.

- ^ 株式会社インプレス (2021年2月8日). “68000と挿し替えて使えるCPUアクセラレータ「Buffy Acellerator」”. PC Watch. 2021年3月25日閲覧。