## Specification for the FIRRTL Language Version 3.2.0

# The FIRRTL Specification Contributors

September 27, 2023

## Contents

| 1 | Revis                      | sion History                                | <b>5</b>           |

|---|----------------------------|---------------------------------------------|--------------------|

| 2 | <b>Intro</b><br>2.1<br>2.2 | duction<br>Background                       | <b>8</b><br>8<br>9 |

| 3 | Ackn                       | owledgments                                 | 9                  |

| 4 | File l                     | Preamble                                    | 10                 |

| 5 | Circu                      | uits and Modules                            | 10                 |

|   | 5.1                        | Circuits                                    | 10                 |

|   | 5.2                        | Modules                                     | 11                 |

|   | 5.3                        | Optional Groups                             | 11                 |

|   | 5.4                        | Externally Defined Modules                  | 13                 |

|   | 5.5                        | Implementation Defined Modules (Intrinsics) | 15                 |

| 6 | Liter                      | als                                         | 15                 |

|   | 6.1                        | Radix-specified Integer Literal             | 15                 |

| 7 | Туре                       | S                                           | 16                 |

|   | 7.1                        | Ground Types                                | 16                 |

|   |                            | 7.1.1 Integer Types                         | 16                 |

|   |                            | 7.1.2 Clock Type                            | 17                 |

|   |                            | 7.1.3 Reset Type                            | 17                 |

|   |                            | 7.1.4 Analog Type                           | 18                 |

|   | 7.2                        | Aggregate Types                             | 19                 |

|   |                            | 7.2.1 Vector Types                          | 19                 |

|   |                            | 7.2.2 Bundle Types                          | 19                 |

|   |                            | 7.2.3 Enumeration Types                     | 20                 |

|   | 7.3   | Reference Types                                                                                       |

|---|-------|-------------------------------------------------------------------------------------------------------|

|   |       | 7.3.1 Probe Types                                                                                     |

|   |       | 7.3.2 Input Probe References                                                                          |

|   | 7.4   | Type Alias                                                                                            |

|   | 7.5   | Property Types                                                                                        |

|   |       | 7.5.1 Integer Property Types                                                                          |

|   | 7.6   | Type Modifiers                                                                                        |

|   |       | 7.6.1 Constant Type                                                                                   |

|   | 7.7   | Passive Types                                                                                         |

|   | 7.8   | Type Equivalence   28                                                                                 |

| 8 | State | ements 28                                                                                             |

|   | 8.1   | Connects                                                                                              |

|   |       | 8.1.1 The Connection Algorithm                                                                        |

|   |       | 8.1.2 Last Connect Semantics                                                                          |

|   | 8.2   | Empty         30                                                                                      |

|   | 8.3   | Wires         31                                                                                      |

|   | 8.4   | Registers                                                                                             |

|   | 0.1   | 8.4.1 Registers without Reset                                                                         |

|   |       | 8.4.2 Registers with Reset                                                                            |

|   | 8.5   | Invalidates                                                                                           |

|   | 0.0   | 8.5.1 The Invalidate Algorithm                                                                        |

|   | 8.6   | Attaches       33                                                                                     |

|   | 8.7   | Nodes         33                                                                                      |

|   | 8.8   | Conditionals     33                                                                                   |

|   | 0.0   | 8.8.1 When Statements                                                                                 |

|   |       | 8.8.1       When Statements       34         8.8.2       Match Statements       36                    |

|   |       |                                                                                                       |

|   |       |                                                                                                       |

|   |       | 8.8.4 Initialization Coverage                                                                         |

|   |       | 8.8.5 Scoping                                                                                         |

|   | 0.0   | 8.8.6 Conditional Last Connect Semantics                                                              |

|   | 8.9   | Memories                                                                                              |

|   |       | 8.9.1 Read Ports                                                                                      |

|   |       | 8.9.2 Write Ports                                                                                     |

|   |       | 8.9.3 Readwrite Ports                                                                                 |

|   |       | 8.9.4 Read Under Write Behavior                                                                       |

|   |       | 8.9.5 Write Under Write Behavior                                                                      |

|   |       | 8.9.6 Constant memory type $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 42$ |

|   | 8.10  | Instances                                                                                             |

|   | 8.11  | Stops                                                                                                 |

|   | 8.12  | Formatted Prints                                                                                      |

|   |       | 8.12.1 Format Strings                                                                                 |

|   | 8.13  | Verification                                                                                          |

|   |       | 8.13.1 Assert                                                                                         |

|   |       | 8.13.2 Assume                                                                                         |

|    |       | 8.13.3 Cover                               | 45        |

|----|-------|--------------------------------------------|-----------|

|    | 8.14  | Probes                                     | 46        |

|    |       | 8.14.1 Define                              | 46        |

|    |       | 8.14.2 Force and Release                   | 48        |

|    | 8.15  | Property Assignments                       | 51        |

| _  | -     |                                            | ~~~       |

| 9  | _     | essions                                    | 52        |

|    | 9.1   | Constant Integer Expressions               | 52        |

|    | 9.2   | Property Literal Expressions               | 53        |

|    |       | 9.2.1 Integer Property Literal Expressions | 53        |

|    | 9.3   | Enum Expressions                           | 53        |

|    | 9.4   | References                                 | 53        |

|    |       | 9.4.1 Static Reference Expressions         | 54        |

|    | 9.5   | Sub-fields                                 | 54        |

|    | 9.6   | Sub-indices                                | 54        |

|    | 9.7   | Sub-accesses                               | 55        |

|    | 9.8   | Multiplexers                               | 57        |

|    | 9.9   | Primitive Operations                       | 58        |

|    | 9.10  | Reading Probe References                   | 58        |

|    | 9.11  | Probe                                      | 59        |

| 10 | ъ.    |                                            | 50        |

| 10 |       | itive Operations                           | <b>59</b> |

|    | 10.1  | Add Operation                              | 59<br>60  |

|    | 10.2  | Subtract Operation                         | 60<br>60  |

|    | 10.3  | Multiply Operation                         | 60<br>60  |

|    | 10.4  | Divide Operation                           | 60        |

|    | 10.5  | Modulus Operation                          | 60        |

|    | 10.6  | Comparison Operations                      | 61        |

|    | 10.7  | Padding Operations                         | 61        |

|    | 10.8  | Interpret As UInt                          | 61        |

|    | 10.9  | Interpret As SInt                          | 61        |

|    |       | Interpret as Clock                         | 62        |

|    | 10.11 | Interpret as AsyncReset                    | 62        |

|    | 10.12 | Shift Left Operation                       | 62        |

|    | 10.13 | 0 1                                        | 62        |

|    |       | Dynamic Shift Left Operation               | 63        |

|    | 10.15 | Dynamic Shift Right Operation              | 63        |

|    | 10.16 | Arithmetic Convert to Signed Operation     | 63        |

|    | 10.17 | Negate Operation                           | 63        |

|    | 10.18 | Bitwise Complement Operation               | 64        |

|    | 10.19 | Binary Bitwise Operations                  | 64        |

|    | 10.20 | Bitwise Reduction Operations               | 64        |

|    | 10.21 | Concatenate Operation                      | 64        |

|    | 10.22 | Bit Extraction Operation                   | 65        |

|    | 10.23 | Head                                       | 65        |

|    | 10.24 Tail                                                                                                                                                                 | 65                          |  |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--|

| 11 | Flows                                                                                                                                                                      | 65                          |  |

| 12 | Width Inference                                                                                                                                                            |                             |  |

| 13 | Combinational Loops                                                                                                                                                        |                             |  |

| 14 | Namespaces                                                                                                                                                                 |                             |  |

| 15 | Annotations15.1Targets15.2Annotation Storage                                                                                                                               | <b>67</b><br>68<br>70       |  |

| 16 | Semantics of Values         16.1       Indeterminate Values                                                                                                                | <b>71</b><br>71             |  |

| 17 | Details about Syntax                                                                                                                                                       | 72                          |  |

| 18 | FIRRTL Compiler Implementation Details         18.1       Module Conventions         18.1.1       The "Scalarized" Convention         18.2       The "Internal" Convention | <b>74</b><br>74<br>74<br>76 |  |

| 19 | FIRRTL Language Definition                                                                                                                                                 | 77                          |  |

| 20 | Versioning Scheme of this Document                                                                                                                                         | 81                          |  |

## 1 Revision History

- 3.2.0

- Add optional groups.

- Fix position of "Type Alias" (it used to be in the middle of "Reference Types").

- 3.1.0

- Add Integer property literals.

- Add property assignment.

- Add Integer property type.

- Add initial description of property types.

- Change/clarify mux selector width inference to align with other operations (must infer to some width by itself, pad if infers to less than 1-bit).

- Fix printf grammar, expect commas between arguments.

- Fix spec bug where string-encoded literals were still used in examples of "Constant Integer Expression".

- Fix bug in grammar where int was incorrectly specified as being binary instead of decimal.

- 3.0.0

- Add intrinsic modules to syntax highlighting

- Add connect, invalidate to syntax highlighting

- Add alternative regreset syntax

- Add literal identifiers to allow for legal numeric fields

- Simplify last-connect semantics explanation, remove "statement groups" (which are not part of the spec) which are only used in the original explanation

- Add enumeration types, match statements, and enumeration expressions

- Fixup probe endpoint and non-passive force examples.

- Add type alias

- Restrict string-encoded integers to only being usable in the construction of hardware literals.

- Change string-encoded integers to radix-encoded integers.

- Remove legacy connect (<=) and invalidate (is invalid) syntax

- Make connect disallow implicit truncation (again).

- 2.4.0

- Add radix-encoded integer literals as alternative syntax for string-encoded integer literals.

- Add missing deprecation notice for "reg with" syntax.

- 2.3.0

- Add intrinsic modules to syntax highlighting

- Add connect, invalidate to syntax highlighting

- Add alternative regreset syntax

- 2.2.0

- Add 'asAsyncReset' to primop\_1expr\_keyword in "FIRRTL Language Definition"

- Fix grammar for force\_release statements

- Add a description of conventions for modules

- 2.1.1

- Fix typos in force/release examples, force takes expr not int literal.

- Delineate string and single-quoted/double-quoted string in grammar.

- Deprecate reference-first statements.

- Tweak grammar of 'read' to support 'read(probe(x))' as in examples.

- 2.0.1

- Clarify int/string types and their allowed usage.

- 2.0.0

- Remove Fixed Point Types.

- Remove conditionally valid expression (validif)

- Remove partial connect ("<-")

- Remove FIRRTL forms and lowering, indicate that high-level constructs may be preserved by a FIRRTL compiler

- Add Compiler Implementation Details documenting Lower Types pass

- Define constant type modifier.

- Remove stray language leftover from removing conditionally valid.

- Render inline annotations as JSON, fix typo in example.

- Fix rendering of type modifiers (const) in document.

- Fix grammar for registers.

- Add reference types and related statements.

- 1.2.0

- Specify behavior of zero bit width integers, add zero-width literals

- Specify behavior of indeterminate values

- Add an explicit section about "Aggregate Types" and move "Vector Type" and "Bundle Type" under it.

- Move "head" and "tail" from primop\_lexpr\_keyword to primop\_lexprlint\_keyword in the "FIRRTL Language Definition".

- Add in-line annotation format

- Specify behavior of combinational loops

- Change connect to truncate widths to align with all existing FIRRTL Compiler implementations

- Fix spelling/grammar issues

- Allow out-of-bounds errors to be caught at compile time.

- Clarify the string argument for cover is a comment, not a message as it is for assert and assume.

- Add intrinsics.

- Fix parameter grammar to include name of parameter.

- 1.1.0

- Add version information to FIRRTL files

- Specify "As-If" limited to boolean

- 1.0.0

- Document the versioning scheme of this specification.

- 0.4.0

- Add documentation for undocumented features of the Scala-based FIRRTL Compiler (SFC) that are de facto a part of the FIRRTL specification due to their widespread use in Chisel and the SFC: Annotations, Targets, Asynchronous Reset, Abstract Reset

- Minor typo corrections and prose clarifications.

- 0.3.1

- Clarify analog usage in registers

- Rework authorship as "The FIRRTL Specification Contributors"

- Add version information as subtitle

- Formatting fixes

- 0.3.0

- Document moved to Markdown

## 2 Introduction

## 2.1 Background

The ideas for FIRRTL (Flexible Intermediate Representation for RTL) originated from work on Chisel, a hardware description language (HDL) embedded in Scala used for writing highlyparameterized circuit design generators. Chisel designers manipulate circuit components using Scala functions, encode their interfaces in Scala types, and use Scala's object-orientation features to write their own circuit libraries. This form of meta-programming enables expressive, reliable and type-safe generators that improve RTL design productivity and robustness.

The computer architecture research group at U.C. Berkeley relies critically on Chisel to allow small teams of graduate students to design sophisticated RTL circuits. Over a three year period with under twelve graduate students, the architecture group has taped-out over ten different designs.

Internally, the investment in developing and learning Chisel was rewarded with huge gains in productivity. However, Chisel's external rate of adoption was slow for the following reasons.

- 1. Writing custom circuit transformers requires intimate knowledge about the internals of the Chisel compiler.

- 2. Chisel semantics are under-specified and thus impossible to target from other languages.

- 3. Error checking is unprincipled due to under-specified semantics resulting in incomprehensible error messages.

- 4. Learning a functional programming language (Scala) is difficult for RTL designers with limited programming language experience.

- 5. Confounding the previous point, conceptually separating the embedded Chisel HDL from the host language is difficult for new users.

- 6. The output of Chisel (Verilog) is unreadable and slow to simulate.

As a consequence, Chisel needed to be redesigned from the ground up to standardize its semantics, modularize its compilation process, and cleanly separate its front-end, intermediate representation, and backends. A well defined intermediate representation (IR) allows the system to be targeted by other HDLs embedded in other host programming languages, making it possible for RTL designers to work within a language they are already comfortable with. A clearly defined IR with a concrete syntax also allows for inspection of the output of circuit generators and transformers thus making clear the distinction between the host language

and the constructed circuit. Clearly defined semantics allows users without knowledge of the compiler implementation to write circuit transformers; examples include optimization of circuits for simulation speed, and automatic insertion of signal activity counters. An additional benefit of a well defined IR is the structural invariants that can be enforced before and after each compilation stage, resulting in a more robust compiler and structured mechanism for error checking.

## 2.2 Design Philosophy

FIRRTL represents the standardized elaborated circuit that the Chisel HDL produces. FIRRTL represents the circuit immediately after Chisel's elaboration. It is designed to resemble the Chisel HDL after all meta-programming has executed. Thus, a user program that makes little use of meta-programming facilities should look almost identical to the generated FIRRTL.

For this reason, FIRRTL has first-class support for high-level constructs such as vector types, bundle types, conditional statements, and modules. A FIRRTL compiler may choose to convert high-level constructs into low-level constructs before generating Verilog.

Because the host language is now used solely for its meta-programming facilities, the frontend can be very light-weight, and additional HDLs written in other languages can target FIRRTL and reuse the majority of the compiler toolchain.

## 3 Acknowledgments

The FIRRTL specification was originally published as a UC Berkeley Tech Report (UCB/EECS-2016-9) authored by Adam Izraelevitz (@azidar), Patrick Li (@CuppoJava), and Jonathan Bachrach (@jackbackrack). The vision for FIRRTL was then expanded in an ICCAD paper and in Adam's thesis.

During that time and since, there have been a number of contributions and improvements to the specification. To better reflect the work of contributors after the original tech report, the FIRRTL specification was changed to be authored by *The FIRRTL Specification Contributors*. A list of these contributors is below:

- @albert-magyar

- @azidar

- @ben-marshall

- @boqwxp

- @chick

- @dansvo

- @darthscsi

- @debs-sifive

- @donggyukim

- @dtzSiFive

- @eigenform

- @ekiwi

- @ekiwi-sifive

- @felixonmars

- @grebe

- @jackkoenig

- @jared-barocsi

- @keszocze

- @mwachs5

- Oprithayan

- @richardxia

- @rwy7

- @seldridge

- @sequencer

- @shunshou

- @tdb-alcorn

- @tymcauley

- Quenoku

- @youngar

## 4 File Preamble

A FIRRTL file begins with a magic string and version identifier indicating the version of this standard the file conforms to (see Section 20). This will not be present on files generated according to versions of this standard prior to the first versioned release of this standard to include this preamble.

```

FIRRTL version 1.1.0 circuit MyTop...

```

## 5 Circuits and Modules

## 5.1 Circuits

All FIRRTL circuits consist of a list of modules, each representing a hardware block that can be instantiated. The circuit must specify the name of the top-level module.

```

circuit MyTop :

module MyTop :

; ...

module MyModule :

; ...

```

## 5.2 Modules

Each module has a given name, a list of ports, and a list of statements representing the circuit connections within the module. A module port is specified by its direction, which may be input or output, a name, and the data type of the port.

The following example declares a module with one input port, one output port, and one statement connecting the input port to the output port. See Section 8.1 for details on the connect statement.

```

module MyModule :

input foo: UInt

output bar: UInt

connect bar, foo

```

Note that a module definition does *not* indicate that the module will be physically present in the final circuit. Refer to the description of the instance statement for details on how to instantiate a module (Section 8.10).

## 5.3 Optional Groups

Optional groups are named collections of statements inside a module. Optional groups contain functionality which will not be present in all executions of a circuit. Optional groups are intended to be used to keep verification, debugging, or other collateral, not relevant to the operation of the circuit, in a separate area. Each group can then be optionally included in the resulting design.

The **declgroup** keyword declares an optional group with a specific identifier. An optional group may be declared in a circuit or in another optional group declaration. An optional group's identifier must be unique within the current namespace. I.e., the identifier of a top-level group declared in a circuit must not conflict with the identifier of a module, external module, or implementation defined module.

Each optional group declaration must include a string that sets the lowering convention for that group. The FIRRTL ABI specification defines supported lowering convention. One such strategy is "bind" which lowers to modules and instances which are instantiated using the SystemVerilog bind feature.

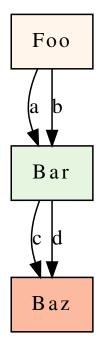

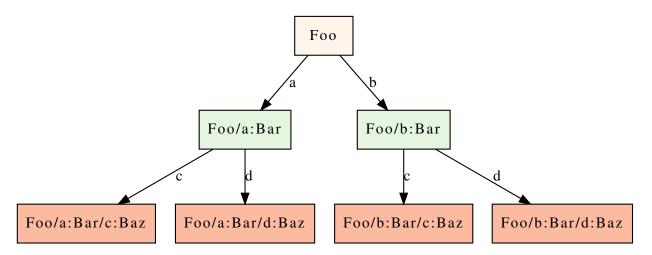

The **group** keyword defines optional functionality inside a module. An optional group may only be defined inside a module. An optional group must reference a group declared in the current circuit. Declarations of identifiers and references to existing identifiers following the same lexical scoping rules as FIRRTL conditional statements (see: Section 8.8.5)—identifiers declared in the group definition may not be used outside the group while groups may refer to identifiers declared outside the group. **The statements in a group are restricted in what identifiers they are allowed to drive.** A statement in a group may drive no sinks declared outside the group *with one exception*: a statement in a group may drive reference types declared outside the group if the reference types are associated with the group in which the statement is declared (see: Section 7.3). The circuit below contains one optional group declaration, **Bar**. Module **Foo** contains a group definition that creates a node computed from a port defined in the scope of **Foo**.

```

circuit Foo:

declgroup Bar, bind: ; Declaration of group Bar with convention "bind"

module Foo:

input a: UInt<1>

group Bar: ; Definition of group Bar inside module Foo

node notA = not(a)

```

Optional group declarations may be nested. Optional group declarations are declared with the **declgroup** keyword indented under an existing **declgroup** keyword. The circuit below contains four optional group declarations, three of which are nested. Bar is the top-level group. Baz and Qux are nested under Bar. Quz is nested under Qux.

```

circuit Foo:

declgroup Bar, bind:

declgroup Baz, bind:

declgroup Qux, bind:

declgroup Quz, bind:

```

Optional group definitions must match the nesting of declared groups. Optional groups are defined under existing groups with the **group** keyword indented under an existing **group** keyword. For the four declared groups in the circuit above, the following is a legal nesting of group definitions:

```

module Foo:

input a: UInt<1>

group Bar:

node notA = not(a)

group Baz:

group Qux:

group Quz:

node notNotA = not(notA)

```

Statements in a nested optional group may only read from ports or declarations of the current module, the current group, or a parent group—statements in a group may not drive components declared outside the group except reference types associated with the same group. In the above example, notA is accessible in the group definition of Quz because notA is declared in a parent group.

In the example below, module Baz defines a group Bar. Module Baz has an output port, \_a, that is associated with the group, Bar. This port can then be driven from inside the group. In module Foo, the port may be read from inside the group. Stated differently, module Baz has an additional port \_a that is only accessible inside a defined group Bar.

```

circuit Foo:

declgroup Bar, bind:

module Baz:

output _a: Probe<UInt<1>, Bar>

wire a: UInt<1>

group Bar:

node notA = not(a)

define _a = probe(notA)

module Foo:

inst baz of Baz

group Bar:

node _b = baz._a

```

If a port is associated with a nested group then a period is used to indicate the nesting. E.g., the following circuit has a port associated with the nested group Bar.Baz:

```

circuit Foo:

declgroup Bar, bind:

declgroup Baz, bind:

module Foo:

output a: Probe<UInt<1>, Bar.Baz>

```

Optional groups will be compiled to modules whose ports are derived from what they capture from their visible scope. For full details of the way optional groups are compiled, see the FIRRTL ABI specification.

### 5.4 Externally Defined Modules

Externally defined modules are modules whose implementation is not provided in the current circuit. Only the ports and name of the externally defined module are specified in the circuit. An externally defined module may include, in order, an optional *defname* which sets the name of the external module in the resulting Verilog, zero or more name-value *parameter* statements, and zero or more *ref* statements indicating the resolved paths of the module's exported references. Each name-value parameter statement will result in a value being passed to the named parameter in the resulting Verilog. Every port or port sub-element of reference type must have exactly one **ref** statement.

The widths of all externally defined module ports must be specified. Width inference, described in Section 12, is not supported for externally defined module ports.

A common use of an externally defined module is to represent a Verilog module that will be written separately and provided together with FIRRTL-generated Verilog to downstream tools.

An example of an externally defined module with parameters is:

```

extmodule MyExternalModule :

input foo: UInt<2>

output bar: UInt<4>

output baz: SInt<8>

defname = VerilogName

parameter x = "hello"

parameter y = 42

```

An example of an externally defined module with references is:

```

extmodule MyExternalModuleWithRefs :

input foo : UInt<2>

output mysignal : Probe<UInt<1>>

output myreg : RWProbe<UInt<8>>

ref mysignal is "a.b"

ref myreg is "x.y"

```

These resolved reference paths capture important information for use in the current FIRRTL design. While they are part of the FIRRTL-level interface to the external module, they are not expected to correspond to a particular Verilog construct. They exist to carry information about the implementation of the extendule necessary for code generation of the current circuit.

The types of parameters may be any of the following literal types. See Section 6 for more information:

- 1. Integer literal, e.g. 42

- 2. String literal, e.g., "hello"

- 3. Raw String Literal, e.g., 'world'

An integer literal is lowered to a Verilog literal. A string literal is lowered to a Verilog string. A raw string literal is lowered verbatim to Verilog.

As an example, consider the following external module:

```

extmodule Foo:

parameter foo = 'hello'

parameter bar = "world"

parameter baz = 42

```

This is lowered to a Verilog instantiation site as:

```

Foo #(

.foo(hello),

.bar("world")

```

```

.baz(42) ) bar();

```

## 5.5 Implementation Defined Modules (Intrinsics)

Intrinsic modules are modules which represent implementation-defined, compiler-provided functionality. Intrinsics generally are used for functionality which requires knowledge of the implementation or circuit not available to a library writer. What intrinsics are supported by an implementation is defined by the implementation. The particular intrinsic represented by an intrinsic module is encoded in *intrinsic*. The name of the introdule is only used to identify a specific instance. An implementation shall type-check all ports and parameters. Ports may be uninferred (either width or reset) if specified by the implementation (which is useful for inspecting and interacting with those inference features).

```

intmodule MyIntrinsicModule_xhello_y64 :

input foo: UInt

output bar: UInt<4>

output baz: SInt<8>

intrinsic = IntrinsicName

parameter x = "hello"

parameter y = 42

```

The types of intrinsic module parameters may only be literal integers or string literals.

## 6 Literals

FIRRTL has both integer, string, and raw string literals.

An integer literal is a signed or unsigned decimal integer. The following are examples of integer literals:

## 42

#### -9000

A string literal is a sequence of characters with a leading " and a trailing ". The following is an example of a string literal:

"hello"

A raw string literal is a sequence of characters with a leading ' and a trailing '. The following is an example of a raw string literal:

'world'

### 6.1 Radix-specified Integer Literal

A radix-specified integer literal is a special integer literal with one of the following leading characters to indicate the numerical encoding:

- 0b for representing binary numbers

- 0o for representing octal numbers

- Od for representing decimal numbers

- Oh for representing hexadecimal numbers

Signed radix-specified integer literals have their sign before the leading encoding character.

The following string-encoded integer literals all have the value 42:

```

0b101010

0o52

0d42

0h2a

The following string-encoded integer literals all have the value -42:

```

-0b101010 -0o52 -0d42 -0h2a

Radix-specified integer literals are only usable when constructing hardware integer literals. Any use in place of an integer is disallowed.

## 7 Types

FIRRTL has four classes of types: ground types, aggregate types, reference types, and property types. Ground types are fundamental and are not composed of other types. Aggregate types and reference types are composed of one or more aggregate or ground types. Reference types may not contain other reference types. Property types represent information about the circuit that is not hardware.

## 7.1 Ground Types

There are five classes of ground types in FIRRTL: unsigned integer types, signed integer types, a clock type, reset types, and analog types.

#### 7.1.1 Integer Types

Both unsigned and signed integer types may optionally be given a known non-negative integer bit width.

UInt ; unsigned int type with inferred width SInt ; signed int type with inferred width UInt<10> ; unsigned int type with 10 bits SInt<32> ; signed int type with 32 bits

Alternatively, if the bit width is omitted, it will be automatically inferred by FIRRTL's width inferencer, as detailed in Section 12.

**7.1.1.1 Zero Bit Width Integers** Integers of width zero are permissible. They are always zero extended. Thus, when used in an operation that extends to a positive bit width, they behave like a zero. While zero bit width integers carry no information, we allow 0-bit integer constant zeros for convenience: UInt<0>(0) and SInt<0>(0).

```

wire zero_u : UInt<0>

invalidate zero_u

wire zero_s : SInt<0>

invalidate zero_s

wire one_u : UInt<1>

connect one_u, zero_u

wire one_s : SInt<1>

connect one_s, zero_s

Is equivalent to:

wire one_u : UInt<1>

connect one_

```

connect one\_u, UInt<1>(0)

wire one\_s : SInt<1>

connect one s, SInt<1>(0)

#### 7.1.2 Clock Type

The clock type is used to describe wires and ports meant for carrying clock signals. The usage of components with clock types are restricted. Clock signals cannot be used in most primitive operations, and clock signals can only be connected to components that have been declared with the clock type.

The clock type is specified as follows:

#### Clock

#### 7.1.3 Reset Type

The uninferred **Reset** type is either inferred to **UInt**<1> (synchronous reset) or **AsyncReset** (asynchronous reset) during compilation.

#### Reset ; inferred type AsyncReset

Synchronous resets used in registers will be mapped to a hardware description language representation for synchronous resets.

The following example shows an uninferred reset that will get inferred to a synchronous reset.

```

input a : UInt<1>

wire reset : Reset

connect reset, a

```

After reset inference, reset is inferred to the synchronous **UInt**<1> type:

```

input a : UInt<1>

wire reset : UInt<1>

connect reset, a

```

Asynchronous resets used in registers will be mapped to a hardware description language representation for asynchronous resets.

The following example demonstrates usage of an asynchronous reset.

```

input clock : Clock

input reset : AsyncReset

input x : UInt<8>

regreset y : UInt<8>, clock, reset, UInt(123)

; ...

```

Inference rules are as follows:

- 1. An uninferred reset driven by and/or driving only asynchronous resets will be inferred as asynchronous reset.

- 2. An uninferred reset driven by and/or driving both asynchronous and synchronous resets is an error.

- 3. Otherwise, the reset is inferred as synchronous (i.e. the uninferred reset is only invalidated or is driven by or drives only synchronous resets).

**Reset**s, whether synchronous or asynchronous, can be cast to other types. Casting between reset types is also legal:

```

input a : UInt<1>

output y : AsyncReset

output z : Reset

wire r : Reset

connect r, a

connect y, asAsyncReset(r)

connect z, asUInt(y)

```

See Section 10 for more details on casting.

#### 7.1.4 Analog Type

The analog type specifies that a wire or port can be attached to multiple drivers. **Analog** cannot be used as part of the type of a node or register, nor can it be used as part of the datatype of a memory. In this respect, it is similar to how inout ports are used in Verilog, and FIRRTL analog signals are often used to interface with external Verilog or VHDL IP.

In contrast with all other ground types, analog signals cannot appear on either side of a connection statement. Instead, analog signals are attached to each other with the commutative attach statement. An analog signal may appear in any number of attach statements, and

a legal circuit may also contain analog signals that are never attached. The only primitive operations that may be applied to analog signals are casts to other signal types.

When an analog signal appears as a field of an aggregate type, the aggregate cannot appear in a standard connection statement.

As with integer types, an analog type can represent a multi-bit signal. When analog signals are not given a concrete width, their widths are inferred according to a highly restrictive width inference rule, which requires that the widths of all arguments to a given attach operation be identical.

```

Analog<1> ; 1-bit analog type

Analog<32> ; 32-bit analog type

Analog ; analog type with inferred width

```

## 7.2 Aggregate Types

FIRRTL supports three aggregate types: vectors, bundles, and enumeration. Aggregate types are composed of ground types or other aggregate types.

#### 7.2.1 Vector Types

A vector type is used to express an ordered sequence of elements of a given type. The length of the sequence must be non-negative and known.

The following example specifies a ten element vector of 16-bit unsigned integers.

#### UInt<16>[10]

The next example specifies a ten element vector of unsigned integers of omitted but identical bit widths.

#### UInt[10]

Note that any type, including other aggregate types, may be used as the element type of the vector. The following example specifies a twenty element vector, each of which is a ten element vector of 16-bit unsigned integers.

UInt<16>[10] [20]

#### 7.2.2 Bundle Types

A bundle type is used to express a collection of nested and named types. All fields in a bundle type must have a given name, and type. All names must be legal identifiers.

The following is an example of a possible type for representing a complex number. It has two fields, real, and imag, both 10-bit signed integers.

{real: SInt<10>, imag: SInt<10>}

Additionally, a field may optionally be declared with a *flipped* orientation.

#### {word: UInt<32>, valid: UInt<1>, flip ready: UInt<1>}

In a connection between circuit components with bundle types, the data carried by the flipped fields flow in the opposite direction as the data carried by the non-flipped fields.

As an example, consider a module output port declared with the following type:

```

output a: {word: UInt<32>, valid: UInt<1>, flip ready: UInt<1>}

```

In a connection to the a port, the data carried by the word and valid sub-fields will flow out of the module, while data carried by the ready sub-field will flow into the module. More details about how the bundle field orientation affects connections are explained in Section 8.1.

As in the case of vector types, a bundle field may be declared with any type, including other aggregate types.

```

{real: {word: UInt<32>, valid: UInt<1>, flip ready: UInt<1>},

imag: {word: UInt<32>, valid: UInt<1>, flip ready: UInt<1>}}

```

When calculating the final direction of data flow, the orientation of a field is applied recursively to all nested types in the field. As an example, consider the following module port declared with a bundle type containing a nested bundle type.

```

output myport: {a: UInt, flip b: {c: UInt, flip d: UInt}}

```

In a connection to myport, the a sub-field flows out of the module. The c sub-field contained in the b sub-field flows into the module, and the d sub-field contained in the b sub-field flows out of the module.

#### 7.2.3 Enumeration Types

Enumerations are structural disjoint union types. An enumeration has a number of variants, each with a type. The different variants are specified with tags. The variant types of an enumeration must all be passive and cannot contain analog or probe types.

In the following example, the first variant has the tag a with type UInt<8>, and the second variant has the tag b with type UInt<16>.

```

{|a: UInt<8>, b: UInt<16>|}

```

A variant may optionally omit the type, in which case it is implicitly defined to be UInt<0>. In the following example, all variants have the type UInt<0>.

{|a, b, c|}

#### 7.3 Reference Types

References can be exported from a module for indirect access elsewhere, and are captured using values of reference type.

For use in cross-module references (hierarchical references in Verilog), a reference to a probe of the circuit component is used. See Section 8.14 for details.

Using probe-type ports, modules may expose internals for reading and forcing without routing wires out of the design.

This is often useful for testing and verification, where probe types allow reads of the entities to be explicitly exported without hard-coding their place in the design. Instead, by using probetype references, a testbench module may express accesses to the internals which will resolve to the appropriate target language construct by the compiler (e.g., hierarchical reference).

Reference ports are not expected to be synthesizable or representable in the target language and are omitted in the compiled design; they only exist at the FIRRTL level.

Reference-type ports are statically routed through the design using the **define** statement.

There are two reference types, **Probe** and **RWProbe**, described below. These are used for indirect access to probes of the data underlying circuit constructs they originate from, captured using probe expressions (see Section 8.14).

**Probe** types are read-only, and **RWProbe** may be used with force and related statements. Prefer the former as much as possible, as read-only probes impose fewer limitations and are more amenable to optimization.

Probe references must always be able to be statically traced to their target, or to an external module's output reference. This means no conditional connections via sub-accesses, multiplexers, or other means.

Reference types compose with optional groups (see Section 5.3. A reference type may be associated with an optional group. When associated with an optional group, the reference type may only be driven from that optional group.

#### 7.3.1 Probe Types

Probe types are reference types used to access circuit elements' data remotely.

There are two probe types: **Probe** and **RWProbe**. **RWProbe** is a **Probe** type, but not the other way around.

Probe types are parametric over the type of data that they refer to, which is always passive (as defined in Section 7.7) even when the probed target is not (see Section 8.14.1.1). Probe types cannot contain reference types.

Conceptually probe types are single-direction views of the probed data-flow point. They are references to the data accessed with the probe expression generating the reference.

Examples:

```

Probe<UInt> ; readable reference to unsigned integer with inferred width

RWProbe<{x: {y: UInt}}> ; readable and forceable reference to bundle

Probe<UInt, A.B> ; readable reference associated with group A.B

```

For details of how to read and write through probe types, see Sections 9.10, 8.14.2.

All ports of probe type must be initialized with exactly one **define** statement.

Probe types are only allowed as part of module ports and may not appear anywhere else.

Sub-accesses are not allowed with types where the result is or has probe types within. This is because sub-accesses are essentially conditional connections (see Section 9.7 for details), which are not allowed with probe types. The following example demonstrates some legal and illegal expressions:

```

module NoSubAccessesWithProbes :

input x : {a : Probe<UInt[2]>, b : UInt}[3]

input i : UInt

input c : const UInt

output p : Probe<UInt>

; Illegal: x[i], x[c]

; Illegal: x[0].a[i], x[0].a[c]

; Legal:

define p = x[0].a[1]

```

Probe types may be specified as part of an external module (see Section 5.4), with the resolved referent for each specified using **ref** statements.

Probe types may target **const** signals, but cannot use rwprobe with a constant signal to produce a **RWProbe**<const T>, as constant values should never be mutated at runtime.

**7.3.1.1 Width and Reset Inference** Probe types do participate in global width and reset inference, but only in the direction of the reference itself (no inference in the other direction, even with force statements). Both inner types of the references used in a **define** statement must be identical or the same type with the destination uninferred (this is checked recursively). Additionally, any contained reset type is similarly only inferred in the direction of the reference, even if it eventually reaches a known reset type.

In the following example, the FIRRTL compiler will produce an error constrasted with inferring the input port as **AsyncReset** if a direct connection was used:

```

circuit ResetInferBad :

module ResetInferBad :

input in : Reset

output out : AsyncReset

connect out, read(probe(in))

```

The following circuit has all resets inferred to AsyncReset, however:

```

circuit ResetInferGood :

module ResetInferGood :

input in : Reset

output out : Reset

output out2 : AsyncReset

```

```

connect out, read(probe(in))

connect out2, in

```

#### 7.3.2 Input Probe References

Probe references are generally forwarded up the design hierarchy, being used to reach down into design internals from a higher point. As a result probe-type references are most often output ports, but may also be used on input ports internally, as described in this section.

Input probe references are allowed on internal modules, but they should be used with care because they make it possible to express invalid or multiple reference paths. When probe references are used to access the underlying data (e.g., with a read or force), they must target a statically known element at or below the point of that use, in all contexts. Support for other scenarios are allowed as determined by the implementation.

Input probe references are not allowed on public-facing modules: e.g., the top module and external modules.

Examples of input probe references follow.

#### 7.3.2.1 U-Turn Example

```

module UTurn:

input in : Probe<UInt>

output out : Probe<UInt>

define out = in

module RefBouncing:

input x: UInt

output y: UInt

inst u1 of UTurn

inst u2 of UTurn

node n = x

define u1.in = probe(n)

define u2.in = u1.out

connect y, read(u2.out) ; = x

```

In the above example, the probe of node n is routed through two modules before its resolution.

**7.3.2.2** Invalid Input Reference When using a probe reference, the target must reside at or below the point of use in the design hierarchy. Input references make it possible to create designs where this is not the case, and such upwards references are not supported:

```

module Foo:

input in : Probe<UInt>

```

```

output out : UInt

connect out, read(in)

```

Even when the target resolves at or below, the path must be the same in all contexts so a single description of the module may be generated.

The following example demonstrates such an invalid use of probe references:

```

circuit Top:

module Top:

input in : UInt<4>

output out : UInt

inst ud1 of UpDown

connect ud1.in, in

define ud1.in ref = ud1.r1

inst ud2 of UpDown

connect ud2.in, in

define ud2.in ref = ud2.r2

connect out, add(ud1.out, ud2.out)

module UpDown:

input in : UInt<4>

input in ref : Probe<UInt<4>>

output r1 : Probe<UInt<4>>

output r2 : Probe<UInt<4>>

output out : UInt

; In ud1, this is UpDown.n1, in ud2 this is UpDown.n2 .

; However, this is not supported as it cannot be both at once.

connect out, read(in ref)

node n1 = and(in, UInt<4>(1))

node n2 = and(in, UInt<4>(3))

define r1 = probe(n1)

define r2 = probe(n2)

```

**7.3.2.3 IO** with references to endpoint data A primary motivation for input probe references is that in some situations they make it easier to generate the FIRRTL code. While output references necessarily capture this design equivalently, this can be harder to generate and so is useful to support.

The following demonstrates an example of this, where it's convenient to use the same bundle type as both output to one module and input to another, with references populated by both modules targeting signals of interest at each end. For this to be the same bundle type – input on one and output on another – the **Probe** references for each end should be output-oriented and accordingly are input-oriented at the other end. It would be inconvenient to generate this design so that each has output probe references only.

The Connect module instantiates a Producer and Consumer module, connects them using a bundle with references in both orientations, and forwards those references for inspection up the hierarchy. The probe targets are not significant, here they are the same data being sent between the two, as stored in each module.

```

module Consumer:

input in : {a: UInt, pref: Probe<UInt>, flip cref: Probe<UInt>}

; . . .

node n = in.a

define in.cref = probe(n)

module Producer:

output out : {a: UInt, pref: Probe<UInt>, flip cref: Probe<UInt>}

wire x : UInt

define out.pref = probe(x)

; ...

connect out.a, x

module Connect:

output out : {pref: Probe<UInt>, cref: Probe<UInt>}

inst a of Consumer

inst b of Producer

: Producer => Consumer

connect a.in.a, b.out.a

define a.in.pref = b.out.pref

define b.out.cref = a.in.cref

; Send references out

define out.pref = b.out.pref

define out.cref = a.in.cref

module Top:

inst c of Connect

node producer_debug = read(c.out.pref); ; Producer-side signal

node consumer debug = read(c.out.cref); ; Consumer-side signal

```

## 7.4 Type Alias

A type alias is a mechanism to assign names to existing FIRRTL types. Type aliases enables their reuse across multiple declarations.

```

type WordType = UInt<32>

type ValidType = UInt<1>

type Data = {w: WordType, valid: ValidType, flip ready: UInt<1>}

type AnotherWordType = UInt<32>

module TypeAliasMod:

input in: Data

output out: Data

wire w: AnotherWordType

connect w, in.w

...

```

The type declaration is globally defined and all named types exist in the same namespace and thus must all have a unique name. Type aliases do not share the same namespace as modules; hence it is allowed for type aliases to conflict with module names. Note that when we compare two types, the equivalence is determined solely by their structures. For instance types of w and in.w are equivalent in the example above even though they are different type alias.

## 7.5 Property Types

FIRRTL property types represent information about the circuit that is not hardware. This is useful to capture domain-specific knowledge and design intent alongside the hardware description within the same FIRRTL.

Property types cannot affect hardware functionality or the hardware ABI. They cannot be used in any hardware types, including aggregates and references. They only exist to augment the hardware description with extra information.

Handling of property types is completely implementation-defined. A valid FIRRTL compiler implementation may do anything with property types as long as the existence of property types does not affect hardware functionality or the hardware ABI. For example, it is valid to drop property types from the IR completely.

Property types are legal in the following constructs:

• Port declarations on modules and external modules

#### 7.5.1 Integer Property Types

Integer property types represent arbitrary precision signed integer values.

```

module Example:

input intProp : Integer ; an input port of Integer property type

```

## 7.6 Type Modifiers

#### 7.6.1 Constant Type

A constant type is a type whose value is guaranteed to be unchanging at circuit execution time. Constant is a constraint on the mutability of the value, it does not imply a literal value at a point in the emitted design. Constant types may be used in ports, wire, nodes, and generally anywhere a non-constant type is usable. Operations on constant type are well defined. As a general rule (with any exception listed in the definition for such operations as have exceptions), an operation whose arguments are constant produces a constant. An operation with some non-constant arguments produce a non-constant. Constants can be used in any context with a source flow which allows a non-constant. Constants may be used as the target of a connect so long as the source of the connect is itself constant. These rules ensure all constants are derived from constant integer expressions or from constant-typed input ports of the top-level module.

```

const UInt<3>

const SInt

const {real: UInt<32>, imag : UInt<32>, other : const SInt}

```

Last-connect semantics of constant typed values are well defined, so long as any control flow is conditioned on an expression which has a constant type. This means if a constant is being assigned to in a **when** block, the **when**'s condition must be a constant.

Output ports of external modules and input ports to the top-level module may be constant. In such case, the value of the port is not known, but that it is non-mutating at runtime is known.

The indexing of a constant aggregate produces a constant of the appropriate type for the element.

**7.6.1.1** A note on implementation Constant types are a restriction on FIRRTL types. Therefore, FIRRTL structures which would be expected to produce certain Verilog structures will produce the same structure if instantiated with a constant type. For example, an input port of type **const UInt** will result in a port in the Verilog, if under the same conditions an input port of type **UInt** would have.

It is not intended that constants are a replacement for parameterization. Constant typed values have no particular meta-programming capability. It is, for example, expected that a module with a constant input port be fully compilable to non-parameterized Verilog.

## 7.7 Passive Types

It is inappropriate for some circuit components to be declared with a type that allows for data to flow in both directions. For example, all sub-elements in a memory should flow in the same direction. These components are restricted to only have a passive type.

Intuitively, a passive type is a type where all data flows in the same direction, and is defined to be a type that recursively contains no fields with flipped orientations. Thus all ground types are passive types. Vector types are passive if their element type is passive. And bundle types are passive if no fields are flipped and if all field types are passive.

All property types are passive.

## 7.8 Type Equivalence

The type equivalence relation is used to determine whether a connection between two components is legal. See Section 8.1 for further details about connect statements.

An unsigned integer type is always equivalent to another unsigned integer type regardless of bit width, and is not equivalent to any other type. Similarly, a signed integer type is always equivalent to another signed integer type regardless of bit width, and is not equivalent to any other type.

Clock types are equivalent to clock types, and are not equivalent to any other type.

An uninferred **Reset** can be connected to another **Reset**, **UInt** of unknown width, **UInt**<1>, or **AsyncReset**. It cannot be connected to both a **UInt** and an **AsyncReset**.

The AsyncReset type can be connected to another AsyncReset or to a Reset.

Two enumeration types are equivalent if both have the same number of variants, and both the enumerations' i'th variants have matching names and equivalent types.

Two vector types are equivalent if they have the same length, and if their element types are equivalent.

Two bundle types are equivalent if they have the same number of fields, and both the bundles' i'th fields have matching names and orientations, as well as equivalent types. Consequently, {a:UInt, b:UInt} is not equivalent to {b:UInt, a:UInt}, and {a: {flip b:UInt}} is not equivalent to {b:UInt, a:UInt}.

Two property types are equivalent if they are the same concrete property type.

## 8 Statements

Statements are used to describe the components within a module and how they interact.

#### 8.1 Connects

The connect statement is used to specify a physically wired connection between two circuit components.

The following example demonstrates connecting a module's input port to its output port, where port myinput is connected to port myoutput.

```

module MyModule :

input myinput: UInt

```

```

output myoutput: UInt

connect myoutput, myinput

```

In order for a connection to be legal the following conditions must hold:

- 1. The types of the left-hand and right-hand side expressions must be equivalent (see Section 7.8 for details).

- 2. The flow of the left-hand side expression must be sink or duplex (see Section 11 for an explanation of flow).

- 3. Either the flow of the right-hand side expression is source or duplex, or the right-hand side expression has a passive type.

- 4. The left-hand side and right-hand side types are not property types.

Connect statements from a narrower ground type component to a wider ground type component will have its value automatically sign-extended or zero-extended to the larger bit width. The behavior of connect statements between two circuit components with aggregate types is defined by the connection algorithm in Section 8.1.1.

#### 8.1.1 The Connection Algorithm

Connect statements between ground types cannot be expanded further.

Connect statements between two vector typed components recursively connects each subelement in the right-hand side expression to the corresponding sub-element in the left-hand side expression.

Connect statements between two bundle typed components connects the i'th field of the right-hand side expression and the i'th field of the left-hand side expression. If the i'th field is not flipped, then the right-hand side field is connected to the left-hand side field. Conversely, if the i'th field is flipped, then the left-hand side field is connected to the right-hand side field.

#### 8.1.2 Last Connect Semantics

Ordering of connects is significant. Later connects take precedence over earlier ones. In the following example port b will be connected to myport1, and port a will be connected to myport2:

```

module MyModule :

input a: UInt

input b: UInt

output myport1: UInt

output myport2: UInt

connect myport1, a

connect myport1, b

connect myport2, a

```

Conditional statements are affected by last connect semantics. For details see Section 8.8.6.

When a connection to a component with an aggregate type is followed by a connection to a sub-element of that same component, only the connection to the sub-element is overwritten. Connections to the other sub-elements remain unaffected. In the following example the c sub-element of port portx will be connected to the c sub-element of myport, and port porty will be connected to the b sub-element of myport.

module MyModule :

input portx: {b: UInt, c: UInt}

input porty: UInt

output myport: {b: UInt, c: UInt}

connect myport, portx

connect myport.b, porty

The above circuit can be rewritten as:

```

module MyModule :

input portx: {b: UInt, c: UInt}

input porty: UInt

output myport: {b: UInt, c: UInt}

connect myport.b, porty

connect myport.c, portx.c

```

When a connection to a sub-element of an aggregate component is followed by a connection to the entire circuit component, the later connection overwrites the earlier sub-element connection.

```

module MyModule :

input portx: {b: UInt, c: UInt}

input porty: UInt

output myport: {b: UInt, c: UInt}

connect myport.b, porty

connect myport, portx

```

The above circuit can be rewritten as:

```

module MyModule :

input portx: {b: UInt, c: UInt}

input porty: UInt

output myport: {b: UInt, c: UInt}

connect myport, portx

```

See Section 9.5 for more details about sub-field expressions.

#### 8.2 Empty

The empty statement does nothing and is used simply as a placeholder where a statement is expected. It is specified using the **skip** keyword.

The following example:

```

connect a, b

skip

connect c, d

```

can be equivalently expressed as:

connect a, b

connect c, d

The empty statement is most often used as the **else** branch in a conditional statement, or as a convenient placeholder for removed components during transformational passes. See Section 8.8 for details on the conditional statement.

#### 8.3 Wires

A wire is a named combinational circuit component that can be connected to and from using connect statements.

The following example demonstrates instantiating a wire with the given name mywire and type UInt.

```

wire mywire: UInt

```

#### 8.4 Registers

A register is a named stateful circuit component. Reads from a register return the current value of the element, writes are not visible until after a positive edges of the register's clock port.

The clock signal for a register must be of type Clock. The type of a register must be a passive type (see Section 7.7) and may not be const.

Registers may be declared without a reset using the **reg** syntax and with a reset using the **regreset** syntax.

#### 8.4.1 Registers without Reset

The following example demonstrates instantiating a register with the given name myreg, type **SInt**, and is driven by the clock signal myclock.

```

wire myclock: Clock

reg myreg: SInt, myclock

; ...

```

#### 8.4.2 Registers with Reset

A register with a reset is declared using **regreset**. A **regreset** adds two expressions after the type and clock arguments: a reset signal and a reset value. The register's value is updated with the reset value when the reset is asserted. The reset signal must be a **Reset**, **UInt**<1>, or **AsyncReset**, and the type of initialization value must be equivalent to the declared type of the register (see Section 7.8 for details). If the reset signal is an **AsyncReset**, then the reset value must be a constant type. The behavior of the register depends on the type of the reset signal. **AsyncReset** will immediately change the value of the register. **UInt**<1> will not change the value of the register until the next positive edge of the clock signal (see Section 7.1.3). **Reset** is an abstract reset whose behavior depends on reset inference. In the following example, **myreg** is assigned the value **myinit** when the signal **myreset** is high.

```

wire myclock: Clock

wire myreset: UInt<1>

wire myinit: SInt

regreset myreg: SInt, myclock, myreset, myinit

; ...

```

A register is initialized with an indeterminate value (see Section 16.1).

#### 8.5 Invalidates

An invalidate statement is used to indicate that a circuit component contains indeterminate values (see Section 16.1). It is specified as follows:

#### wire w: UInt invalidate w

Invalidate statements can be applied to any circuit component of any type. However, if the circuit component cannot be connected to, then the statement has no effect on the component. This allows the invalidate statement to be applied to any component, to explicitly ignore initialization coverage errors.

The following example demonstrates the effect of invalidating a variety of circuit components with aggregate types. See Section 8.5.1 for details on the algorithm for determining what is invalidated.

```

module MyModule :

input in: {flip a: UInt, b: UInt}

output out: {flip a: UInt, b: UInt}

wire w: {flip a: UInt, b: UInt}

invalidate in

invalidate out

invalidate w

```

is equivalent to the following:

```

module MyModule :

input in: {flip a: UInt, b: UInt}

output out: {flip a: UInt, b: UInt}

wire w: {flip a: UInt, b: UInt}

invalidate in.a

```

```

invalidate out.b

invalidate w.a

invalidate w.b

```

The handing of invalidated components is covered in Section 16.1.

#### 8.5.1 The Invalidate Algorithm

Invalidating a component with a ground type indicates that the component's value is undetermined if the component has sink or duplex flow (see Section 11). Otherwise, the component is unaffected.

Invalidating a component with a vector type recursively invalidates each sub-element in the vector.

Invalidating a component with a bundle type recursively invalidates each sub-element in the bundle.

Components of reference and analog type are ignored, as are any reference or analog types within the component (as they cannot be connected to).

### 8.6 Attaches

The attach statement is used to attach two or more analog signals, defining that their values be the same in a commutative fashion that lacks the directionality of a regular connection. It can only be applied to signals with analog type, and each analog signal may be attached zero or more times.

```

wire x: Analog<2>

wire y: Analog<2>

wire z: Analog<2>

attach(x, y) ; binary attach

attach(z, y, x) ; attach all three signals

```

### 8.7 Nodes

A node is simply a named intermediate value in a circuit. The node must be initialized to a value with a passive type and cannot be connected to. Nodes are often used to split a complicated compound expression into named sub-expressions.

The following example demonstrates instantiating a node with the given name mynode initialized with the output of a multiplexer (see Section 9.8).

```

wire pred: UInt<1>

wire a: SInt

wire b: SInt

node mynode = mux(pred, a, b)

```

### 8.8 Conditionals

Several statements provide branching in the data-flow and conditional control of verification constructs.

#### 8.8.1 When Statements

Connections within a when statement that connect to previously declared components hold only when the given condition is high. The condition must have a 1-bit unsigned integer type.

In the following example, the wire x is connected to the input a only when the en signal is high. Otherwise, the wire x is connected to the input b.

```

module MyModule :

input a: UInt

input b: UInt

input en: UInt<1>

wire x: UInt

when en :

connect x, a

else :

connect x, b

```

**8.8.1.1** Syntactic Shorthands The else branch of a conditional statement may be omitted, in which case a default else branch is supplied consisting of the empty statement.

Thus the following example:

```

module MyModule :

input a: UInt

input b: UInt

input en: UInt<1>

wire x: UInt

when en :

connect x, a

```

can be equivalently expressed as:

```

module MyModule :

input a: UInt

input b: UInt

input en: UInt<1>

wire x: UInt

when en :

connect x, a

else :

skip

```

To aid readability of long chains of conditional statements, the colon following the **else** keyword may be omitted if the **else** branch consists of a single conditional statement.

Thus the following example:

```

module MyModule :

input a: UInt

input b: UInt

input c: UInt

input d: UInt

input c1: UInt<1>

input c2: UInt<1>

input c3: UInt<1>

wire x: UInt

when c1 :

connect x, a

else :

when c2 :

connect x, b

else :

when c3 :

connect x, c

else :

connect x, d

```

can be equivalently written as:

```

module MyModule :

input a: UInt

input b: UInt

input c: UInt

input d: UInt

input c1: UInt<1>

input c2: UInt<1>

input c3: UInt<1>

wire x: UInt

when c1 :

connect x, a

else when c2 :

connect x, b

else when c3 :

connect x, c

else :

connect x, d

```

To additionally aid readability, a conditional statement where the contents of the **when** branch consist of a single line may be combined into a single line. If an **else** branch exists, then the

else keyword must be included on the same line.

The following statement:

```

when c :

connect a, b

else :

connect e, f

```

can have the when keyword, the when branch, and the else keyword expressed as a single line:

```

when c : connect a, b else :

connect e, f

```

The **else** branch may also be added to the single line:

```

when c : connect a, b else : connect e, f

```

#### 8.8.2 Match Statements

Match statements are used to discriminate the active variant of an enumeration typed expression. A match statement must exhaustively test every variant of an enumeration. An optional binder may be specified to extract the data of the variant.

```

match x:

some(v):

connect a, v

none:

connect e, f

```

#### 8.8.3 Nested Declarations

If a component is declared within a conditional statement, connections to the component are unaffected by the condition. In the following example, register myreg1 is always connected to a, and register myreg2 is always connected to b.

```

module MyModule :

input a: UInt

input b: UInt

input en: UInt<1>

input clk : Clock

when en :

reg myreg1 : UInt, clk

connect myreg1, a

else :

reg myreg2 : UInt, clk

connect myreg2, b

```

Intuitively, a line can be drawn between a connection to a component and that component's declaration. All conditional statements that are crossed by the line apply to that connection.

#### 8.8.4 Initialization Coverage

Because of the conditional statement, it is possible to syntactically express circuits containing wires that have not been connected to under all conditions.

In the following example, the wire a is connected to the wire w when en is high, but it is not specified what is connected to w when en is low.

```

module MyModule :

input en: UInt<1>

input a: UInt

wire w: UInt

when en :

connect w, a

```

This is an illegal FIRRTL circuit and an error will be thrown during compilation. All wires, memory ports, instance ports, and module ports that can be connected to must be connected to under all conditions. Registers do not need to be connected to under all conditions, as it will keep its previous value if unconnected.

#### 8.8.5 Scoping

The conditional statement creates a new *scope* within each of its **when** and **else** branches. It is an error to refer to any component declared within a branch after the branch has ended. As mention in Section 14, circuit component declarations in a module must be unique within the module's flat namespace; this means that shadowing a component in an enclosing scope with a component of the same name inside a conditional statement is not allowed.

#### 8.8.6 Conditional Last Connect Semantics

In the case where a connection to a circuit component is followed by a conditional statement containing a connection to the same component, the connection is overwritten only when the condition holds. Intuitively, a multiplexer is generated such that when the condition is low, the multiplexer returns the old value, and otherwise returns the new value. For details about the multiplexer, see Section 9.8.

The following example:

```

wire a: UInt

wire b: UInt

wire c: UInt<1>

wire w: UInt

connect w, a

when c :

connect w, b

```

can be rewritten equivalently using a multiplexer as follows:

```

wire a: UInt

wire b: UInt

wire c: UInt<1>

wire w: UInt

connect w, mux(c, b, a)

```

Because invalid statements assign indeterminate values to components, a FIRRTL Compiler is free to choose any specific value for an indeterminate value when resolving last connect semantics. E.g., in the following circuit w has an indeterminate value when c is false.

```

wire a: UInt

wire c: UInt<1>

wire w: UInt

invalidate w

when c :

connect w, a

```

A FIRRTL compiler is free to optimize this to the following circuit by assuming that w takes on the value of a when c is false.

```

wire a: UInt

wire c: UInt<1>

wire w: UInt

connect w, a

```

See Section 16.1 for more information on indeterminate values.

The behavior of conditional connections to circuit components with aggregate types can be modeled by first expanding each connect into individual connect statements on its ground elements (see Section 8.1.1 for the connection algorithm) and then applying the conditional last connect semantics.

For example, the following snippet:

```

wire x: {a: UInt, b: UInt}

wire y: {a: UInt, b: UInt}

wire c: UInt<1>

wire w: {a: UInt, b: UInt}

connect w, x

when c :

connect w, y

```

can be rewritten equivalently as follows:

```

wire x: {a:UInt, b:UInt}

wire y: {a:UInt, b:UInt}

wire c: UInt<1>

wire w: {a:UInt, b:UInt}

```