# **Emerging Memories**

Livio Baldi, Gurtej Sandhu Micron Technology

©2013 Micron Technology, Inc. All rights reserved. Products are warranted only to meet Micron's production data sheet specifications. Information, products, and/or specifications are subject to change without notice. All information is provided on an "AS IS" basis without warranties of any kind. Dates are estimates only. Drawings are not to scale. Micron and the Micron logo are trademarks of Micron Technology, Inc. All other trademarks are the property of their respective owners.

ESSDERC 2013

## Outline

- □ Solid State Memories: a success story

- □ A lot of alternatives:

- Prototypal memories

- > New concepts

- □ From cell to memory

- □ Is there a winner?

## Outline

- □ Solid State Memories: a success story

- □ A lot of alternatives:

- Prototypal memories

- New concepts

- □ From cell to memory

- □ Is there a winner?

## There is more than one memory

### In our head

#### Retention time:

- Short term memory: what was in previous slide? (if you still remember it)

- Long term memory: what did you learn at school?

#### But also functions:

- **Procedural memory**: how to ride a bike, make a knot in your tie,..

- **Semantic memory**: remembering well defined data, e.g. a phone number

- **Episodic memory**: past events, e.g. your trip here, your holidays, the plot of a movie.

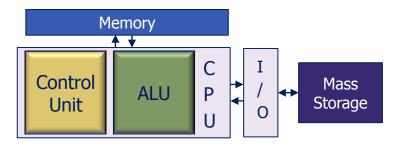

### and in computers

#### In Turing machine:

- A memory for **data** (endless tape)

- A memory for the **instructions**

Von Neumann architecture:

- One main memory for data and program

- One mass storage unit

### Memory performances

There is no single parameter to characterize memories:

- Size: how many bits in a single device?

- Retention: how long is information conserved without power supply?

- Endurance: how many times can I change the content before degradation?

- Programming speed: how fast can I change the content?

- Access speed

- Latency: how long before the first data out?

- Throughput: which is maximum reading data flow?

- Power

- Programming

- Reading

- Stand-by

COST: how many bucks per bit (or Byte, or Gigabyte)?And others (BER, T range, .....)

## The evolution of memory systems

- Early Computing

- Early Storage

IBM Hard Disk Drive 1965 Weight > 1ton Capacity: 5Mbyte

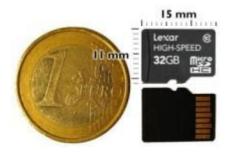

Today: • 32Gbyte microSD

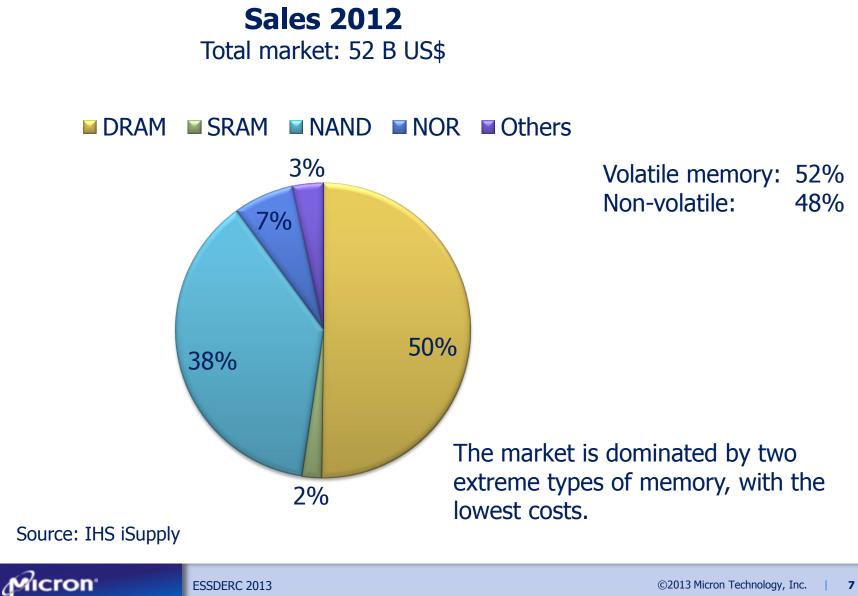

### Memory market

### Scaling Issues

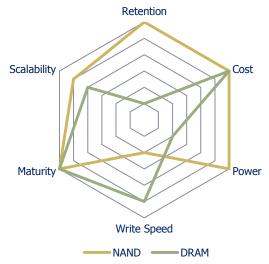

### NAND

- Active dielectric thickness

- Isolation aspect-ratio and parasitic coupling

- Statistical effects increase due to few electrons storage

- Increasing weight of Error Correction Algorithms

### • DRAM

- Cell transistor architecture in a 4F2 size (refresh time)

- Cell capacitor material with high-k dielectric

- Cell capacitor aspect ratio

### BUT:

"The reports of my death are greatly exaggerated".

©2013 Micron Technology, Inc. 9

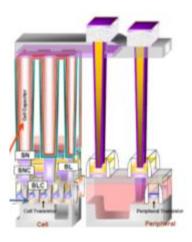

## **3-D** memories

### Manhattan approach:

- more efficient use of real estate by stacking memory cells.

- East block approach

- More efficient use of space by putting more bits in the same cell.

### **DRAM** memory

- From planar capacitor to

- vertically stacked capacitor

- vertical transistor as next step

ESSDERC 2013

Micron

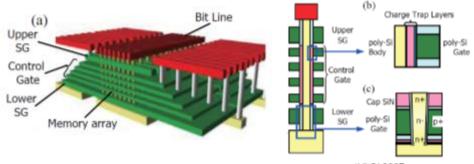

### NAND memory

- Vertically stacked memory cells

- Polysilicon channel

- Better use of area, but

- Cell footprint cannot be scaled

- Density = number of layers

- Cost = number of layers

- Multibit/cell

©2013 Micron Technology, Inc.

## Outline

### □ Solid State Memories: a success story

- □ A lot of alternatives:

- Prototypal memories

- New concepts

- □ From cell to memory

- □ Is there a winner?

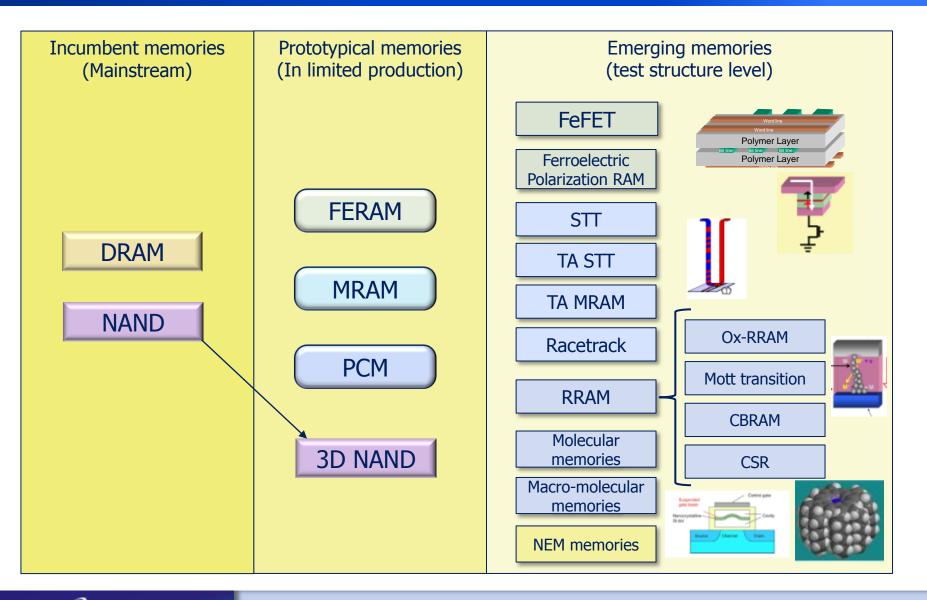

### Memory cell landscape

Micron

ESSDERC 2013

## Outline

- □ Solid State Memories: a success story

- □ A lot of alternatives:

- Prototypal memories

- > New concepts

- □ From cell to memory

- □ Is there a winner?

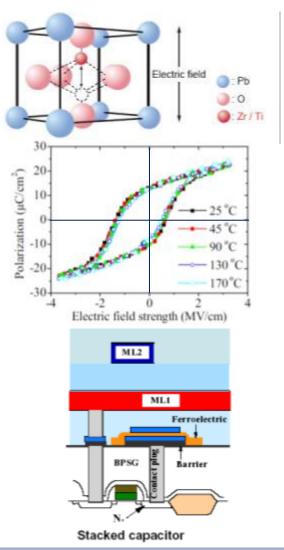

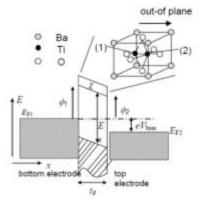

### **Ferroelectric Memories**

### Storing mechanism

- Permanent polarization of a ferroelectric material induced by external electric field, related to ion displacement in the crystal cell.

- Most common ferroelectric device is the FeRam

- DRAM-like cell: 1 transistor, 1 capacitor (1T/1C)

- Sensing through the displacement current associated to the polarization switch (destructive reading)

- Two base materials used

- PZT (PbxZr1-xTiO<sub>3</sub>), known since long time

- SBT (SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub>), more recent material (easier thickness and voltage scalability)

### FERAM: Advantages and Issues

- Advantages:

- Fast (<100ns) and low energy write.

- High write endurance.

- Medium/low voltage write.

- Issues:

- Difficult process integration.

- Large cell size (25 F<sup>2</sup>) and limited scaling potential with respect to Flash and DRAM.

- Limited read endurance, destructive read-out.

- Technology gap vs. established technologies.

- Commercially available up to 8Mb (Ramtron, Fujitsu)

- Interest revamped by two emerging concepts

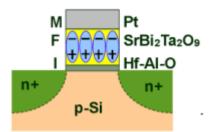

## **FeRAM emerging Memories**

#### Different sensing mechanism

- <u>Ferroelectric FET</u>: integration of ferroelectric material in transistor gate; Flash-like cell: 1 transistor.

- Direct sensing of cell threshold, non destructive reading.

- Issues: large k of ferroelectric material → thick ferroelectric layer → max. aspect ratio limits cell size

- Read disturbs

- One paper at this conference

- <u>Ferroelectric Polarization RRAM</u>: M-I-M tunnel diode where the dielectric is a ferroelectric material

- Changing ferroelectric polarization can modify the charge injection/transport properties of FE

- Different mechanisms claimed: Schottky barrier, lattice strain,...

- Low reading current due to tunnel effect.

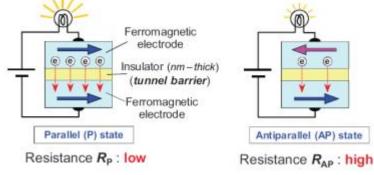

### **Magnetic Memories**

#### Storing mechanism

- Permanent magnetization of a ferromagnetic material

- Sensing mechanism

- Tunnelling current between two ferromagnetic layers

- One 'free' magnetic layer (easily switchable) and one pinned reference layer

- Tunnel current depending on mutual orientation of magnetic layers

- Main advantages

- Fast write (<100ns)</li>

- Low voltage write

- High write endurance

Freescale first product: 4Mb in 2006

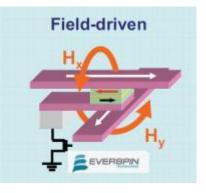

### **First Generation**

- Tunnel MagnetoResistance (TMR)

- Programming by current induced magnetic field

- Main issues

- Difficult process integration (10-12 layers required due to layer matching requirements)

- Large cell size vs Flash and DRAM (40-80 F<sup>2</sup>: IBM, Toshiba), difficult scaling

- Large write current (>10mA/byte), small read signal

- Programming disturbs by stray magnetic field

- Heating can assist the switching of the 'free' layer in programming and keep retention and disturb immunity low (Thermally assisted MRAM)

- However heat propagation can become an issue to scaling

©2013 Micron Technology, Inc. | 18

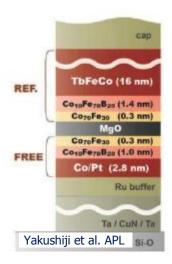

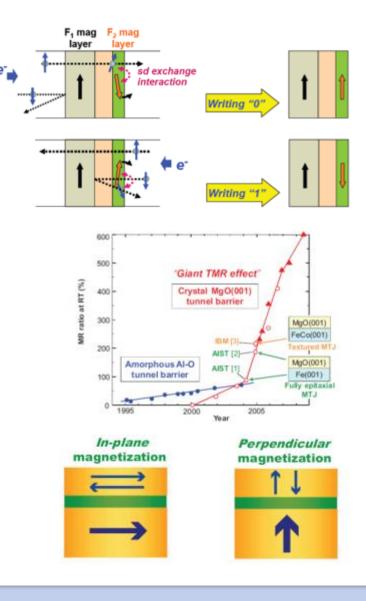

### **Second Generation**

- Spin-Transfer Torque programming

- Memory switching by injection of spinpolarized electrons

- All current directly used for switching

- Current scales with area.

- Less disturbs

- MgO dielectric replacing AlO2 -> much better signal

- Perpendicular magnetization instead of parallel -> better scaling, better thermal immunity.

- Cell size down to 14 F2 reported in literature, but average is more than 20.

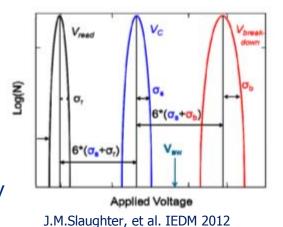

### Some concerns....

- Reading margins

- 200% is considered high for MRAM, but very low for other NVM types

- Operating margins:

- Writing voltages in the 0.5-0.6V range;

- TDDB of dielectric is around 1-1.5V;

- Read voltage in the 0.15-.2V range

- Very low margins for safe operation and disturb immunity

- Tight process control needed due to multilayer structure.

- Possibility of multi-bit operation proposed, but low reading margins.

- Complex read schemes:

- Conventional with dummy cell, but heavy stress on technology control

- Self-reference but requires write back

TDDB: Time Dependent Dielectric Breakdown

©2013 Micron Technology, Inc. | 20

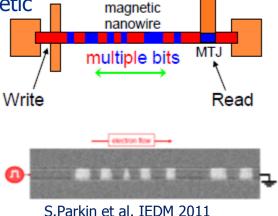

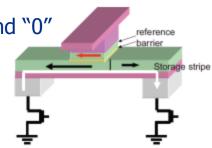

## MRAM emerging memories

- Race track memories

- Proposed by IBM (S.Parkin et al., Science 320, 190, 2008)

- Shift register organization: bit as domain orientation in magnetic nanowire.

- One write head and one read head at the ends of the strip.

- Main issues:

- Control of domain motion.

- Current values for domain shift

- Power consumption: reading requires domain shift and rewriting

- Alternative Domain Wall

- Originally proposed by NEC (H.Numata et al. VLSI 2007)

- Domain wall is shifted left and right by a current, to give "1" and "0"

- Reading by tunneling current in spin diode.

- Less reliability problems, but large cell.

©2013 Micron Technology, Inc. | 21

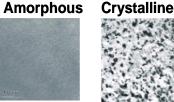

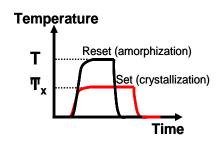

### Phase Change Memories

- Polycrystalline to amorphous transition in chalcogenide.

- Writing mechanism

- Current pulse to melt material followed by fast or slow cooling.

- Sensing mechanism

- Resistivity measurement at low currents

- Cell structure

- 1 transistor, 1 resistor (1T/1R)

- Two options: MOS transistor for embedded; bipolar for high density

- Basic material:

- GST (Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> is the most usual, but other compositions also possible)

**High resistivity**

©2013 Micron Technology, Inc. 22

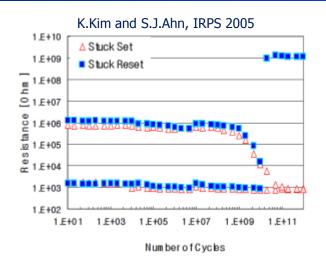

### PCM: Advantages and Issues

#### Main advantages

- Fast write (<100 ns)</li>

- Good read signal window (factor ten in resistance)

- Medium/low voltage write

- Bit granularity

- High endurance

- Cell size comparable to Flash and DRAM

- Good scalability

- Main issues

- Process integration for GST

- Heater-GST interface optimization

- Writing current (~1 mA), scalable with cell size

- Retention at high temperature (150° C). Common issue to all emerging memories

- 1Gbit memory available in 45nm technology

- DDR2 interface

- NOR Flash legacy spec + bit alterability

- Chip area: 37.5mm2

- Power supply range: 1.7V÷2.0V

- Temperature Range: -40C÷+85C

## PCM emerging memories

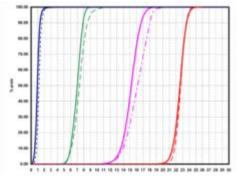

### Multi-level storage

- Proposed by IBM (Papandreou N. et al., IMW 2011)

- Using the large Ion/Ioff ratio of PCM cell it seems possible to store 2-3 bit/cell.

- Densities comparable with NAND appear possible.

- Main issues: disturbs, threshold drifts

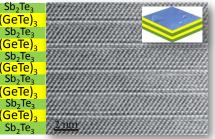

- Super-Lattice Memory

- Originally proposed by NEC (Chong et al. Appl. Phys. Lett. 88 (2006)

- A super-lattice of chalcogenide layers with thickness within the phase-transition limits.

- Phase transition assumed to be by motion of Ge atoms without melting.

- Faster switching, much lower current.

- Exact mechanism and limits not yet clarified.

Courtesy of CAMELS project, partially funded under FP6 Programme

Courtesy of PSTRY project, partially funded under FP7 Programme

©2013 Micron Technology, Inc. | 24

## Outline

### □ Solid State Memories: a success story

- □ A lot of alternatives:

- Prototypal memories

- > New concepts

- □ From cell to memory

- □ Is there a winner?

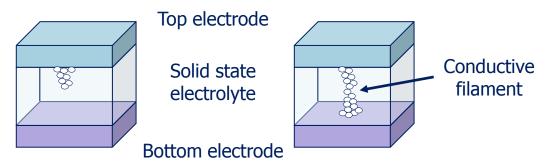

### **Resistive memories**

- Formation (and dissolution) of a conductive path between two electrodes:

- Induced by a voltage pulse

- Reversible

- Persistent in time (non volatility)

- Such as to induce large changes in resistance

- Conductive filament can have different natures:

- Metal ions (conductive bridge RRAM or CBRAM)

- Formation of traps (Oxygen vacancies) OxRRAM

- Generally requires an initialization process ('forming')

- Exact mechanism not yet defined, but phenomenological models available.

- Electrode material plays a critical role.

- ▶ 6 out of 8 papers on memories at this conference

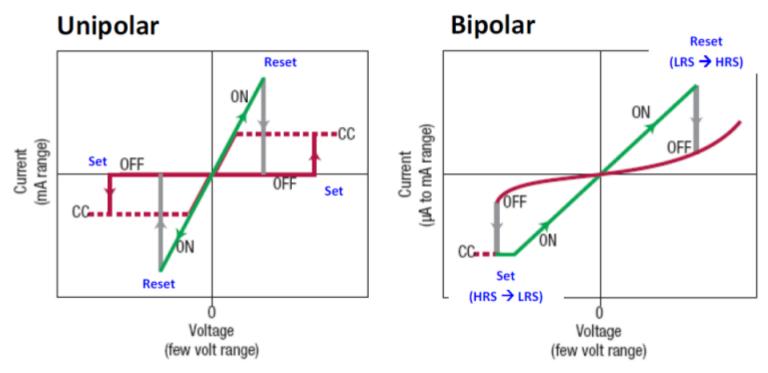

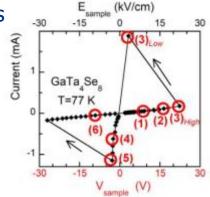

## Switching polarity

Type a – Unipolar switching device:

- Switching between ON&OFF depends only upon E amplitude

- Breakdown-type mechanism for Off to On transition (SET)

#### Type b – Bipolar switching device:

- Switching between ON&OFF depends upon E polarity

- Less stress on material

#### Micron

## **Conductive Bridge RAM**

### **Reaction environment**

### Anodic dissolution

- $\bullet$  equilibrium  $\rightarrow$  oxidation for applied bias

- electrochemical electron transfer (Butler-Volmer)

- no overpotential, fast reaction

### **Cation transport**

- drift /diffusion transport

- high fields  $\rightarrow$  drift dominant

- non-linear, very fast at high field

### **Cathodic deposition**

- electrochemical electron transfer (Butler-Volmer)

- crystallization overpotential

### **Filament growth**

Ag, Cu 🕂

SE

g<sup>+</sup>,Cu<sup>+</sup>

Pt, W, ...

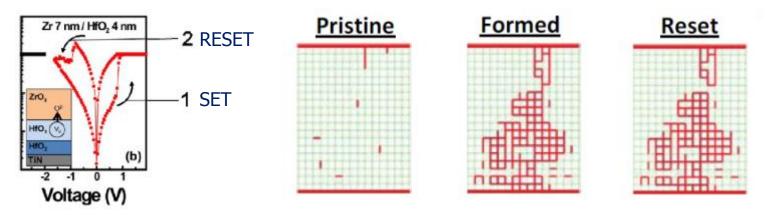

## Oxide bridge RAM

- Trap-assisted conduction in metal oxide

- Formation of a vacancy filament through a forming process (soft breakdown)

- Conduction through electron tunneling via Oxygen vacancies

- RESET by dissolution of the filament by oxygen migration and recombination.

- SET by regeneration of filament through opposite voltage.

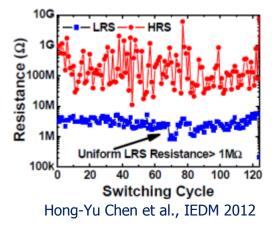

- Soft breakdown' not very reproducible:

- Dissolution of filament not always complete. High loff currents in RESET.

- Large variability in On and especially Off states

- Heating can play an important role

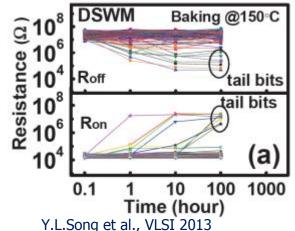

### Main concerns of RRAM

- Filament formation not very reproducible

- Strong dependence on forming process conditions

- Strong variation in loff current, both cell to cell and with cycling

- RTN noise in high resistance status

- Sensitive to temperature and voltage stress.

- But:

- Forming seems avoidable for scaled cells

- More sophisticated cell architecture and programming algorithms emerging

- Window seems to improve with cycling

- Not clear understanding of mechanism:

- Complex interplay of cell and electrode materials

- Large variety in materials investigated; materials with an history of integration in CMOS technology (TiO, WO, HfO, TaO) are preferred

©2013 Micron Technology, Inc. 31

## Other possible RRAM mechanisms

### Mott transition RAM (CeRAM)

- Charge injection induces a transition from strongly correlated to weakly correlated electrons, resulting in an insulator-metal transition.

- Explored in VO2, SmNiO3, NiO or more complex combinations (L.Cario et al., Advanced Materials 2010)

- Exact mechanism still not clear (crystal deformation?)

- Non volatile?

- Needs high voltages; 25% Ron/Roff margin at room T<sup>o</sup>

- Mixed Valence Oxide RAM

- Change of tunnel barrier height due to Oxygen ions exchange with conductive metal oxide (R.Meyer et al. NVMTS 2008)

- Bipolar switching. One order of magnitude between Ron/Roff.

- A 64Mbit memory presented at ISSCC 2010.

## More NVM Concepts: Longer Term

### A not exhaustive list.....

| Nano-electromechanical memory (NEMM)                                   |                                                                                                        |                        |                              |                       |     |

|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------|------------------------------|-----------------------|-----|

| Bi-stable nano-electromechanical switch                                | Electrostatic Attraction + Van der<br>Waals Adhesion<br>e.g. Nantero CNT memory,<br>cantilever devices |                        | T Fabric                     | ell" Cross-section    |     |

| Issues: scalability, endurance, stick                                  | NRAM Cell<br>Figure 1                                                                                  | Top                    | o View CNT Fabric            |                       |     |

| Macromolecular (polymeric)                                             | a d a                                                                                                  | $\sim$                 | PH 150°C<br>• rev<br>2 - for |                       |     |

| Polymers with two resistivity states (bengal rose, fluoreiscine)       | Switching between different redox states, charge trapping                                              |                        | NEO CO                       |                       |     |

| Issues: material stability, mechanis                                   | Bengal Rose                                                                                            | Fluorescei             | n •                          | 2<br>Voltage (V)      |     |

| Molecular memories                                                     | initial                                                                                                |                        | read                         | erase                 |     |

| Single molecules in a cross-point array                                | Voltage Driven Change in electronic states in Redox                                                    | 0yN 4                  | 0,4 U NH2 1                  |                       | 0,4 |

| Issues: difficulty in handling single parameters, addressing problems. | Au<br>low σ<br>V = 0                                                                                   | Au<br>high σ<br>V = V+ | ku<br>high σ<br>V>0          | λυ<br>Ιου σ<br>V = V- |     |

## Outline

- □ Solid State Memories: a success story

- □ A lot of alternatives:

- Prototypal memories

- > New concepts

- □ From cell to memory

- □ Is there a winner?

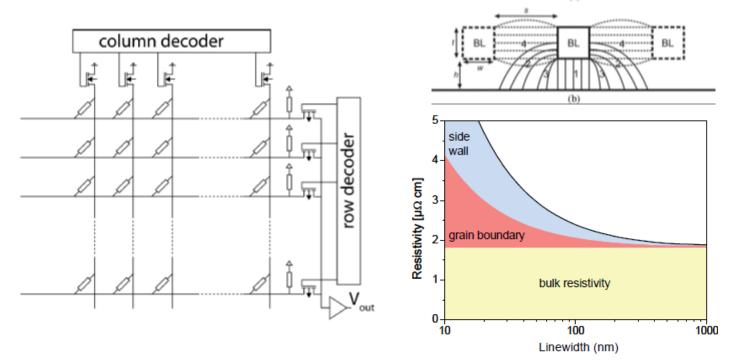

### Memory as a system

### Two main functions to an electronic memory:

- Data storage

- Data retrieval

- Memories are organized in arrays

- Storing and retrieval requires selecting the cell

- Cell selection can be the major issue for different types of storage and is the main contributor to size of memory array.

- Cell selection is often the most critical issue for emerging memories.

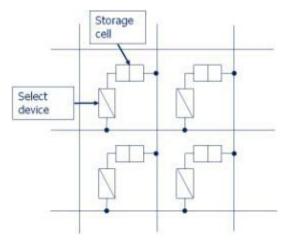

## Cell selector and array organization

- Cell selection within the array, and array characteristics can play a major role in the selection of memory technology.

- The selector allows a given memory cell in an array to be addressed for read or write.

- Key requirements for select device:

- Strong non linear characteristic (switch).

- In the On state: capability to handle the current required by the memory cell

- In the Off state: very low leakage current (it limits max. size of array)

- Compatibility with the process of the memory cell.

- Small size.

- Scalability.

- The requirements are especially critical for memories that require bipolar switching.

#### Micron

### Selector types

- Transistor

- MOS: easy to integrate, good performances, large size (DRAM, MRAM, FERAM)

- Bipolar: more complex process, good performances, smaller size (PCM)

- Diodes (unipolar)

- p-n in substrate: good performances, not for cross-point arrays

- p-n in poly: can be integrated in back-end, poor Ion/Ioff

- Schottky: low Ion density, poor Ion/Ioff

- Bipolar devices

- Devices with strongly non-linear symmetrical I\_V characteristics, e.g.

- Metal-Insulator Transition switch (MIT), e.g. Mott transition switch:

- Threshold Switch, e.g. Ovonic Threshold Switch

- Mixed electronic and ionic conduction (MIEC)

- Very little data available

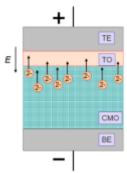

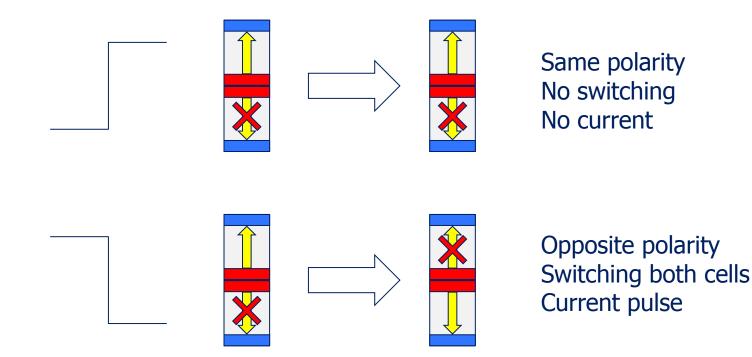

### **Complementary Resistive Switch**

- An architectural solution

- Two bipolar RRAM disposed back-to-back.

- A voltage pulse generate s a current pulse only if polarity is such as to switch both devices.

Destructive reading as in FeRAM

### **Real Arrays**

- In real arrays, parasitic capacitance and resistance of interconnects cannot be neglected.

- Uniform scaling keeps capacitance constant but increases resistance.

- Also resistivity increases because of sidewall scattering.

- Interconnection delay and capacitance charging time can limit size of memory arrays.

©2013 Micron Technology, Inc. | 40

## Outline

- □ Solid State Memories: a success story

- □ A lot of alternatives:

- Prototypal memories

- New concepts

- □ From cell to memory

- □ Is there a winner?

### In summary

Source S.Lai

#### The ideal memory:

- High density

- Low power consumption

- Non-volatility

- ► Fast read/write/erase

- Random read/write access

- Endurance against write/erase cycles

- Scalability with low cost

#### and what is available (from ITRS ERD 2011)

|                  | Prototypical (Table ERD3) |          |          | Emerging (Table ERD5)     |                          |              |             |                          |                     |

|------------------|---------------------------|----------|----------|---------------------------|--------------------------|--------------|-------------|--------------------------|---------------------|

| Parameter        | FeRAM                     | STT-MRAM | PCRAM    | Emerging<br>ferroelectric | Nanomechanical<br>memory | Redox memory | Mott Memory | Macromolecular<br>memory | Molecular<br>Memory |

| Scalability      |                           | <u>.</u> | <u> </u> | <u> </u>                  |                          | <b>(</b> )   | •           | •                        | <u>.</u>            |

| MLC              |                           |          | <u>.</u> |                           |                          | <u> </u>     | ?           | <u>.</u>                 | 2                   |

| 3D integration   |                           | <u>.</u> | <u>.</u> |                           |                          | <u></u>      | ?           | <u> </u>                 |                     |

| Fabrication cost | <u></u>                   | <u></u>  | <u>.</u> | <u></u>                   |                          |              | ?           | <u> </u>                 | ?                   |

| Endurance        | <u>.</u>                  | <u>.</u> | <u></u>  | <u>••</u>                 |                          | <u> </u>     | :           | -                        | ?                   |

Probably we have to settle for less: no 'universal memory', but several new concepts with interesting performances.

## **Emerging Memories**

A few warnings

- Most of the emerging memories have low programming voltages/energy:

- □ Low power dissipation, high programming speed, but

- □ Low temperature stability

- □ Low reading voltage → low On/Off margin

- Difficulty to have multilevel storage

- High sensitivity to read disturbs

- Some concepts are not easily scalable (STT, FeRAM)

- Cross-point cell looks attractive, but:

- Scaling depends on the availability of next generation lithography

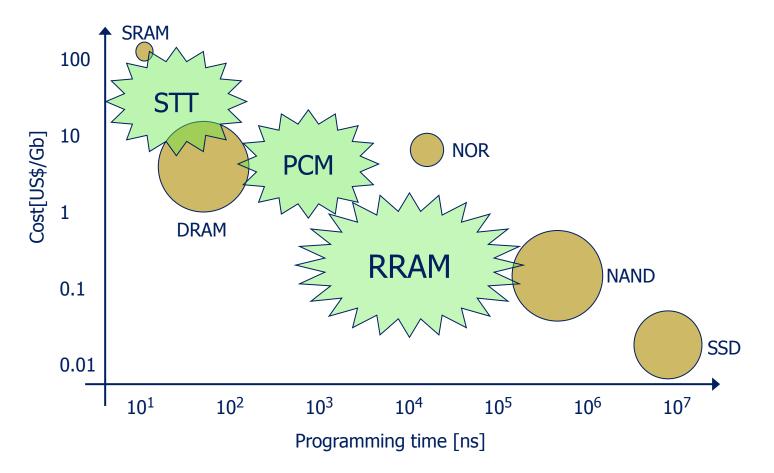

### The competition arena

- New memories can fill the gaps between consolidated technologies

- Gain at system level.

Micron

## Can we live with one memory?

Three strategy options for new memories:

- Compete with mainstream memory for cost (DRAM and NAND are hard to beat)

- Higher cost but replace more memory types (saving at system level)

- Find a niche in an intermediate position.

#### Micron

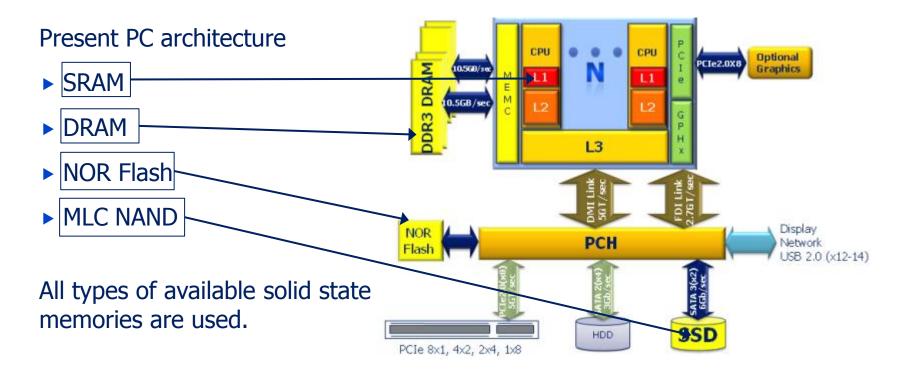

### **Computer architectures**

### A mixed future

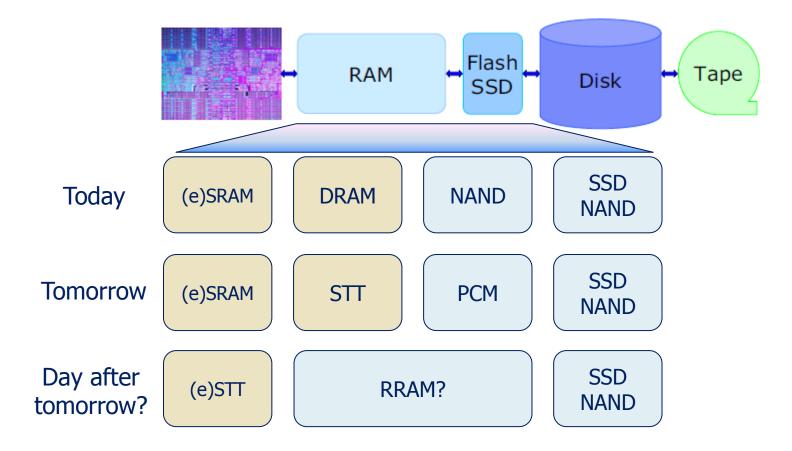

- In the longer term the competition is still open between different alternative memories:

- Choices on materials and architectures are needed to achieve critical mass.

- Array and selector technology will be as important as the memory cell.

- Probably no "universal solution" but a differentiated landscape

- Memory systems combining different memory types in the same package will probably be the winning solution.