# Front-End Symposium Intro

Steve Hoover

Redwood EDA

# VSDOpen Conference 2018

# FRONT-END AGENDA

#### Steve:

- Open-Source H/W Trends

- TL-Verilog Primer

#### Ákos:

- Formal Verification of WARP-V, a TL-Verilog RISC-V Core Generator

- Ahmed:

- Top-Down Transaction-Level Design with TL-Verilog

# OPEN SOURCE H/W - What's keeping us back?

- 1. Access to tools

- 2. Access to h/w

- 3. Complexity/Scale

# ...AND THE WALLS ARE BREAKING DOWN!!!

- 1. Access to tools

- Complete open-source FPGA design flows now exist

- 2. Access to h/w

- Cloud FPGAs are the answer!

- 3. Complexity/Scale

- TL-Verilog

# **IMPACT**

- Greater impact than open-source s/w

- Start-up culture will thrive!

- Just in time for the "golden age of computing"

# 4th Barrier - Patents

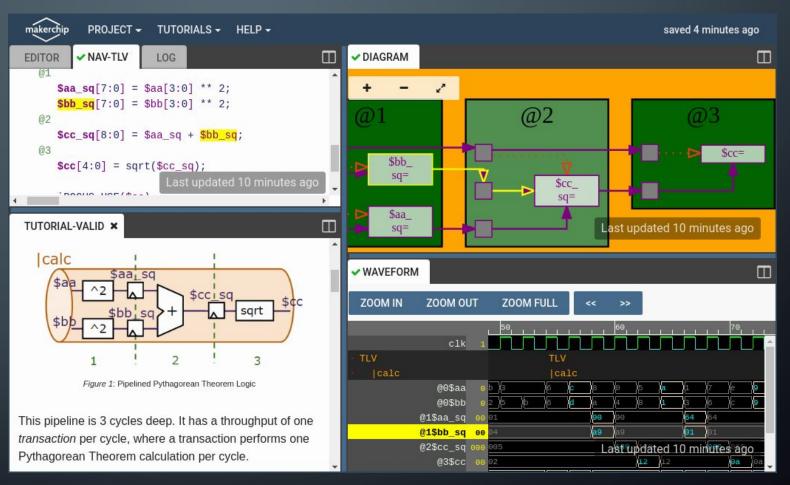

## MAKERCHIP

- 1. Access to tools- in browser

- 2. Access to h/w

- Cloud FPGAs

- 3. Complex./Scale

- TL-Verilog

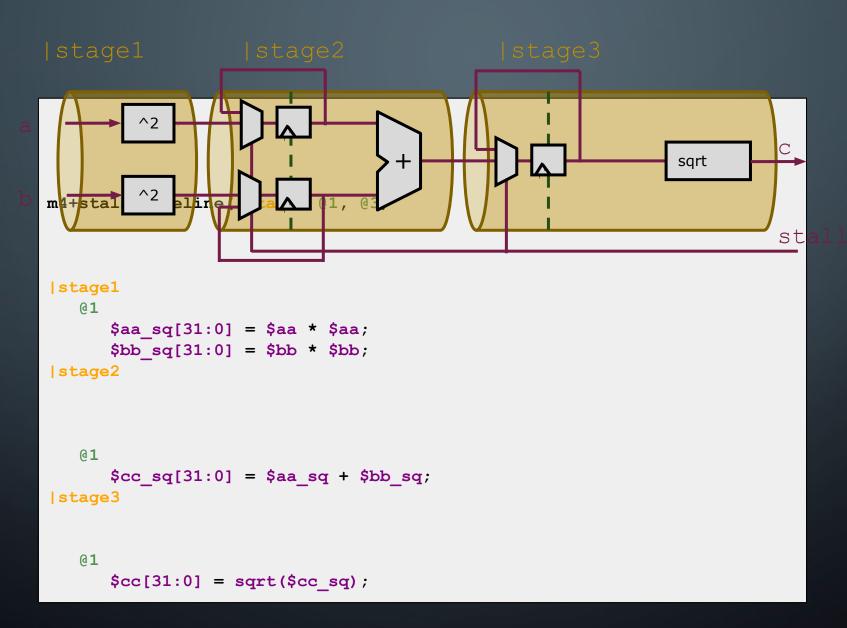

# TIMING ABSTRACTION

#### RTL:

### Timing-abstract:

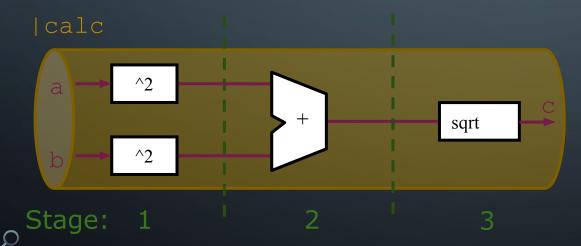

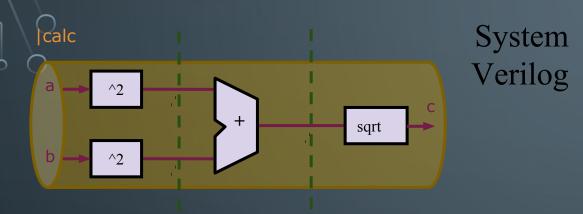

$$c = sqrt(a^2 + b^2)$$

→ Flip-flops and staged signals are implied from context.

## TL-VERILOG VS. SYSTEMVERILOG

## TL-Verilog

```

// Calc Pipeline

logic [31:0] a C1;

logic [31:0] b C1;

logic [31:0] a sq C1,

a_sq_C2;

logic [31:0] b_sq_C1,

b_sq_C2;

logic [31:0] c sq C2,

c sq C3;

logic [31:0] c C3;

always ff @(posedge clk) a sq C2 <= a sq C1;

always ff @(posedge clk) b sq C2 <= b sq C1;

always ff @(posedge clk) c sq C3 <= c sq C2;

// Stage 1

assign a_sq_C1 = a_C1 * a_C1;

assign b sq C1 = b C1 * b C1;

// Stage 2

assign c sq C2 = a sq C2 + b sq C2;

// Stage 3

assign c_C3 = sqrt(c_sq_C3);

```

## ADDING BACKPRESSURE