Четырёхъядерная система на кристалле с 64-битной архитектурой SPARC v.9, работающая на тактовой частоте до 1 ГГц при технологических нормах 90 нм.

Четырёхъядерная система на кристалле с 64-битной архитектурой SPARC v.9, работающая на тактовой частоте до 1 ГГц при технологических нормах 90 нм.

Микропроцессор МЦСТ R1000 (1891ВМ6Я, проектное название МЦСТ-4R) – четырёхъядерная система на кристалле с 64-битной архитектурой SPARC v.9. Поддерживаются векторные расширения VIS1 и VIS2, а также дополнительные инструкции для комбинированных и упакованных операций.

Особенности процессора МЦСТ R1000:

Основная сфера применения микропроцессора МЦСТ R1000 – использование в многопроцессорных системах с общей памятью (NUMA), рассчитанных на высокие показатели производительности (напр., вычислительные комплексы для АСУ), создание одноплатных встраиваемых ЭВМ и промышленных компьютеров.

| Характеристика | Значение |

|---|---|

| Обозначение микросхемы | 1891ВМ6Я |

| Архитектура | SPARC V9/JPS1 |

| Тактовая частота | до 1000 МГц |

| Число ядер | 4 |

| Операций в такт (на ядро) | до 2 |

| Кэш-память данных 1-го уровня, на ядро | 32 Кб |

| Кэш-память команд 1-го уровня, на ядро | 16 Кб |

| Кэш-память 2-го уровня (универсальная) | 2 МБ |

| Организация оперативной памяти | DDR2-800 |

| Пропускная способность каналов оперативной памяти | 6,4 ГБ/сек. |

| Возможность объединения в многопроцессорную систему с когерентной общей памятью | До 4 процессоров |

| Каналы межпроцессорного обмена | 3, дуплексные |

| Пропускная способность каждого канала межпроцессорного обмена | 4 ГБ/сек |

| Каналы ввода-вывода/RemoteDMA | 1, дуплексный |

| Пропускная способность канала ввода-вывода/RemoteDMA | 2 ГБ/сек |

| Совместимые СБИС южного моста | КПИ |

| Технологические характеристики микросхемы | |

| Напряжение питания | 1,0 В, 1,8 В, 2,5 В |

| Рабочий диапазон температуры среды | −40…+85 град. С |

| Потребляемая мощность | 15 Вт |

| Год начала производства | 2011 |

| Добавленные технологии | |

| Система команд | VIS1, VIS2 |

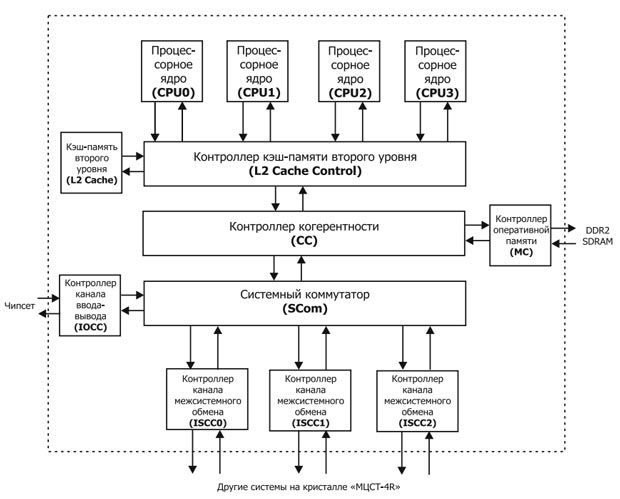

Структурная схема системы на кристалле МЦСТ-R1000

Микросхема 1891ВМ6Я содержит (см. рисунок):

Назначение основных функциональных модулей микропроцессора:

Процессорные ядра (CPU0…CPU3) реализуют 64-разрядную архитектуру SPARC v.9 и имеют суперскалярную организацию. Максимальный темп дешифрации команд в ядре – 2 команды за такт. Обмен с кэш-памятью второго уровня для каждого ядра процессора выполняется блоками по 32 байта и выполняется на рабочей частоте.

Кэш-память второго уровня (L2Cache) ёмкостью 2 Мбайт – общая для четырёх процессорных ядер. Организована в виде 8 колонок по 4096 строк, размер кэш-блока – 64 байта данных. Ассоциативность – 4, политика записи – write-back.

Контроллер когерентности (СС) обеспечивает согласованность данных в многопроцессорных системах и при операциях ввода-вывода.

Системный коммутатор (SCom) обеспечивает доступ в оперативную память процессорных ядер, контроллера IOCC и трёх контроллеров ISCC.

Контроллер памяти (MC) обеспечивает доступ к двум слотам оперативной памяти DDR2-800 с общим объёмом до 8 Гбайт. Обмен выполняется с темпом обмена до 6.4 Гбайт/с.

Контроллер канала ввода-вывода (IOCC) обеспечивает обмен с подсистемой ввода-вывода (контроллером «южного моста») или другими вычислительными комплексами.

Контроллеры каналов межсистемного обмена (ISCC0…ISCC2) обеспечивают связь с другими процессорами МЦСТ R1000. Каждый контроллер удалённого доступа имеет дуплексный байтовый LVDS-канал. Обмен выполняется по методу DDR на частоте 500 МГц. Суммарная пропускная способность контроллера – 4 Гбайт/с.

Различия между контроллерами IOCC и ISCC связаны в основном со спецификой пакетов данных и сигнальных сообщений, передаваемых в канале обмена. По каналу ввода-вывода выполняется передача данных для периферийных устройств (массивы данных или отдельные команды). По каналу межсистемного обмена осуществляется доступ в память к другим системам и от других систем на кристалле МЦСТ-R1000 в многопроцессорных системах с общей памятью.