# Look-ahead Sigma-Delta Modulation and its application to Super Audio CD

Erwin Janssen

The work described in this thesis has been carried out at the Philips Research Laboratories and NXP Semiconductors, Eindhoven, the Netherlands, as part of the Philips/NXP research program.

Janssen, E.

Look-ahead Sigma-Delta Modulation and its application to Super Audio CD

Proefschrift Technische Universiteit Eindhoven, 2010

Trefwoorden: 1-bit audio, digital-to-digital conversion, linearization, lookahead, noise shaping, sigma-delta modulation, signal processing

A catalogue record is available from the Eindhoven University of Technology Library ISBN: 978-90-386-2364-1

© E. Janssen 2010 All rights reserved. Reproduction in whole or in part is prohibited without the written consent of the copyright owner.

## Look-ahead Sigma-Delta Modulation and its application to Super Audio CD

PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de rector magnificus, prof.dr.ir. C.J. van Duijn, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op woensdag 1 december 2010 om 16.00 uur

door

Erwin Janssen

geboren te Ede

Dit proefschrift is goedgekeurd door promotor:

prof.dr.ir. A.H.M. van Roermund

Samenstelling promotiecommissie:

prof.dr.ir. A.H.M. van Roermund prof.dr.ir. A.C.P.M. Backx dr.ir. J.A. Hegt dr.ir. P.C.W. Sommen prof.dr.ir. B. Nauta prof.dr.ir. G. Gielen dr. D. Reefman dr.ir. L.J. Breems Technische Universiteit Eindhoven Technische Universiteit Eindhoven Technische Universiteit Eindhoven Technische Universiteit Eindhoven Universiteit Twente Katholieke Universiteit Leuven Philips Research NXP Semiconductors

# Contents

| Li       | st of | symbols and abbreviations                   | vii |

|----------|-------|---------------------------------------------|-----|

| 1        | Intr  | oduction                                    | 1   |

| _        | 1.1   | Motivation                                  | 2   |

|          | 1.2   | Aim of the thesis                           | 3   |

|          | 1.3   | Scope of the thesis                         | 4   |

|          | 1.4   | Organization of the thesis                  | 4   |

| <b>2</b> | Bas   | ics of sigma-delta modulation               | 7   |

|          | 2.1   | AD, DD, and DA Sigma-Delta conversion       | 11  |

|          |       | 2.1.1 AD conversion                         | 11  |

|          |       | 2.1.2 DD conversion                         | 12  |

|          |       | 2.1.3 DA conversion                         | 12  |

|          | 2.2   | Sigma-Delta structures                      | 13  |

|          | 2.3   | Linear modeling of an SDM                   | 16  |

|          | 2.4   | SDM performance indicators                  | 22  |

|          |       | 2.4.1 Generic converter performance         | 23  |

|          |       | 2.4.2 SDM specific functional performance   | 29  |

|          |       | 2.4.3 SDM specific implementation costs     | 34  |

|          |       | 2.4.4 Figure-Of-Merit of an SDM             | 36  |

| 3        | Tra   | nsient SDM performance                      | 39  |

|          | 3.1   | Measuring signal conversion quality         | 39  |

|          |       | 3.1.1 Steady-state                          | 39  |

|          |       | 3.1.2 Non-steady-state                      | 40  |

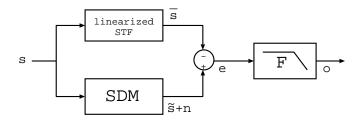

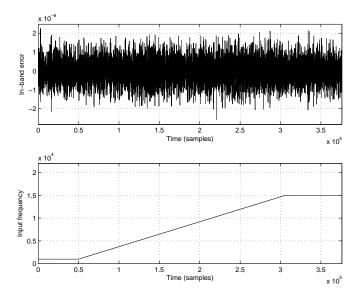

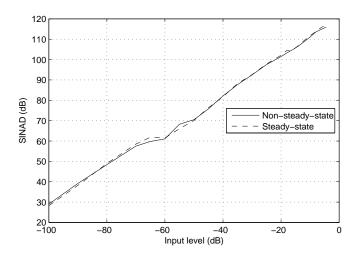

|          | 3.2   | Time domain SINAD measurement               | 41  |

|          | 3.3   | Steady-state SINAD measurement analysis     | 44  |

|          |       | 3.3.1 Obtaining the linearized STF          | 45  |

|          |       | 3.3.2 Time domain SINAD measurement         | 49  |

|          | 3.4   | Non-steady-state SINAD measurement analysis | 50  |

|          | 3.5   | Conclusions                                 | 52  |

| <b>4</b> | Noi  | se-shaj        | ping quantizer model                                 |   | <b>55</b>       |

|----------|------|----------------|------------------------------------------------------|---|-----------------|

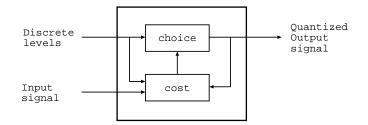

|          | 4.1  | Gener          | ic quantizer                                         |   | 55              |

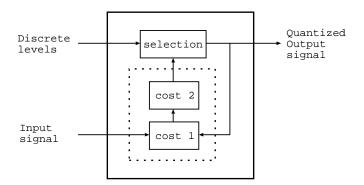

|          | 4.2  | Noise-         | shaping quantizer                                    |   | 57              |

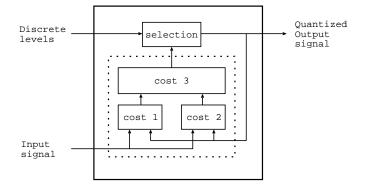

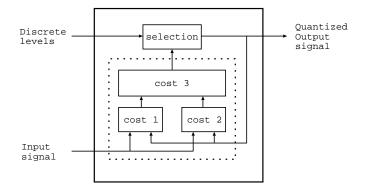

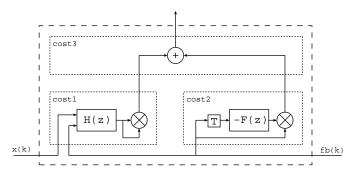

|          | 4.3  | Noise-         | shaping quantizer with multiple cost functions       |   | 59              |

|          | 4.4  | Specifi        | ic realization structures                            |   | 60              |

| 5        | Loo  | k-ahea         | d sigma-delta modulation                             |   | 63              |

|          | 5.1  |                | shaping quantizer with look-ahead                    |   | 63              |

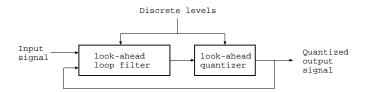

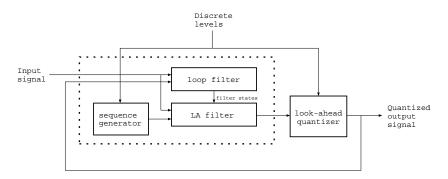

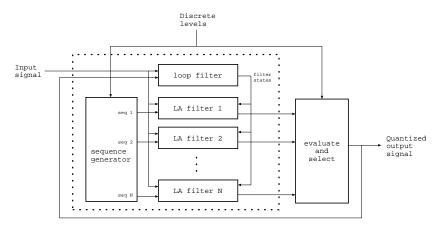

|          | 5.2  |                | ahead enabled SDM model                              |   | 65              |

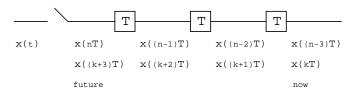

|          | 5.3  |                | ahead principle                                      |   | 67              |

|          | 0.0  | 5.3.1          | Quantizer cost function                              |   | 69              |

|          | 5.4  |                | ning information about the future                    |   | 70              |

|          | 0.1  | 5.4.1          | Approximated future input                            |   | 71              |

|          |      | 5.4.2          | Actual future input                                  |   | 71              |

|          | 5.5  |                | ook-ahead algorithm                                  |   | 72              |

|          | 5.6  |                | modeling of a look-ahead SDM                         |   | 75              |

|          | 0.0  | 5.6.1          | Boundary conditions and assumptions                  |   | 76              |

|          |      | 5.6.2          | Feed-forward look-ahead SDM                          |   | 78              |

|          |      | 5.6.2          | Feed-back look-ahead SDM                             |   | 80              |

|          | 5.7  | 0.0.0          | ts and disadvantages of look-ahead                   |   | 82              |

|          | 0.1  | 5.7.1          | Benefits                                             |   | 82              |

|          |      | 5.7.1<br>5.7.2 | Disadvantages                                        |   | 86              |

|          | 5.8  |                | ahead AD conversion                                  |   | 87              |

|          | 0.0  | 5.8.1          | Potential benefits and disadvantages of look-ahead   | • | 01              |

|          |      | 5.6.1          | in AD conversion                                     |   | 87              |

|          |      | 5.8.2          | Feasibility of a look-ahead ADC                      |   | 88              |

|          |      | 5.8.2          | Hybrid look-ahead ADC                                |   | 00<br>90        |

|          |      | 5.8.4          | Conclusion                                           |   | 90<br>92        |

|          | 5.9  |                | ahead DD conversion                                  |   | $\frac{92}{92}$ |

|          |      |                |                                                      |   | $\frac{92}{95}$ |

|          | 5.10 | Concit         | usions                                               | • | 90              |

| 6        | Red  | lucing         | the complexity of LA DD conversion                   |   | 97              |

|          | 6.1  | Full lo        | ook-ahead                                            |   | 97              |

|          |      | 6.1.1          | Complete response calculation with reuse of inter-   |   |                 |

|          |      |                | mediate results                                      |   | 98              |

|          |      | 6.1.2          | Select and continue with half of the solutions       |   | 98              |

|          |      | 6.1.3          | Linear decomposition of the filter response $\ldots$ |   | 99              |

|          |      | 6.1.4          | Conditional computation of the solutions $\ldots$ .  |   | 101             |

|          |      | 6.1.5          | Calculating multiple output symbols per step         |   | 101             |

|          |      | 6.1.6          | Summary                                              |   | 103             |

|          | 6.2  | Prune          | d look-ahead                                         |   | 104             |

|          |      | 6.2.1          | Motivation for pruning                               |   | 104             |

|          |      | 6.2.2          | Basic pruned look-ahead modulation                   |   |                 |

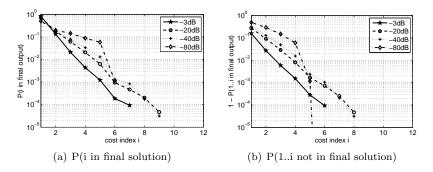

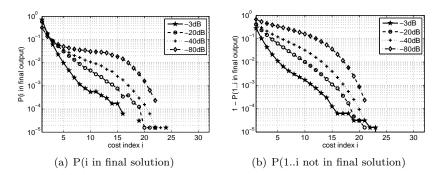

|   | 6.3        | 6.2.3       Pruned look-ahead modulation with reuse of results 108         6.2.4       Summary       120         Pruned look-ahead modulator realizations       120         6.3.1       Trellis sigma-delta modulation       121         6.2.2       Efficiency       121 |

|---|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |            | <ul><li>6.3.2 Efficient Trellis sigma-delta modulation 122</li><li>6.3.3 Pruned Tree sigma-delta modulation</li></ul>                                                                                                                                                     |

|   |            | 6.3.4 Pruned Tree sigma-delta modulation for SA-CD . 126                                                                                                                                                                                                                  |

|   | 6.4        | Conclusions                                                                                                                                                                                                                                                               |

|   | -          |                                                                                                                                                                                                                                                                           |

| 7 |            | llis sigma-delta modulation 12                                                                                                                                                                                                                                            |

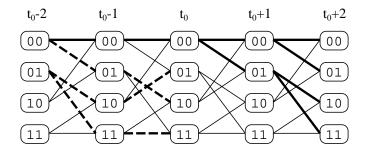

|   | 7.1        | Algorithm - Kato model                                                                                                                                                                                                                                                    |

|   |            | 7.1.1 Hidden Markov model                                                                                                                                                                                                                                                 |

|   | - 0        | 7.1.2 Algorithm steps                                                                                                                                                                                                                                                     |

|   | 7.2        | Algorithm - pruned look-ahead model                                                                                                                                                                                                                                       |

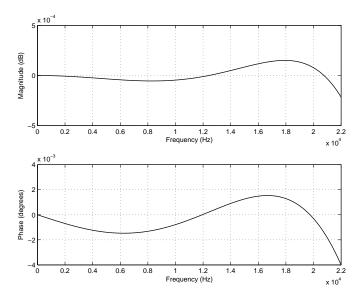

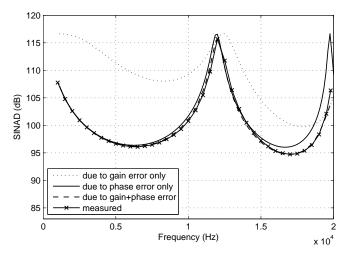

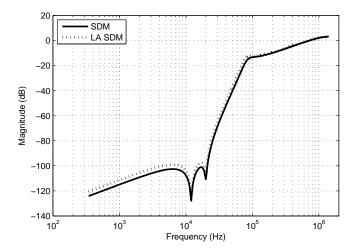

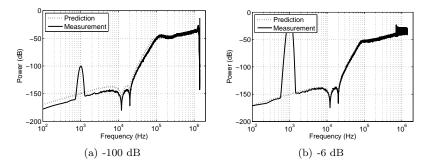

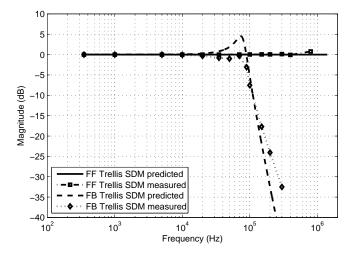

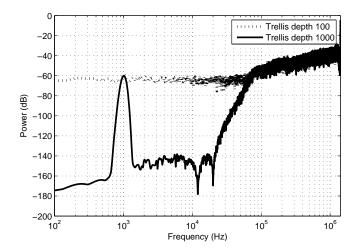

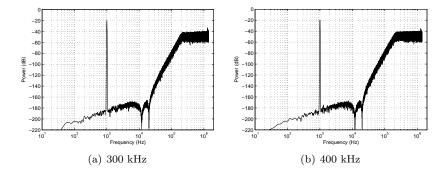

|   | 7.3        | Verification of the linearized NTF and STF                                                                                                                                                                                                                                |

|   |            | 7.3.1       NTF       139         7.3.2       STF       140                                                                                                                                                                                                               |

|   | 74         |                                                                                                                                                                                                                                                                           |

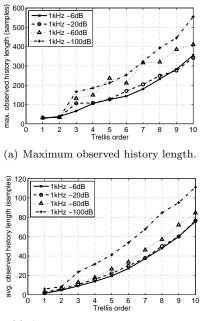

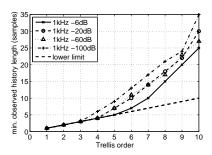

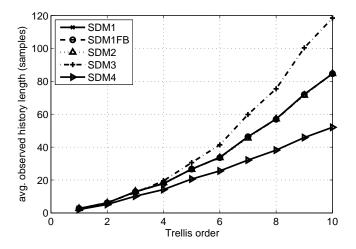

|   | 7.4        | Relation Trellis order and Trellis depth1427.4.1Simulation setup143                                                                                                                                                                                                       |

|   |            | 7.4.1 Simulation setup                                                                                                                                                                                                                                                    |

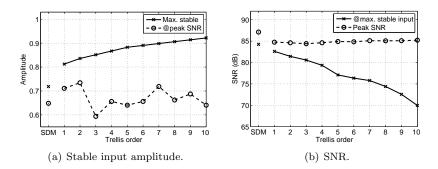

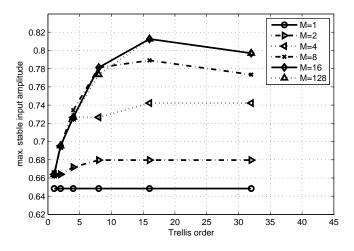

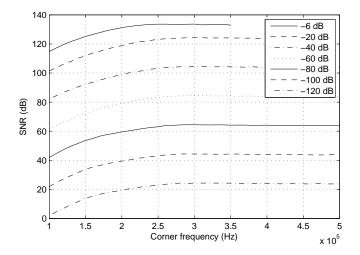

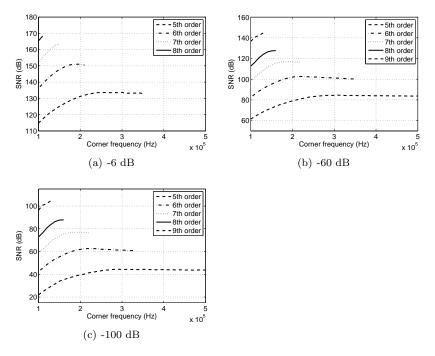

|   |            | the signal amplitude                                                                                                                                                                                                                                                      |

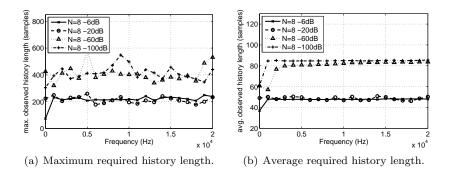

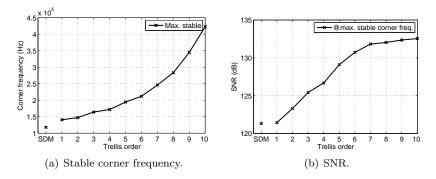

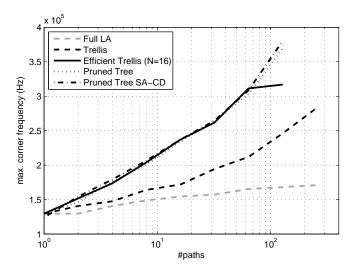

|   |            | 7.4.3 Trellis depth as a function of the signal frequency . 146                                                                                                                                                                                                           |

|   |            | 7.4.4 Trellis depth as a function of the loop-filter con-                                                                                                                                                                                                                 |

|   |            | figuration                                                                                                                                                                                                                                                                |

|   |            | 7.4.5 Summary                                                                                                                                                                                                                                                             |

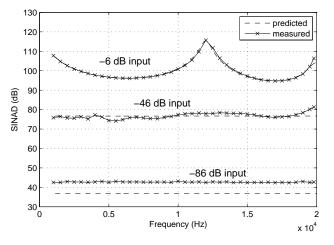

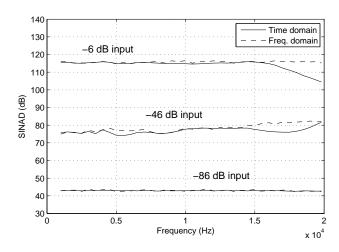

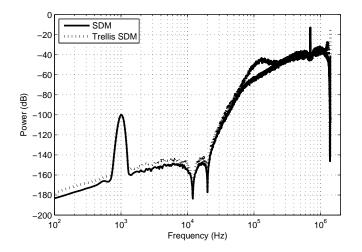

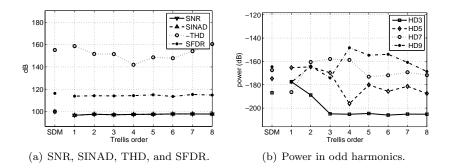

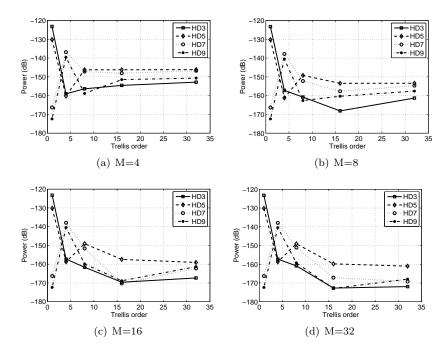

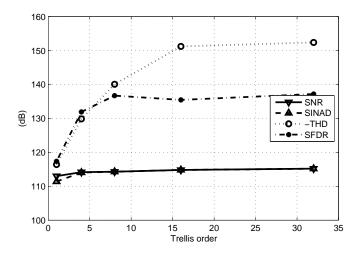

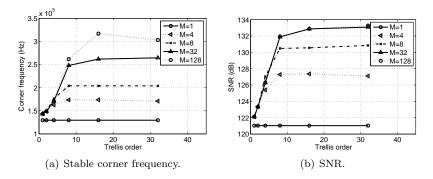

|   | 7.5        | Functional performance                                                                                                                                                                                                                                                    |

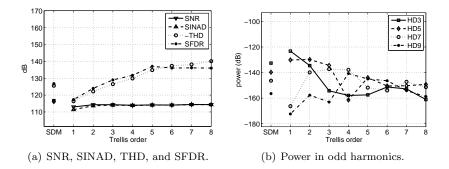

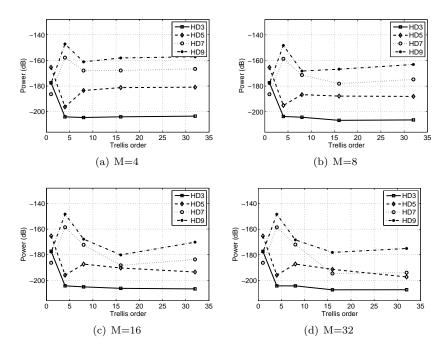

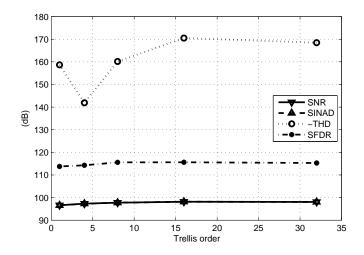

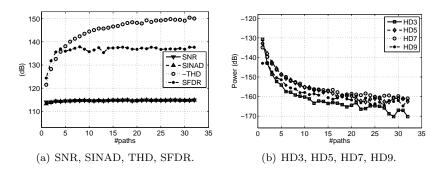

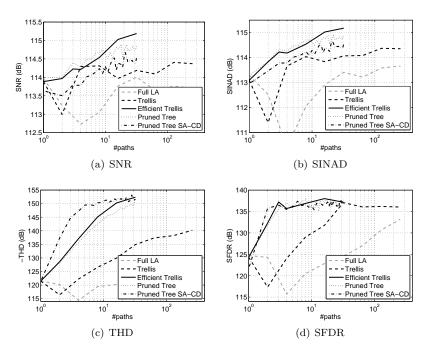

|   | 1.0        | 7.5.1 SNR, SINAD, THD and SFDR                                                                                                                                                                                                                                            |

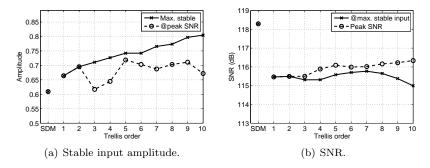

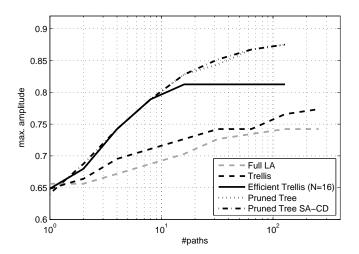

|   |            | 7.5.2 Converter stability                                                                                                                                                                                                                                                 |

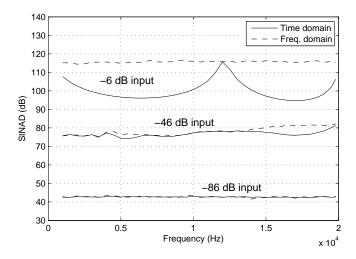

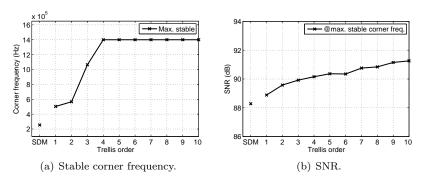

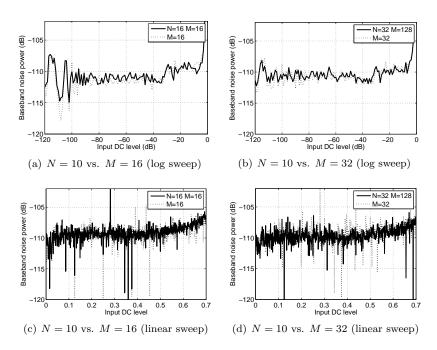

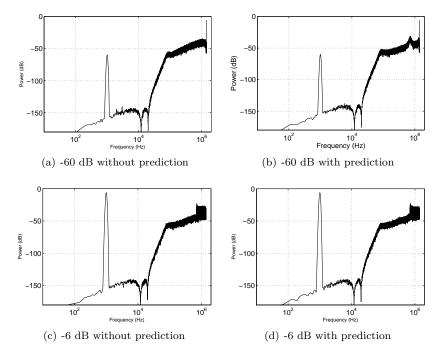

|   |            | 7.5.3 Noise modulation                                                                                                                                                                                                                                                    |

|   |            | 7.5.4 Summary                                                                                                                                                                                                                                                             |

|   | 7.6        | Implementation aspects                                                                                                                                                                                                                                                    |

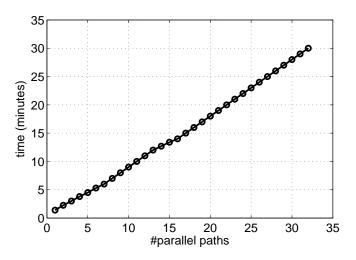

|   |            | 7.6.1 Required computational resources                                                                                                                                                                                                                                    |

|   |            | $7.6.2$ Look-ahead filter unit $\ldots \ldots \ldots$                                                                                                     |

|   |            | 7.6.3 Output symbol selection                                                                                                                                                                                                                                             |

|   | 7.7        | Conclusions                                                                                                                                                                                                                                                               |

| 0 | ъœ         |                                                                                                                                                                                                                                                                           |

| 8 |            | cient Trellis sigma-delta modulation 173                                                                                                                                                                                                                                  |

|   | 8.1<br>8.2 | Reducing the number of parallel paths                                                                                                                                                                                                                                     |

|   |            | Algorithm       176         Relation between N and M       178                                                                                                                                                                                                            |

|   | 8.3        |                                                                                                                                                                                                                                                                           |

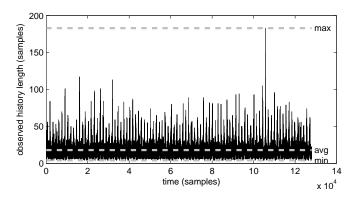

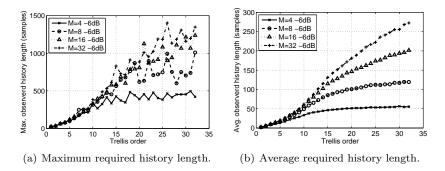

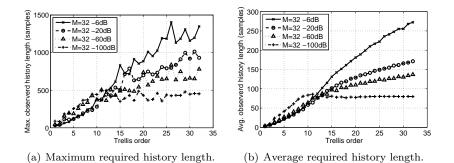

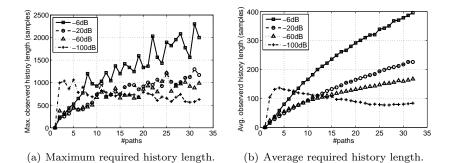

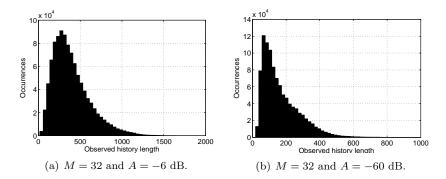

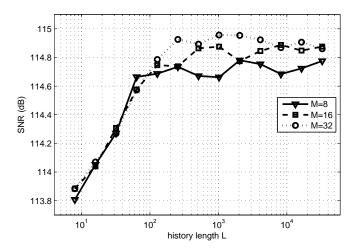

|   | 8.4<br>8.5 | Required history length                                                                                                                                                                                                                                                   |

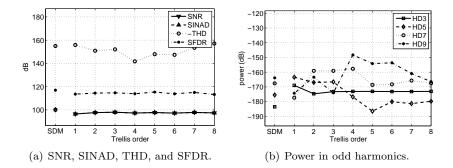

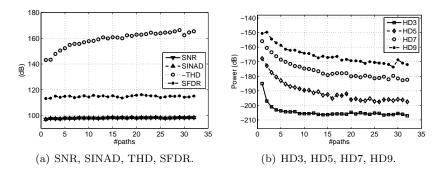

|   | 8.5        | Functional performance                                                                                                                                                                                                                                                    |

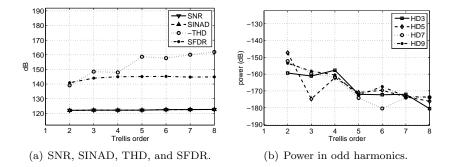

|   |            | 8.5.1 SNR, SINAD, THD and SFDR                                                                                                                                                                                                                                            |

|    |                                                                                    | 8.5.2 Converter stability                                                                                                                                                                                                                                                                                                                                                | 188                                                                                                                        |

|----|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

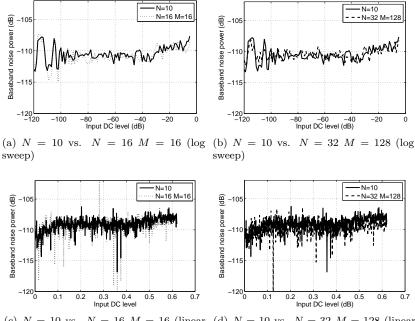

|    |                                                                                    | 8.5.3 Noise modulation                                                                                                                                                                                                                                                                                                                                                   | 189                                                                                                                        |

|    |                                                                                    | 8.5.4 Summary                                                                                                                                                                                                                                                                                                                                                            | 192                                                                                                                        |

|    | 8.6                                                                                | Implementation aspects                                                                                                                                                                                                                                                                                                                                                   | 194                                                                                                                        |

|    |                                                                                    | 8.6.1 Selection step                                                                                                                                                                                                                                                                                                                                                     | 194                                                                                                                        |

|    | 8.7                                                                                | Conclusions                                                                                                                                                                                                                                                                                                                                                              | 196                                                                                                                        |

| 9  | Pru                                                                                | ned Tree sigma-delta modulation                                                                                                                                                                                                                                                                                                                                          | 199                                                                                                                        |

|    | 9.1                                                                                | Removing the test for uniqueness                                                                                                                                                                                                                                                                                                                                         |                                                                                                                            |

|    | 9.2                                                                                | Algorithm                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                            |

|    |                                                                                    | 9.2.1 Initialization phase $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                         |                                                                                                                            |

|    |                                                                                    | 9.2.2 Operation phase                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                            |

|    | 9.3                                                                                | Required history length                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                            |

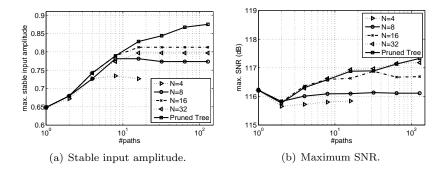

|    | 9.4                                                                                | Functional performance                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                            |

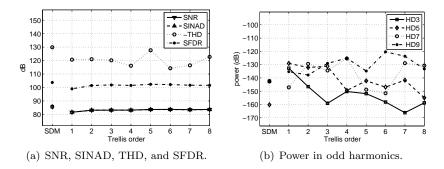

|    |                                                                                    | 9.4.1 SNR, SINAD, THD and SFDR                                                                                                                                                                                                                                                                                                                                           |                                                                                                                            |

|    |                                                                                    | 9.4.2 Converter stability $\ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                    | 210                                                                                                                        |

|    |                                                                                    | 9.4.3 Noise modulation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                             | -                                                                                                                          |

|    |                                                                                    | 9.4.4 Summary                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                            |

|    | 9.5                                                                                | Implementation aspects                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                            |

|    | 9.6                                                                                | Conclusions                                                                                                                                                                                                                                                                                                                                                              | 218                                                                                                                        |

| 10 | Dm                                                                                 | and There shows dollar and dollar for SA CD                                                                                                                                                                                                                                                                                                                              |                                                                                                                            |

|    |                                                                                    |                                                                                                                                                                                                                                                                                                                                                                          | ·)·)·2                                                                                                                     |

| 10 |                                                                                    | ned Tree sigma-delta modulation for SA-CD                                                                                                                                                                                                                                                                                                                                | <b>223</b>                                                                                                                 |

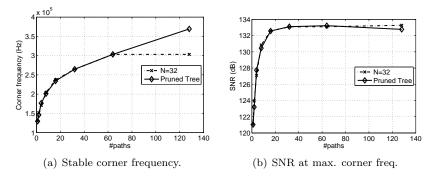

| 10 | 10.1                                                                               | Requirements of an SA-CD modulator                                                                                                                                                                                                                                                                                                                                       | 224                                                                                                                        |

| 10 | $\begin{array}{c} 10.1 \\ 10.2 \end{array}$                                        | Requirements of an SA-CD modulator                                                                                                                                                                                                                                                                                                                                       | 224<br>226                                                                                                                 |

| 10 | $\begin{array}{c} 10.1 \\ 10.2 \end{array}$                                        | Requirements of an SA-CD modulator                                                                                                                                                                                                                                                                                                                                       | 224<br>226<br>230                                                                                                          |

| 10 | $\begin{array}{c} 10.1 \\ 10.2 \end{array}$                                        | Requirements of an SA-CD modulator                                                                                                                                                                                                                                                                                                                                       | 224<br>226<br>230<br>231                                                                                                   |

| 10 | $\begin{array}{c} 10.1 \\ 10.2 \end{array}$                                        | Requirements of an SA-CD modulator                                                                                                                                                                                                                                                                                                                                       | 224<br>226<br>230<br>231<br>232                                                                                            |

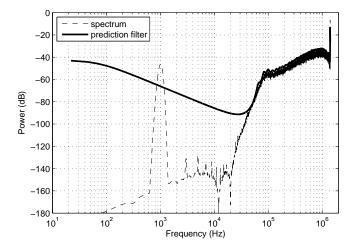

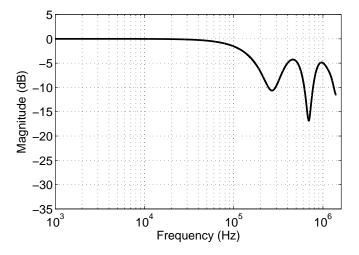

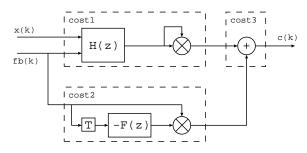

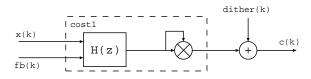

| 10 | 10.1<br>10.2<br>10.3                                                               | Requirements of an SA-CD modulatorSA-CD lossless data compressionDual optimization10.3.1 Predictor cost function10.3.2 Combining the cost functions10.3.3 Spectral shaping                                                                                                                                                                                               | 224<br>226<br>230<br>231<br>232<br>234                                                                                     |

| 10 | 10.1<br>10.2<br>10.3                                                               | Requirements of an SA-CD modulatorSA-CD lossless data compressionDual optimization10.3.1 Predictor cost function10.3.2 Combining the cost functions10.3.3 Spectral shapingAlgorithm                                                                                                                                                                                      | 224<br>226<br>230<br>231<br>232<br>234<br>237                                                                              |

| 10 | 10.1<br>10.2<br>10.3                                                               | Requirements of an SA-CD modulatorSA-CD lossless data compressionDual optimization10.3.1 Predictor cost function10.3.2 Combining the cost functions10.3.3 Spectral shapingAlgorithmFunctional performance                                                                                                                                                                | 224<br>226<br>230<br>231<br>232<br>234<br>237<br>240                                                                       |

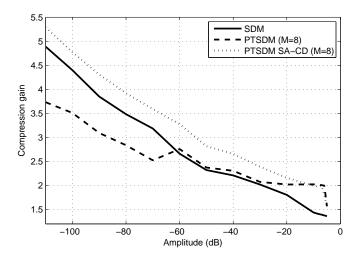

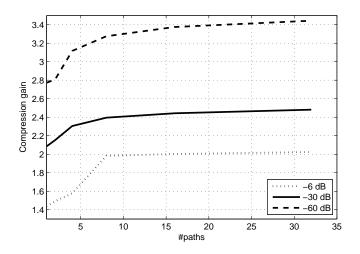

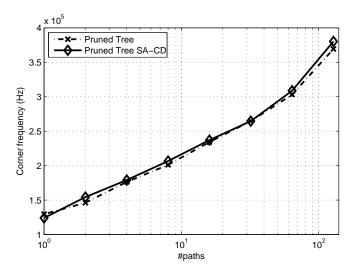

| 10 | 10.1<br>10.2<br>10.3                                                               | Requirements of an SA-CD modulatorSA-CD lossless data compressionDual optimization10.3.1 Predictor cost function10.3.2 Combining the cost functions10.3.3 Spectral shapingAlgorithmFunctional performance10.5.1 Lossless data compression                                                                                                                                | 224<br>226<br>230<br>231<br>232<br>234<br>237<br>240<br>240                                                                |

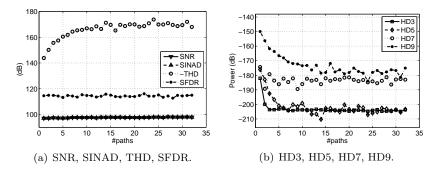

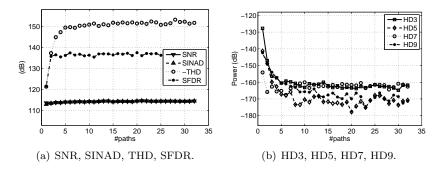

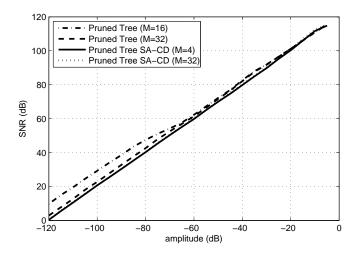

| 10 | 10.1<br>10.2<br>10.3                                                               | Requirements of an SA-CD modulatorSA-CD lossless data compressionDual optimization10.3.1 Predictor cost function10.3.2 Combining the cost functions10.3.3 Spectral shapingAlgorithmFunctional performance10.5.1 Lossless data compression10.5.2 SNR, SINAD, THD and SFDR                                                                                                 | 224<br>226<br>230<br>231<br>232<br>234<br>237<br>240<br>240<br>242                                                         |

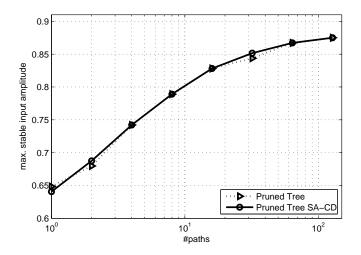

| 10 | 10.1<br>10.2<br>10.3                                                               | Requirements of an SA-CD modulatorSA-CD lossless data compressionDual optimization10.3.1 Predictor cost function10.3.2 Combining the cost functions10.3.3 Spectral shapingAlgorithmFunctional performance10.5.1 Lossless data compression10.5.2 SNR, SINAD, THD and SFDR10.5.3 Converter stability                                                                       | 224<br>226<br>230<br>231<br>232<br>234<br>237<br>240<br>240<br>242<br>245                                                  |

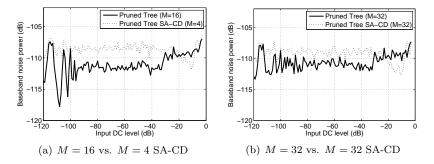

| 10 | 10.1<br>10.2<br>10.3                                                               | Requirements of an SA-CD modulatorSA-CD lossless data compressionDual optimization10.3.1 Predictor cost function10.3.2 Combining the cost functions10.3.3 Spectral shapingAlgorithm10.5.1 Lossless data compression10.5.2 SNR, SINAD, THD and SFDR10.5.3 Converter stability10.5.4 Noise modulation                                                                      | 224<br>226<br>230<br>231<br>232<br>234<br>237<br>240<br>240<br>242<br>245<br>245<br>247                                    |

| 10 | 10.1<br>10.2<br>10.3<br>10.4<br>10.5                                               | Requirements of an SA-CD modulatorSA-CD lossless data compressionDual optimization10.3.1 Predictor cost function10.3.2 Combining the cost functions10.3.3 Spectral shapingAlgorithmFunctional performance10.5.1 Lossless data compression10.5.2 SNR, SINAD, THD and SFDR10.5.3 Converter stability                                                                       | 224<br>226<br>230<br>231<br>232<br>234<br>237<br>240<br>240<br>242<br>245<br>247<br>249                                    |

| 10 | 10.1<br>10.2<br>10.3<br>10.4<br>10.5                                               | Requirements of an SA-CD modulatorSA-CD lossless data compressionDual optimization10.3.1 Predictor cost function10.3.2 Combining the cost functions10.3.3 Spectral shapingAlgorithmSubscription10.5.1 Lossless data compression10.5.2 SNR, SINAD, THD and SFDR10.5.3 Converter stability10.5.4 Noise modulation10.5.5 Summary                                            | 224<br>226<br>230<br>231<br>232<br>234<br>237<br>240<br>240<br>242<br>245<br>247<br>249<br>251                             |

|    | 10.1<br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>10.7<br><b>Con</b>                 | Requirements of an SA-CD modulator                                                                                                                                                                                                                                                                                                                                       | 224<br>226<br>230<br>231<br>232<br>234<br>237<br>240<br>240<br>242<br>245<br>247<br>249<br>251<br>252<br><b>255</b>        |

|    | 10.1<br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>10.7<br><b>Con</b>                 | Requirements of an SA-CD modulator                                                                                                                                                                                                                                                                                                                                       | 224<br>226<br>230<br>231<br>232<br>234<br>237<br>240<br>240<br>242<br>245<br>247<br>249<br>251<br>252<br><b>255</b>        |

|    | 10.1<br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>10.7<br><b>Con</b><br>11.1         | Requirements of an SA-CD modulatorSA-CD lossless data compressionDual optimization10.3.1 Predictor cost function10.3.2 Combining the cost functions10.3.3 Spectral shapingAlgorithmFunctional performance10.5.1 Lossless data compression10.5.2 SNR, SINAD, THD and SFDR10.5.3 Converter stability10.5.4 Noise modulation10.5.5 SummaryImplementation aspectsConclusions | 224<br>226<br>230<br>231<br>232<br>234<br>237<br>240<br>240<br>242<br>245<br>247<br>249<br>251<br>252<br><b>255</b>        |

|    | 10.1<br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>10.7<br><b>Com</b><br>11.1<br>11.2 | Requirements of an SA-CD modulator                                                                                                                                                                                                                                                                                                                                       | 224<br>226<br>230<br>231<br>232<br>234<br>237<br>240<br>240<br>242<br>245<br>247<br>249<br>251<br>255<br>255<br>255<br>257 |

| 11.3.2 Converter stability $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 26$                                                            | 65       |

|----------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 11.3.3 Noise modulation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 26$                                                        |          |

| 11.3.4 Lossless data compression                                                                                                                   |          |

| 11.3.5 Summary                                                                                                                                     | 74       |

| 11.4 Conclusions $\ldots \ldots 27$                                                 | 75       |

|                                                                                                                                                    | 79       |

| 12.1 Experiment 1                                                                                                                                  |          |

| 12.2 Experiment 2                                                                                                                                  |          |

| 12.3 Analysis                                                                                                                                      |          |

| 12.3.1 Second order filter stability                                                                                                               |          |

| 12.3.2 High order filter stability $\ldots \ldots \ldots 28$                                                                                       |          |

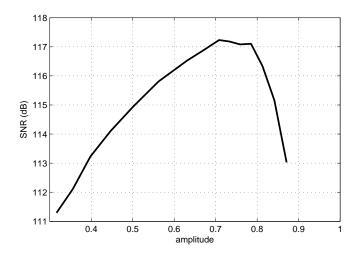

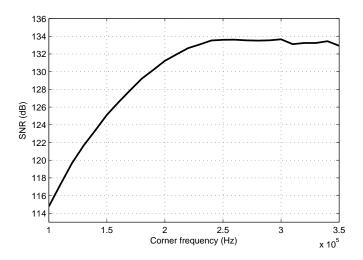

| 12.4 Obtaining the maximum SNR $\dots \dots \dots$ |          |

| 12.5 Theoretical maximum SNR                                                                                                                       |          |

| 12.6 Conclusions $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 29$                                                        | 93       |

| 13 General conclusions 29                                                                                                                          | 95       |

| A FFT calculations - coherent and power averaging 29                                                                                               | 97       |

| B Description of the used Sigma-Delta Modulators 30                                                                                                | 01       |

| References 30                                                                                                                                      | 03       |

|                                                                                                                                                    | ~~       |

| Original contributions 30                                                                                                                          | 09       |

|                                                                                                                                                    | 09<br>11 |

| List of publications 31                                                                                                                            |          |

| List of publications 31<br>Summary 31                                                                                                              | 11       |

| List of publications31Summary31Samenvatting31                                                                                                      | 11 $15$  |

# List of symbols and abbreviations

| $t_0$               | current time step                                            |

|---------------------|--------------------------------------------------------------|

| ĂC                  | alternating current                                          |

| AD                  | analog to digital                                            |

| ADC                 | analog to digital converter                                  |

| $\mathbf{C}$        | accumulated cost value or cost function                      |

| с                   | cost value                                                   |

| DA                  | digital to analog                                            |

| DAC                 | digital to analog converter                                  |

| dBFS                | decibels full scale                                          |

| DC                  | direct current, 0 Hz                                         |

| DD                  | digital to digital                                           |

| DDC                 | digital to digital converter                                 |

| DSD                 | Direct Stream Digital                                        |

| DSM                 | Delta-Sigma Modulator                                        |

| DST                 | Direct Stream Transfer                                       |

| ENOB                | effective number of bits                                     |

| ERBW                | effective resolution bandwidth                               |

| ETSDM               | Efficient Trellis SDM                                        |

| $\operatorname{FB}$ | feed-back                                                    |

| $\mathbf{FF}$       | feed-forward                                                 |

| FoM                 | figure of merit                                              |

| $\mathbf{Fs}$       | sampling rate                                                |

| HD                  | harmonic distortion                                          |

| HMM                 | hidden Markov model                                          |

| $\mathbf{L}$        | the number of bits latency, or the trace-back depth in bits, |

|                     | for all the different look-ahead algorithms                  |

| LA                  | look-ahead                                                   |

| LASDM               | look-ahead SDM                                               |

| Μ                   | the number of parallel paths in the Pruned Tree sigma-       |

|                     |                                                              |

|                      | delta modulation algorithm (for SA-CD)                    |

|----------------------|-----------------------------------------------------------|

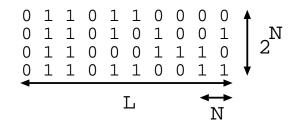

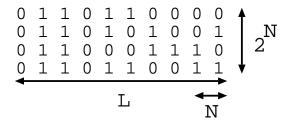

| Ν                    | the number of bits over which uniqueness of the parallel  |

|                      | solutions is determined in the (Efficient) Trellis sigma- |

|                      | delta modulation algorithm. Also determines the number    |

|                      | of parallel solutions $(2^N)$ for the Trellis algorithm.  |

| NS                   | noise-shaping                                             |

| NTF                  | noise transfer function                                   |

| OSR                  | oversampling ratio                                        |

| $\mathbf{PCM}$       | pulse-code modulated                                      |

| PDF                  | probability density function                              |

| PDM                  | pulse density modulation                                  |

| PTSDM                | Pruned Tree SDM                                           |

| $\mathbf{PWM}$       | pulse width modulation                                    |

| SA-CD                | Super Audio CD                                            |

| SD                   | Sigma-Delta                                               |

| SDM                  | Sigma-Delta Modulator                                     |

| SFDR                 | spurious free dynamic range                               |

| SINAD                | signal to noise and distortion ratio                      |

| SNDR                 | SINAD                                                     |

| $\operatorname{SNR}$ | signal to noise ratio                                     |

| $\operatorname{STF}$ | signal transfer function                                  |

| TD                   | time domain                                               |

| THD                  | total harmonic distortion                                 |

| TSDM                 | Trellis SDM                                               |

## Chapter 1

## Introduction

In March 1999 the Super Audio Compact Disc (Super Audio CD, SA-CD), the successor of the normal audio CD, was presented to the world. This new audio carrier, conceived by Philips and Sony, makes use of a radically new way to store and reproduce audio signals. Instead of working with the traditional 44.1 kHz sampling rate and 16-bit pulse-code modulated (PCM) signals, a 2.8 MHz 1-bit format is used to store the audio signal. The new format is marketed to deliver a signal-to-noise ratio (SNR) of 120 dB and a signal bandwidth of 90 kHz, as opposed to an SNR of 96 dB and a bandwidth of 20 kHz for the normal audio CD. The decision for this alternate encoding format was made years earlier, when 1-bit Analog-to-Digital (AD) audio Sigma-Delta (SD) converters were still delivering the highest signal conversion quality. In fact, virtually all of the high quality AD and digital-to-analog (DA) converters that were used at that time for the generation and reproduction of CD quality PCM audio were based on 1-bit converters. It was reasoned that a higher audio quality could be obtained by removing the decimation and interpolation filters that performed the conversion from 1-bit to PCM and vice versa, and by storing the 1-bit signal from the Sigma-Delta Modulator (SDM) directly on the disc.

Although the idea of storing the 1-bit SDM output signal directly on the disc sounds very reasonable, in practice things work differently, and the original recorded signal is never stored directly on a disc. As a result, there is a clear need for high quality digital 1-bit Sigma-Delta Modulators that generate bitstreams that have a high lossless compression gain, as will be explained in the next section. After the motivation for the work, the aims and the scope of the thesis are presented. Finally, a short description of the contents of each chapter of the thesis is given.

## 1.1 Motivation

In the process of recording an SA-CD, typically, a number of recordings of the same performance are made, and at a later stage in the studio those recordings are edited and processed, e.g. removal of coughs from an audience or the equalization of the audio levels, until the desired sound quality is obtained. This process of editing and processing can only be performed on multi-bit (PCM) signals, and only once all this work is done the 1-bit signal that will be stored on the SA-CD disc will be generated. Thus, if it is assumed that all the digital processing on the audio signal is without any loss of the signal quality, the final signal quality of the 1-bit signal that is stored on the disc is determined by the initial analog-to-digital conversion and the final digital-to-digital (DD) conversion.

Nowadays, the highest quality analog-to-digital conversion for audio applications is obtained with a multi-bit SDM. Such a converter can deliver a very high SNR and very low distortion levels. From the output of the SDM a PCM signal is generated, but now with a higher resolution and much higher sampling rate than what is used for CD. After all the processing on the multi-bit signal is performed, the final 1-bit signal is generated. Traditionally, this is done with a digital 1-bit SDM. However, with a normal SDM it is not trivial to generate a 1-bit signal with the desired ultra-high quality under all signal conditions. For example, for extremely high signal levels a 1-bit SDM can generate significant distortion, especially if the modulator is designed to deliver a very high SNR for normal signal levels. Besides this potential signal quality issue there is a much bigger issue that, with traditional sigma-delta modulation approaches, can not be solved without jeopardizing the signal quality: the risk of not realizing a long enough playback duration.

The SA-CD standard supports, in addition to a normal stereo recording, also the possibility to store a multi-channel version of the same recording. In order to fit all the data on the 4.7 gigabyte disc and obtain a playback duration of at least 74 minutes, the standard playback duration of the normal audio CD, lossless data compression is applied to the 1-bit audio signal. Only if the compression gain, the ratio that indicates the amount of data size reduction, is high enough it will be possible to obtain the required 74 minutes of playback time. Since the data compression algorithm is lossless, the compression gain depends on the redundancy in the 1-bit encoded audio signal, and this can only be influenced with the SDM design. However, the only solution to increase the redundancy is to reduce the signal conversion quality of the SDM, and since SA-CD is about delivering high audio quality this is not an acceptable solution.

From the above it is clear that there is a strong motivation to realize a 1-bit digital sigma-delta modulation solution that is able to realize a very high signal conversion quality and that is simultaneously able to generate bitstreams that are compatible with the SA-CD lossless data compression algorithm. As demonstrated by Kato in [37,38] the use of a look-ahead modulator instead of a normal SDM can bring significant improvements to the signal conversion quality. Although the computational load of his solution is too large for the approach to be practically usable, it does provide a good starting point for the exploration of alternative look-ahead approaches that are able to improve the signal conversion quality at a reasonable computational cost.

## 1.2 Aim of the thesis

The aim of this thesis is to expand and improve upon the existing knowledge on discrete-time 1-bit look-ahead sigma-delta modulation in general, and to come to a solution for the above mentioned specific issues arising from 1-bit sigma-delta modulation for SA-CD.

In order to achieve this objective an analysis is made of the possibilities for improving the performance of digital noise shaping look-ahead solutions. In this context "performance" has a broad definition and encompasses the standard signal-to-noise ratio and linearity performance indicators, the 1-bit SDM specific measures of stability and noise modulation, and also the computational load associated with a look-ahead algorithm. In the specific case of a look-ahead modulator for SA-CD also the lossless compression gain that is obtained on the output bitstream is evaluated.

On the basis of the insights obtained from the analysis, several novel generic 1-bit look-ahead solutions that improve upon the state-of-the-art will be derived and their performance will be evaluated and compared. Finally, all the insights are combined with the knowledge of the SA-CD lossless data compression algorithm to come to a specifically for SA-CD optimized look-ahead design.

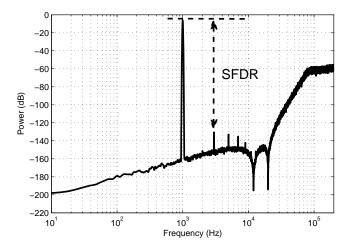

## 1.3 Scope of the thesis

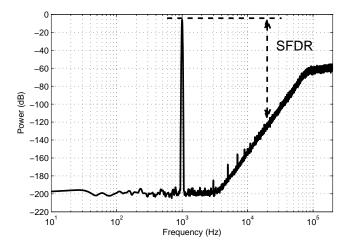

Almost all of the work described in this thesis has a general focus on (digital) 1-bit look-ahead sigma-delta modulation, and is independent of the sampling rate and the loop filter type of the converter. However, since the possibilities of look-ahead modulation are investigated with a Super Audio CD application in mind, the SDM design parameters used throughout the work are selected in line with the Super Audio CD standard. This translates to a sampling rate for the studied Sigma-Delta Modulators of 64.44.1 kHz, approximately 2.8 MHz, and the use of interpolative (low-pass) loop filters. The SNR, the signal-to-noise-anddistortion ratio (SINAD), the total harmonic distortion (THD), and the spurious free dynamic range (SFDR), are always evaluated over the audio bandwidth of 20 kHz. Besides these SA-CD specific parameters no use is made of any SA-CD specific nomenclature, except for chapter 10 where a minimal amount of usage can not be avoided. All the demonstrated SDM implementations have been realized in software, i.e. written in ANSI C, and make use of floating point arithmetic. Only limited attention is paid to the challenges of realizing a hardware solution, since in the context of Super Audio CD the primary intended use is in a software application.

## **1.4** Organization of the thesis

In chapter 2, a basic introduction to sigma-delta modulation and the performance evaluation of Sigma-Delta Modulators is given. Readers familiar with traditional sigma-delta modulation for AD and DD conversion and the possible artifacts resulting from 1-bit sigma-delta modulation can skip this chapter and immediately continue with chapter 3.

Traditionally, signal conversion quality is characterized with steady-state signals. In the case of a linear data converter this procedure will also give the performance for non-steady-state signals. However, since a 1-bit SDM is a non-linear data converter, it is not guaranteed that the steady-state performance is representative for non-steady-state signals. In chapter 3 this potential discrepancy is investigated.

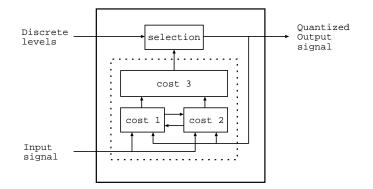

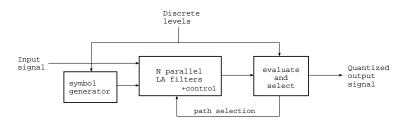

In chapter 4, a generic model of a noise-shaping quantizer is derived. This model is subsequently used in chapter 5 to come to a noise-shaping quantizer model for a look-ahead converter. Next, the main look-ahead principles are introduced, accompanied with an analysis of the benefits and disadvantages. The basic full look-ahead algorithm is presented, and an analysis is made of the possibilities for realizing a look-ahead enabled AD converter. Although this idea is rejected, it is clear that large benefits can be expected from look-ahead based DD conversion, but only if an approach with a reduced computational load can be realized.

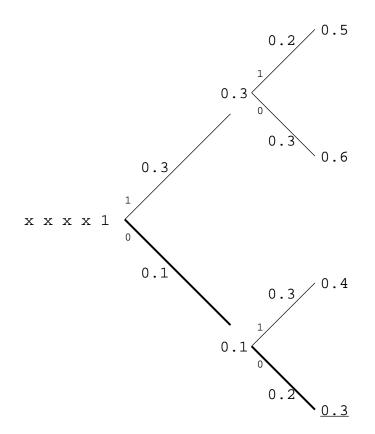

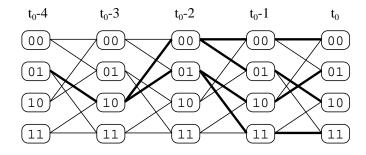

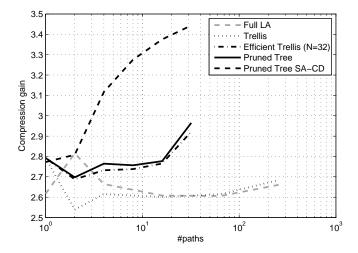

The possibilities for reducing the computational load of the full lookahead algorithm for DD conversion are investigated in chapter 6. Since the obtainable reduction is rather limited, an alternative approach, i.e. pruning of the solution space, is investigated. It is concluded that, with a proper pruning algorithm, it should be possible to realize solutions that result in large computational savings and that have a limited impact on the obtainable signal conversion performance. Therefore, the next chapters focus on pruned look-ahead algorithms.

In chapter 7, an analysis is made of the Trellis sigma-delta modulation algorithm by Kato. An improvement of the signal conversion quality, compared to a normal SDM, is realized but at a very large computational cost.

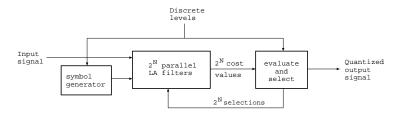

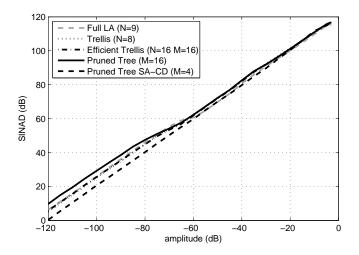

Further analysis of the Trellis sigma-delta modulation algorithm in chapter 8 reveals that only a fraction of all the parallel solutions contributes to the final output. The Efficient Trellis sigma-delta modulation algorithm makes use of this observation and prunes the solution space further, thereby enabling a larger pruned look-ahead depth that results in an improvement of the signal conversion quality, as well as a reduction in the computational load.

In chapter 9, the Pruned Tree sigma-delta modulation algorithm, that is an improvement over the Efficient Trellis sigma-delta modulation algorithm, is discussed. The pruning criteria that is applied in the Efficient Trellis sigma-delta modulation algorithm is effective for reducing the number of parallel solutions, but also adds a significant computational overhead to the algorithm. By changing the initial conditions of the look-ahead modulator the pruning criteria can be relaxed, which results in a computationally more efficient solution that, typically, delivers performance that is on par with that of the Efficient Trellis sigma-delta modulation algorithm, but that is sometimes even better.

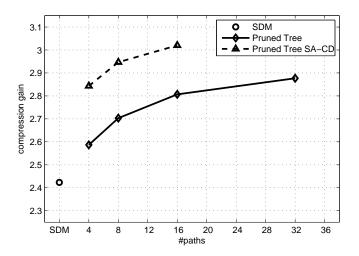

In the Pruned Tree sigma-delta modulation algorithm for SA-CD, described in chapter 10, a cost function is added to the original Pruned Tree sigma-delta modulation algorithm that reflects the predictability of the output bitstream. This addition results in a dual optimization that takes both the signal quality into account and improves the lossless data compression gain of the output signal.

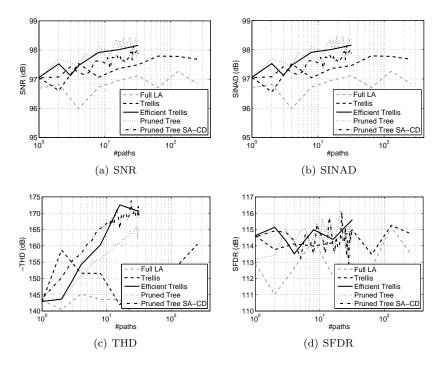

In chapter 11, a comparison is made between the various look-ahead

techniques that are detailed in the previous chapters. This comparison includes an analysis of the algorithmic differences, and a comparison of the functional performance.

In the previous chapters it was found that there appears to be a limit on the SNR that can be achieved with a fifth order 1-bit SDM. In chapter 12 this phenomenon is analyzed in detail and new results on the limits of 1-bit noise shaping are presented.

Finally, in chapter 13 the general conclusions on the work described in this thesis are presented.

## Chapter 2

# Basics of sigma-delta modulation

The principle of sigma-delta modulation, although widely used nowadays, was developed over a time span of more than 25 years. Initially the concept of oversampling and noise shaping was not known and the search for an efficient technique for transmitting voice signals digitally resulted in the Delta Modulator. Delta modulation was independently invented at the ITT Laboratories by Deloraine et. al [12,13] the Philips Research Laboratories by de Jager [11], and at Bell Telephone Labs [9] by Cutler. In 1954 the concept of oversampling and noise shaping was introduced and patented by Cutler [10]. His objective was not to reduce the data rate of the signal to transmit as in earlier published work, but to achieve a higher signal-to-noise ratio in a limited frequency band. All the elements of modern sigma-delta modulation are present in his invention, except for the digital decimation filter required for obtaining a Nyquist rate signal. The name Delta-Sigma Modulator (DSM) was finally introduced in 1962 by Inose et al. [26, 27] in their papers discussing 1-bit converters. By 1969 the realization of a digital decimation filter was feasible and described in a publication by Goodman [17]. In 1974 Candy published the first complete multi-bit Sigma-Delta Modulator (SDM) in [7]. Around the same time the name SDM was introduced as an alternative for Delta-Sigma Modulator and since then both names are in use. In this thesis the oversampled noise-shaping structure will be referred to as SDM. According to the author SDM is the more appropriate name since the integration or summing (the sigma) is over the difference (the delta).

In the 70's, because of the initially limited performance of Sigma-Delta

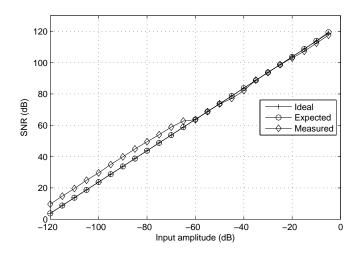

Modulators, their main use was in encoding low frequency audio signals (analog-to-digital conversion) using a 1-bit quantizer and a first or a second order loop filter. The creation of black and white images for print from a gray scale input was another application where Sigma-Delta noise-shaping techniques were used (digital-to-digital conversion). Since then a lot of research on improving SDM performance has been performed and great improvements have been realized. Nowadays top of the line SDM based analog-to-digital converters (ADCs) use a multibit quantizer and a high-order loop filter and are capable of converting 10's of MHz of bandwidth with high dynamic range. Because of high power efficiency, Sigma-Delta based analog-to-digital converters are used in the radio of mobile telephones. Another example of the efficient use of sigma-delta modulation techniques is the Super Audio CD format which uses a 64 times oversampled 1-bit signal for delivering a 120 dB signal-to-noise ratio (SNR) over the 0-20 kHz band. In this specific example the decimation filter is omitted and the oversampled signal is directly stored as to minimize signal operations and therefore maximize the signal quality. An omnipresent example of sigma-delta modulation in digital-to-analog conversion can be found in portable audio playback devices, e.g. IPOD and MP3 players. The audio digital-toanalog converter (DAC) in these devices realizes its performance using noise shaping (NS) and pulse-width-modulation (PWM) or pulsedensity-modulation (PDM) techniques. These PWM/PDM signals are typically generated using a (modified) digital SDM.

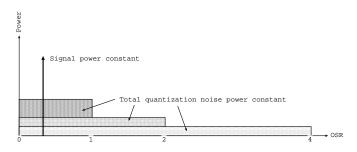

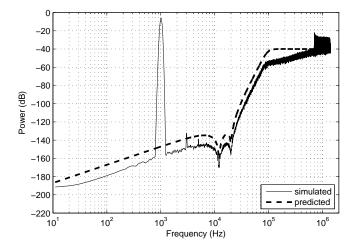

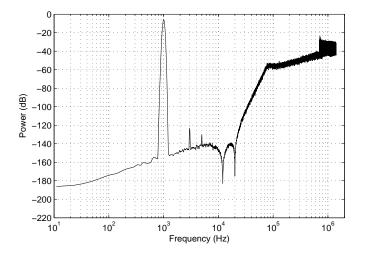

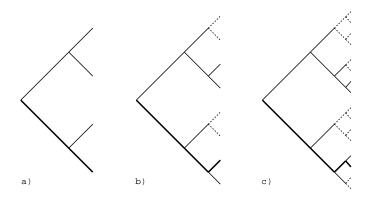

Although all these SDM solutions are optimized for a certain application and context, they still share the same underlying basic principles of oversampling and noise shaping. Oversampling is the process of taking more samples per second than required on the basis of the Nyquist-Shannon criterion. By changing the sampling rate the signal power and total quantization noise power is not affected. Therefore, the signal to quantization noise ratio is not changed. However, the quantization noise is spread over a larger frequency range, reducing the spectral density of the quantization noise. If now only the original Nyquist band is considered, the quantization noise power is reduced by 3 dB for every doubling of the oversampling ratio and the signal to quantization noise ratio is improved accordingly. This effect is illustrated in fig. 2.1 for an oversampling ratio (OSR) of 1, 2, and 4 times.

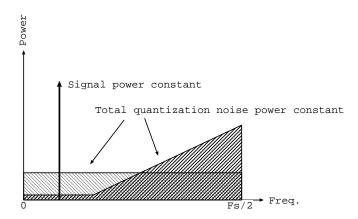

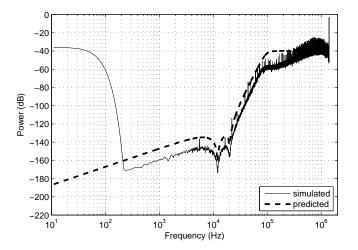

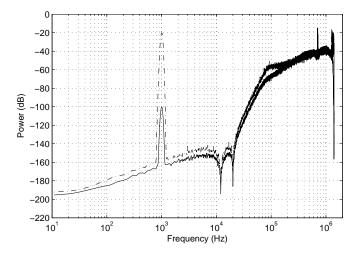

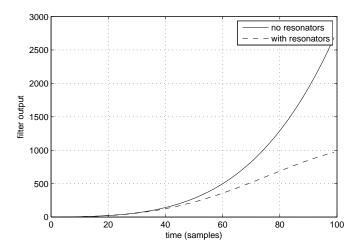

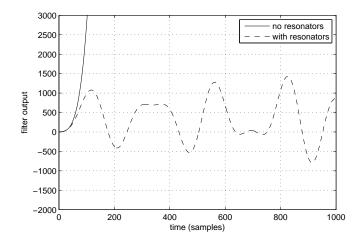

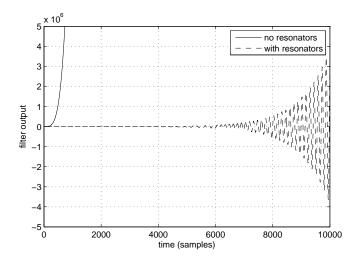

Noise shaping is applied as a second step to improve the signal to quantization noise ratio. In this process the frequency distribution of the quantization noise is altered such that the quantization noise density reduces in the signal band. As a result the noise density increases at other frequencies where the noise is less harmful. This effect is depic-

Figure 2.1: Oversampling does not affect the signal power or total quantization noise power but reduces the noise spectral density.

ted in fig. 2.2, where low frequency noise is pushed to high frequencies. The amount of quantization noise is not changed by this process but the signal to noise ratio is increased in the low frequency area of the spectrum. In an SDM the techniques of oversampling and noise shaping are combined, resulting in an increased efficiency since now the quantization noise can be pushed to frequencies far from the signal band.

Figure 2.2: Low frequency noise is pushed to high frequencies by noise shaping.

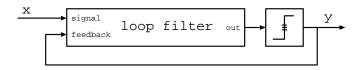

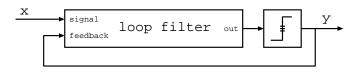

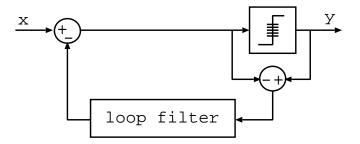

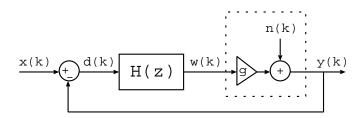

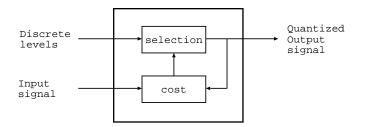

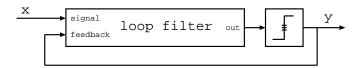

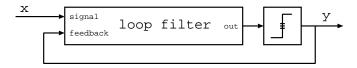

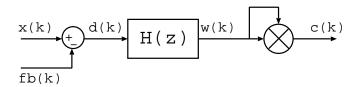

All SDM structures realize the shaping of noise with an error minimizing feedback loop in which the input signal x is compared with the quantized output signal y, as depicted in fig. 2.3. The difference between these two signals is frequency weighed with the loop filter. Differences between the

input and output that fall in the signal band are passed to the output without attenuation, out-of-band differences are suppressed by the filter. The result of the weighing is passed to the quantizer, which generates the next output value y. The output y is also fed back to the input, to be used in the next comparison. The result of this strategy is a close match of input signal and quantized output in the pass-band of the filter, and shaping of the quantization errors such that those fall outside the signal band.

Figure 2.3: Generic model of the Sigma-Delta noise-shaping loop, consisting of 2-input loop filter and quantizer.

In sec. 2.1 the noise-shaping loop in data converters will be examined in detail, revealing that in reality only analog-to-digital (AD) and digitalto-digital (DD) noise shaping conversion exists. Over the last decennia a great variety of noise-shaping loops have been developed, but all originate from a minimal number of fundamental approaches. The most commonly used configurations are discussed in sec. 2.2. During the design phase of an SDM the noise-shaping transfer function is typically evaluated using a linear model. In reality, especially for a 1-bit quantizer, the noise transfer is highly non-linear and large differences between predicted and actual realized transfer can occur. In sec. 2.3 the linear modeling of an SDM is examined and it will be shown that simulations instead of calculations are required for evaluating SDM performance. Several criteria exist for evaluating the performance of an SDM. The criteria can be differentiated between those that are generic and are used for characterizing data converters in general, and those that are only applicable for Sigma-Delta converters. Both types are discussed in sec. 2.4.

## 2.1 AD, DD, and DA Sigma-Delta conversion

#### 2.1.1 AD conversion

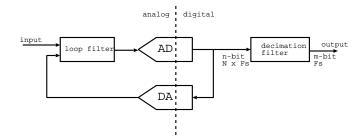

The most well-known form of sigma-delta modulation is analog-to-digital conversion. In fig. 2.4 the main building blocks of a generic Sigma-Delta ADC are shown. In the figure the analog and digital domains are indicated as well. The analog signal that will be converted, as well as the DAC feedback signal, enter the analog loop filter at the left side of the figure. The output of the loop filter is converted to an n-bit digital signal by the quantizer (ADC). This n-bit digital signal is passed to a digital decimation filter and to the feedback DAC. The decimation filter removes the out-of-band quantization noise, thereby converting the high rate low resolution signal to a high resolution low rate signal. The feedback DAC performs the inverse function of the ADC (quantizer) and converts the n-bit digital code to an analog voltage or current, closing the Sigma-Delta loop.

Figure 2.4: Main building blocks of a Sigma-Delta analog-to-digital converter.

Several different types of analog Sigma-Delta Modulators exist, varying in for example the way the loop filter is functioning (e.g. continuous time or discrete time) or how the DAC is constructed (e.g. switched capacitor or resistor based). Independent of these details, in all structures the use of a low resolution ADC and DAC is key. The coarse quantization results in a large amount of quantization noise which is pushed out of band by the loop filter. The number of bits used in the ADC and DAC is typically in the range 1-5. A 1-bit quantizer is easier to build than a 5-bit quantizer, requires less area and power, and is intrinsically linear, but has the disadvantage that less efficient noise shaping can be realized and that a higher oversampling ratio is required to compensate for this. The final Sigma-Delta output, i.e. at the output of the decimation filter, will be an m-bit word where m can be as high as 24. The number of bits is independent on the number of bits used in the internal ADC and DAC. Sometimes only the part before the decimation filter is considered in discussions about Sigma-Delta Modulators.

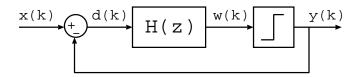

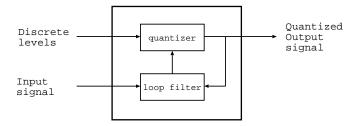

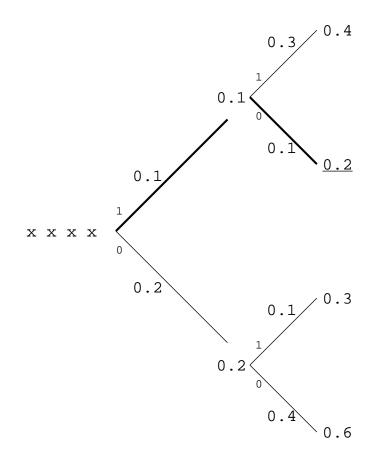

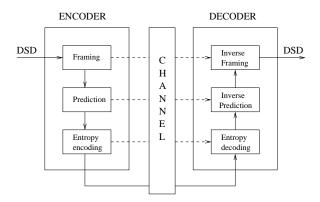

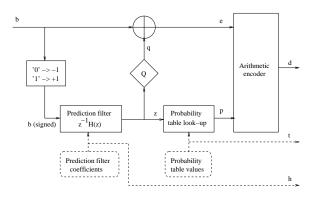

### 2.1.2 DD conversion

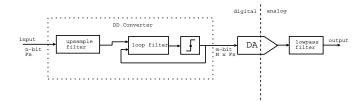

In a digital-to-digital Sigma-Delta converter an n-bit digital input is converted to an m-bit digital output, where n is larger than m. The sampling rate of the signal is increased during this process in order to generate additional spectral space for the quantization noise. The main building blocks of a generic DD SDM are shown in fig. 2.5. The n-bit signal is first upsampled from Fs to  $N \ge Fs$  in the upsampling filter. The resulting signal is passed to the actual SDM loop. This loop is very similar to the one in fig. 2.4, except that now everything is in the digital domain. The ADC and DAC combination is replaced by a single quantizer which takes the many-bit loop-filter output and generates a lower-bit word. Since everything is operating in the digital domain no DAC is required and the m-bit word can directly be used as feedback value. The noise-shaped m-bit signal is the final Sigma-Delta output. This m-bit signal is often passed to a DA converter, resulting in a Sigma-Delta DAC. In the case of audio encoding for Super Audio CD the 1-bit output is the final goal of the processing and is directly recorded on disc.

Figure 2.5: Main building blocks of a Sigma-Delta digital-to-digital converter.

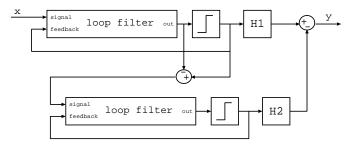

#### 2.1.3 DA conversion

A Sigma-Delta based DA converter realizes a high SNR with the use of a DAC with few quantization levels and noise-shaping techniques. In the digital domain the input signal to the DAC is shaped, such that the quantization noise of the DAC is moved to high frequencies. In the analog domain a passive low-pass filter removes the quantization noise, resulting in a clean baseband signal. The structure of a Sigma-Delta DAC is, except for some special PWM systems, a feed-forward solution, i.e. there is no feedback from the analog output into the noise-shaping filter. Because the noise-shaping feedback signal is not crossing the analog-digital boundary, the name Sigma-Delta DAC is confusing and misleading. A Sigma-Delta DAC is the combination of a DD converter and a high-speed few-bit DAC. In fig. 2.6 the complete Sigma-Delta DAC structure is shown. The digital n-bit input signal is passed to a DD converter which upsamples the input to  $N \ge Fs$  before an all digital SDM reduces the word-length. The noise-shaped m-bit signal is passed to the m-bit DAC which converts the digital signal to the analog domain. Finally the analog signal is filtered to remove the out-of-band quantization noise.

Figure 2.6: Main building blocks of a Sigma-Delta digital-to-analog converter.

## 2.2 Sigma-Delta structures

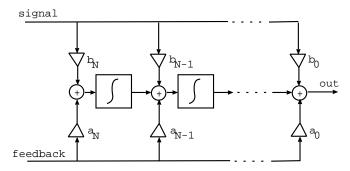

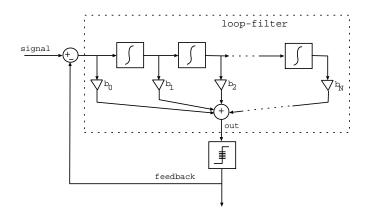

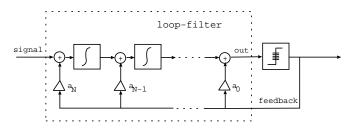

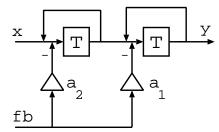

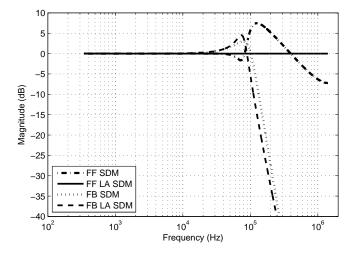

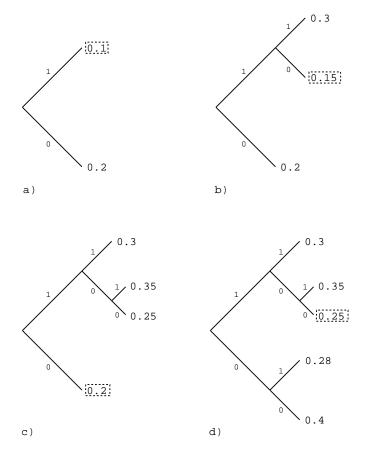

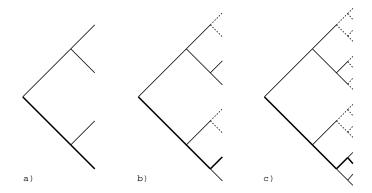

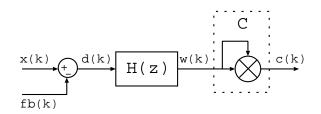

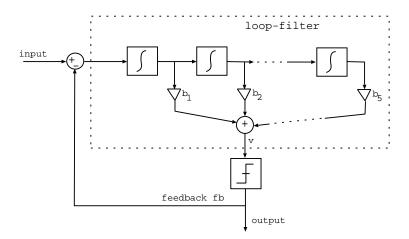

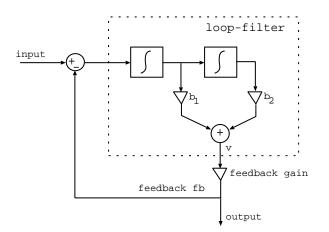

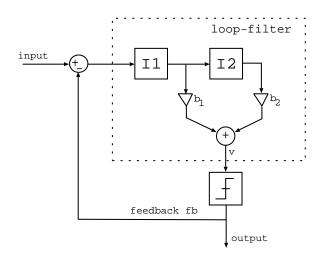

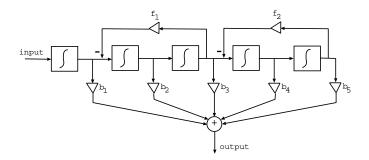

In sec. 2.1 it was shown that two basic SDM types exist, i.e. with an analog or a digital loop filter. In the case of an analog filter the combination of a quantizing ADC and a DAC is required for closing the noise-shaping loop and a decimation filter is present at the output. In the case of a digital filter no analog-digital domain boundary has to be crossed and only a digital quantizer is required, but at the input an upsample filter is present. When studying the noise-shaping properties of an SDM from a high-level perspective these analog-digital differences can be safely ignored and a generic model of the Sigma-Delta noise-shaping loop can be used instead. This generic model, consisting of a loop filter and a quantizer, is depicted in fig. 2.7. The loop filter has two inputs, one for the input signal and one for the quantizer feedback signal, where the transfer function for the two inputs can be complete independent in theory. In practice large parts of the loop-filter hardware will be shared between the two inputs. A practical loop-filter realization will consist of addition points, integrator sections, feed-forward coefficients  $b_i$  and feed-

Figure 2.7: Generic model of the Sigma-Delta noise-shaping loop, consisting of 2-input loop filter and quantizer.

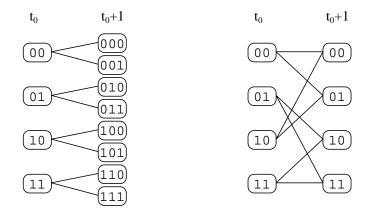

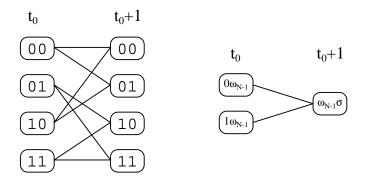

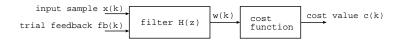

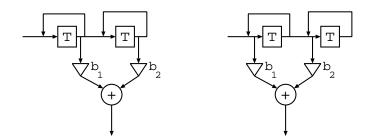

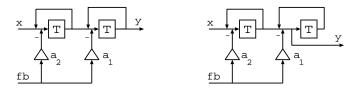

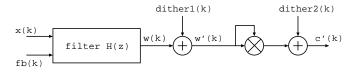

back coefficients  $a_i$  as shown in fig. 2.8. In this structure the number of